生成時鐘包括自動生成時鐘(又稱為自動衍生時鐘)和用戶生成時鐘。自動生成時鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列FPGA中的BUFGCE_DIV/BUFG_GT以及Versal中的MBUFG/BUFG_GT等。對于這類時鐘,Vivado會自動創(chuàng)建時鐘,并不需要用戶手工通過create_generated_clock創(chuàng)建。

案例1:單端時鐘

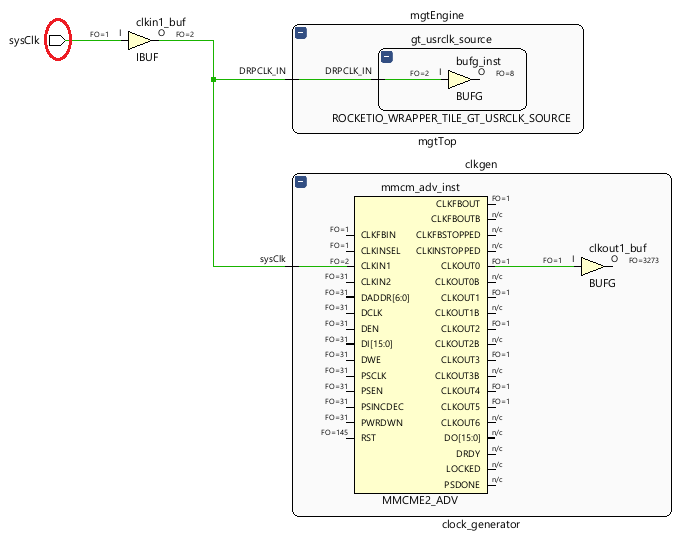

這是比較典型的場景,如下圖所示:時鐘由全局時鐘管腳進入經(jīng)IBUF驅(qū)動MMCM以及BUFG。此時只用在輸入時鐘管腳處(圖中紅色橢圓標(biāo)記)創(chuàng)建時鐘即可,MMCM生成時鐘如圖中端口CLKOUT0,Vivado會自動創(chuàng)建。注意主時鐘的位置在sysClk對應(yīng)的全局時鐘管腳處,不是MMCM的輸出端口,也不是BUFG的輸出端口。

案例2:差分時鐘

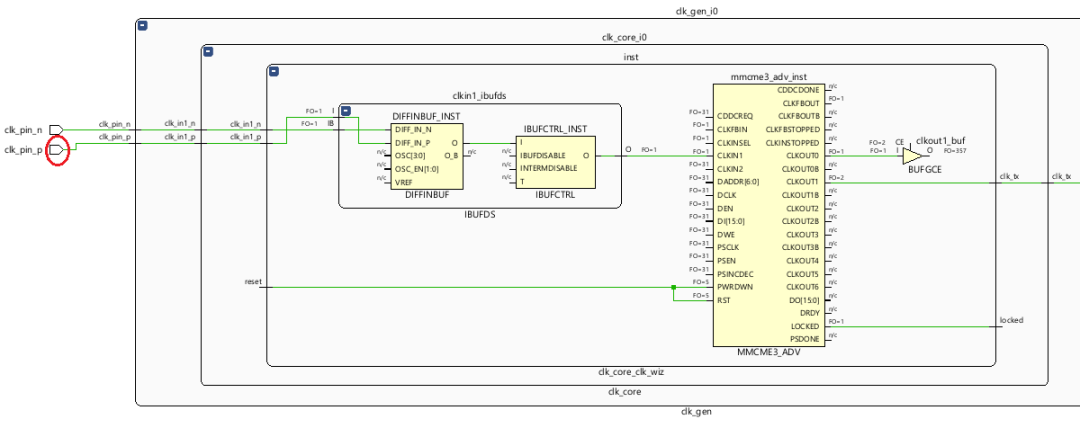

如下圖所示,差分時鐘轉(zhuǎn)單端驅(qū)動MMCM,這里主時鐘為clk_pin_p(圖中紅色方框所示),因此只用對該端口施加create_clock命令。

使用create_clock時,對于差分時鐘,施加對象為差分的P端而不是N端,同時只用對P端使用該命令,如下圖所示。

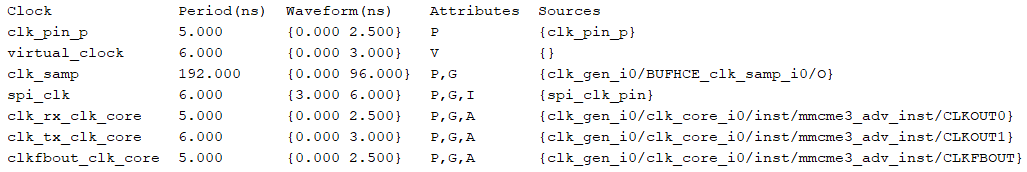

有了上述約束,工具就會自動推斷出MMCM生成時鐘,這可通過report_clocks命令查看并驗證,如下圖所示(需要打開綜合后的網(wǎng)表)。

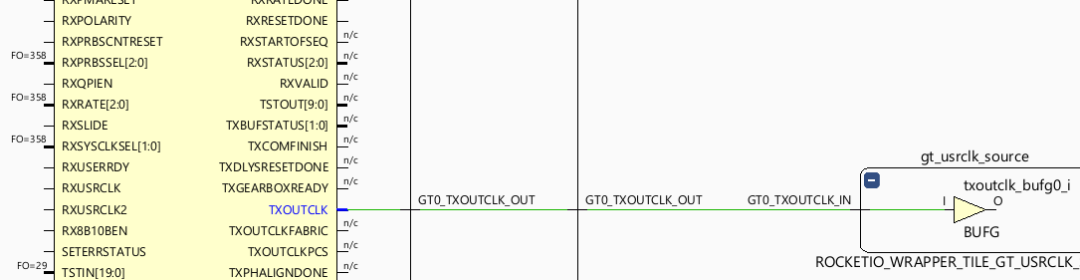

案例3:7系列FPGA中高速收發(fā)器的TXOUTCLK/RXOUTCLK

如下圖所示,7系列FPGA中高速收發(fā)器的TXOUTCLK,輸出端口接BUFG。這時要在TXOUTCLK處施加命令create_clock,因此,要用get_pins而不是get_ports。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614618 -

緩沖器

+關(guān)注

關(guān)注

6文章

2037瀏覽量

46698 -

時鐘

+關(guān)注

關(guān)注

11文章

1886瀏覽量

132894 -

輸出端口

+關(guān)注

關(guān)注

0文章

25瀏覽量

10278

原文標(biāo)題:create_clock你用對了嗎?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

請問AD9684中DCO時鐘的用法

請問AD9946中DCO時鐘的用法是?

怎么使用AD9946中DCO時鐘?

影響FPGA設(shè)計中時鐘因素的探討

DLL在FPGA時鐘設(shè)計中的應(yīng)用

大型設(shè)計中FPGA的多時鐘設(shè)計策略

基于FPGA的時鐘設(shè)計

FPGA異步時鐘設(shè)計中的同步策略

DLL在_FPGA時鐘設(shè)計中的應(yīng)用

關(guān)于FPGA中跨時鐘域的問題分析

時鐘在FPGA設(shè)計中能起到什么作用

FPGA架構(gòu)中的全局時鐘資源介紹

FPGA的時鐘電路結(jié)構(gòu)原理

FPGA中時鐘的用法

FPGA中時鐘的用法

評論