在PCB設計中,如何避免串擾?

在PCB設計中,避免串擾是至關重要的,因為串擾可能導致信號失真、噪聲干擾及功能故障等問題。

一、了解串擾及其原因

在開始討論避免串擾的方法之前,我們首先需要了解什么是串擾及其常見原因。串擾是指一個信號電路中的電流或電磁場對周圍其他電路產生干擾的現象。常見的原因包括電磁輻射、電磁感應、信號反射、互連線長度不匹配等。

二、正確的布局設計

1.分離敏感信號與噪聲源:盡量分離敏感信號線和噪聲源,使它們物理上保持足夠的距離。這可以減少噪聲來源對敏感信號的干擾。

2.地線規劃:合理規劃地線,保持地線的連續性和低阻抗。通過增加地面平面的面積,可以減少地線回路的自感和電阻。

3.隔離模擬和數字信號:模擬信號和數字信號的電路應該盡量分離放置,以減少彼此之間的串擾。如果不得不相互交叉布線,可以采用地隔離設備來隔離信號。

4.層次布局:盡量將不同類型的信號布置在不同的層次上。例如,模擬信號可以布置在底層,而數字信號可以布置在頂層。這種布局方式可以減少模擬和數字信號之間的耦合。

三、綜合考慮信號走線和電源線

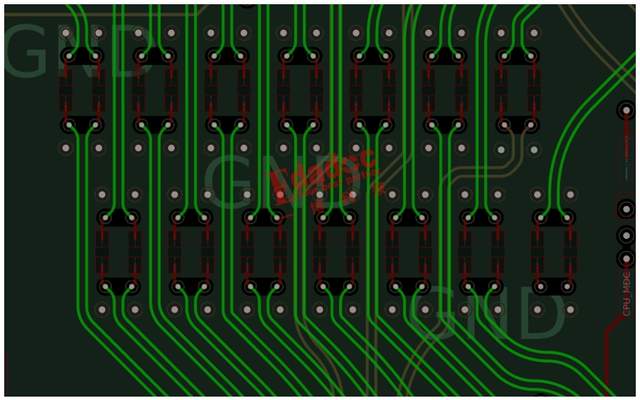

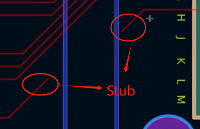

1.信號線走向:合理規劃信號線的走向,避免平行布線和交叉布線。如果信號線必須平行走線,可以通過增加地間隔或引入繞組間隔來減小串擾。

2.繞組間距:對于高頻信號線,應考慮增加繞組間的距離以減少串擾。較高的繞組間距可以降低電磁耦合,減少相鄰線路之間的互感。

3.電源線布線:電源線是一個常見的串擾源。在布線時,應盡量將電源線與其他敏感信號線隔離,并遠離高速信號線。

四、噪聲抑制技術

1.濾波器:在PCB上適當布置濾波器可以抑制一部分噪聲。例如,可采用電源線上的濾波電容來過濾高頻噪聲。

2.屏蔽:在設計中采用屏蔽材料或屏蔽罩可以有效地減少電磁輻射和感應,從而降低串擾。

3.電磁兼容性設計:在設計信號電路時,應該遵循電磁兼容性(EMC)原則,包括合理選用元器件、合理布局和阻抗匹配等。

五、仿真與調試

1.電磁場仿真:通過使用電磁場仿真軟件,可以在設計階段模擬和分析電磁場的分布情況,從而更好地了解并優化布局。

2.工程驗算:在PCB設計完成后,進行工程驗算是非常重要的。通過測量和分析實際電路的性能,可以識別并解決可能存在的串擾問題。

3.故障排除:如果在實際應用中發現了串擾問題,需要進行逐步的故障排除。可以通過排查布線、檢查接地情況、減少元器件布線長度等方法來消除或減小串擾。

結論

串擾是PCB設計中常見的問題,可能導致信號失真和噪聲干擾。為了避免串擾,我們需要在設計和布局階段充分考慮并采取適當的措施。合理的布局設計、信號線和電源線的走線規劃、噪聲抑制技術以及仿真和調試等方法都可以幫助我們避免串擾問題的發生。只有在實踐中不斷改進和優化,才能夠設計出高品質的PCB電路板。這些措施都是為了確保PCB電路板的正常運行并提高系統的可靠性。

-

PCB設計

+關注

關注

396文章

4815瀏覽量

90871 -

電磁兼容性

+關注

關注

6文章

471瀏覽量

34254 -

信號失真

+關注

關注

0文章

75瀏覽量

11675

發布評論請先 登錄

在PCB設計中,如何避免串擾?

在PCB設計中,如何避免串擾?

評論