在verilog中狀態(tài)機的一種很常用的邏輯結(jié)構(gòu),學(xué)習(xí)和理解狀態(tài)機的運行規(guī)律能夠幫助我們更好地書寫代碼,同時作為一種思想方法,在別的代碼設(shè)計中也會有所幫助。

一、簡介

在使用過程中我們常說的是有限狀態(tài)機(Finite-State Machine,F(xiàn)SM),簡稱為狀態(tài)機,表示在有限個狀態(tài)以及這些狀態(tài)之間的轉(zhuǎn)移和動作等行為的數(shù)學(xué)模型。

二、分類

在verilog中常使用的狀態(tài)機可以分為兩類,分別是Moore(摩爾)狀態(tài)機和Mealy(米利)狀態(tài)機。兩種狀態(tài)機的主要區(qū)別在于****Moore狀態(tài)機的輸出只與當(dāng)前狀態(tài)有關(guān),與當(dāng)前輸入無關(guān);Mealy狀態(tài)機的輸出不僅與當(dāng)前狀態(tài)有關(guān),還與當(dāng)前的輸入信號有關(guān) 。

三、設(shè)計實例

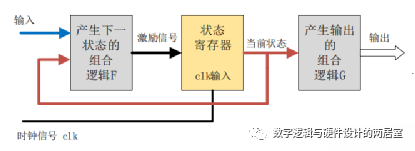

在狀態(tài)機設(shè)計的過程中推薦使用三段式設(shè)計,下面是三段式狀態(tài)機的基本結(jié)構(gòu):

(1)狀態(tài)機第一段,時序邏輯,非阻塞賦值,傳遞狀態(tài)機的狀態(tài) ;

(2)狀態(tài)機第二段,組合邏輯,阻塞賦值 ,根據(jù)當(dāng)前狀態(tài)和當(dāng)前輸入, 確定下一個狀態(tài)機的狀態(tài) ;

(3)狀態(tài)機第三段,時序邏輯,非阻塞賦值,確定輸出信號 。

下面介紹一個簡單的狀態(tài)機設(shè)計實例:一個學(xué)生,一周七天周一到周五需要上學(xué),單周周六鞏固復(fù)習(xí)這一周的知識,周日出去玩;雙周周六周日出去玩。可以得到狀態(tài)轉(zhuǎn)移圖如下:

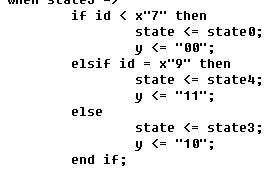

設(shè)計代碼如下:

`timescale 1ns / 1ps

?

module FSM(

input clk,

input rst_n,

input [2:0] week,

input odd_even,

output [1:0] activity

);

?

parameter learn = 2'd0;

parameter review= 2'd1;

parameter play = 2'd2;

?

reg [1:0] st_cur;

reg [1:0] st_next;

?

always @ (posedge clk or negedge rst_n)begin //Update the current status

if(!rst_n)begin

st_cur <= learn;

end

else begin

st_cur <= st_next;

end

end

?

always @(*)begin //Determine the next status

case(st_cur)

learn:

case(week)

3'd5: begin

if(odd_even)

st_next = review;

else

st_next = play;

end

3'd6:begin

st_next = play;

end

3'd7:begin

st_next = learn;

end

default:st_next = learn;

endcase

review: st_next = play;

play :

case(week)

3'd7: st_next = learn;

default: st_next = play;

endcase

default: st_next = st_next;

endcase

end

?

reg [1:0] activity_r;

?

always @(posedge clk or negedge rst_n)begin //Output signal

if(!rst_n)

activity_r <= 2'd0;

else

activity_r <= st_next;

end

?

assign activity = activity_r;

?

endmodule

仿真代碼如下:

`timescale 1ns / 1ps

?

module FSM_tb;

reg clk;

reg rst_n;

reg [2:0] week;

reg odd_even;

wire [1:0] activity;

initial begin

clk <= 1'b0;

rst_n <= 1'b0;

odd_even <= 1'b0;

week <= 3'd1;

#10

rst_n <= 1'b1;

end

always #10

clk = ~clk;

always @(posedge clk)begin

week <= week + 3'd1;

if(week == 3'd7)begin

odd_even <= ~odd_even;

week <= 3'd1;

end

end

?

FSM fsm_inst(

.clk(clk),

.rst_n(rst_n),

.week(week),

.odd_even(odd_even),

.activity(activity)

);

endmodule

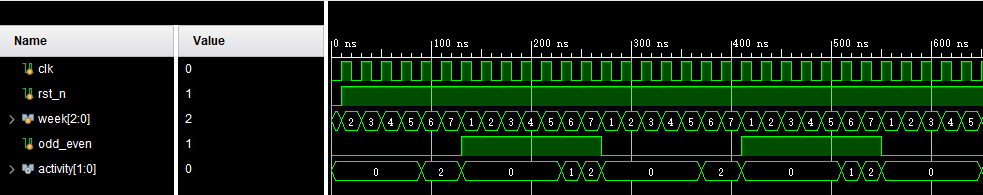

仿真結(jié)果如下圖所示:

對狀態(tài)機的理解需要大量的實際操作,孰能生巧,在我學(xué)習(xí)的過程中老師曾要求我們用狀態(tài)機寫 萬年歷 ,對于感興趣的同學(xué)來說也可以進行嘗試。

-

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111978 -

狀態(tài)機

+關(guān)注

關(guān)注

2文章

493瀏覽量

28112

發(fā)布評論請先 登錄

狀態(tài)機編程實例-狀態(tài)表法

狀態(tài)機編程實例-面向?qū)ο蟮?b class='flag-5'>狀態(tài)設(shè)計模式

verilog狀態(tài)機問題

狀態(tài)機舉例

基于有限狀態(tài)機的工控系統(tǒng)軟件設(shè)計

有限狀態(tài)機的建模與優(yōu)化設(shè)計

使用verilog HDL實現(xiàn)狀態(tài)機8位流水燈的程序和工程文件免費下載

Verilog設(shè)計過程中狀態(tài)機的設(shè)計方法

Verilog狀態(tài)機的類型

Verilog狀態(tài)機+設(shè)計實例

Verilog狀態(tài)機+設(shè)計實例

評論