數(shù)字減法器電路的性能指標

目前,針對數(shù)字電路研究的主要目標都是為了提高電路的運算速度、降低電路的功耗和減少電路邏輯輸出的誤差,因此延時、功耗和誤差是數(shù)字電路三個最重要的性能指標。

運算速度指標——延時

數(shù)字電路的延時主要是指信號的傳輸延時,電路的延時與邏輯門的工藝設計相關,延時限制了電路的工作速度,所以對電路的延時優(yōu)化一直是很多學者研究的熱點。全減器模塊作為最基本的電路組成部件,整個電路的延時取決于全減器模塊的延時,因此,對全減器模塊延時的優(yōu)化工作顯得尤為重要。

對于全減器來說,延時優(yōu)化主要方法是減小信號在關鍵路徑上的延時;對于串行進位減法器電路來說,關鍵路徑就是指信號進位位支路(也就是對電路中所有的輸入來說,信號延時時間最大時的情形),減小進位位支路的延時時間,對于提高串行進位減法器電路運算速度具有重要意義。

近年來,隨著電路低功耗設計的要求,電源電壓隨之降低,而電源電壓的降低又會增大電路中信號的傳輸延時時間,從而影響電路的邏輯輸出結(jié)果。尤其是在時鐘周期固定的同步電路中,如何保證電路正確的邏輯輸出結(jié)果,實現(xiàn)電路的可靠性設計和最大限度的降低功耗是當前電路設計研究的主要課題。

能量消耗指標——功耗

CMOS 電路中功耗由兩部分組成:動態(tài)功耗、靜態(tài)功耗。動態(tài)功耗主要是由 CMOS 電路中邏輯門工作過程中負載電容充放電時引起的功耗,主要包括翻轉(zhuǎn)功耗(翻轉(zhuǎn)指的是電路中信號 0→1 或 1→0 的變換)和短路功耗。

翻轉(zhuǎn)功耗是數(shù)字電路要完成邏輯功能計算所必須要消耗的功耗,也稱有效功耗;短路功耗是由于 CMOS 在翻轉(zhuǎn)過程中 PMOS 管和 NMOS 管同時導通時所消耗的功耗,也稱無效功耗;靜態(tài)功耗是由于漏電電流引起的功耗。

通常靜態(tài)功耗與電路中的器件相關,在電路設計過程中,如何降低整體的電路功耗已成為當今電路研究者與設計者十分關注的問題,特別是要考慮到如何降低電路的動態(tài)功耗。

可靠性指標——誤差

在同步電路中,由于時鐘周期的存在,一旦電路總的延時時間超過了時鐘周期,那么在時鐘周期內(nèi)我們采樣得到的電路輸出結(jié)果與理論上電路正確的邏輯輸出結(jié)果不同,此時電路實際上輸出的是錯誤的結(jié)果。

因此,如何保證電路最終的輸出結(jié)果是正確的,最大限度的減小誤差也是目前電路研究的一個熱點方向。

兩位格雷碼減法器數(shù)字電路設計

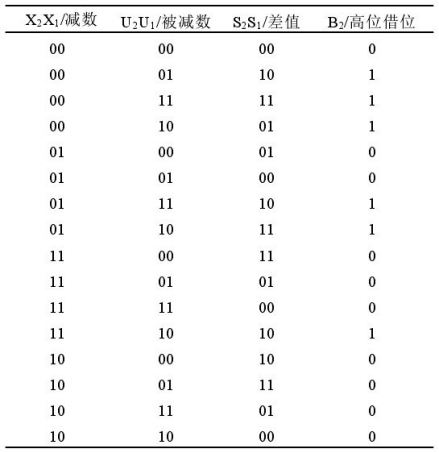

兩位減法器的格雷碼(Gray code)真值表如圖13所示,可以實現(xiàn)兩個兩位二進制數(shù)之間的減法算術運算。從真值表中可以得知,存在 16 種不同的邏輯運算。

如表 4-1 所示,X2X1****和 U2U1 分別代表減數(shù)和被減數(shù),S2S1 代表兩個兩位二進制數(shù)之間的差值,B2代表來自高位的借位。在圖13中,減數(shù)、被減數(shù)和差值都通過使用格雷碼來表示,格雷碼可以轉(zhuǎn)換成二進制碼(8421 碼),即從左邊的第二位開始,在每個位和左邊的解碼值之間獲得異或操作的值作為該位的解碼值,最左邊的值保持不變。

圖13 兩位減法器操作運算的真值表

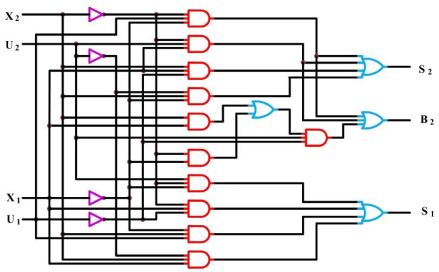

根據(jù)兩位格雷碼減法器的真值表,列寫其布爾邏輯表達式,依據(jù)其布爾表達式,構(gòu)造相應的數(shù)字電路原理圖,如圖14所示,有三種基本的邏輯門,即非門、與門、或門,不同的邏輯門使用不同的顏色標記,使用紫羅蘭色標記非門,紅色標記與門,天藍色標記或門,圖14中共存在 4 個非門,11 個與門,4 個或門。

圖14 兩位格雷碼減法器原理圖

-

邏輯門

+關注

關注

1文章

142瀏覽量

24857 -

二進制

+關注

關注

2文章

805瀏覽量

42185 -

格雷碼

+關注

關注

2文章

34瀏覽量

13371 -

減法器

+關注

關注

1文章

26瀏覽量

17062 -

CMOS電路

+關注

關注

0文章

49瀏覽量

11788

發(fā)布評論請先 登錄

數(shù)字電路中加法器和減法器邏輯圖分析

兩位格雷碼減法器數(shù)字電路設計

兩位格雷碼減法器數(shù)字電路設計

評論