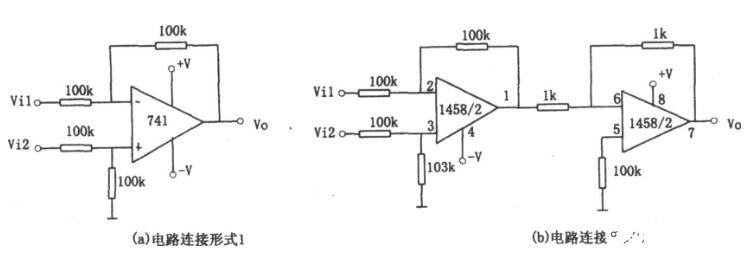

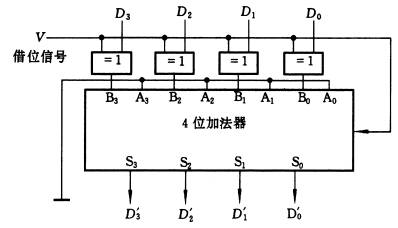

減法器電路

一個通常的應用就是用于去除立體聲磁帶中的原唱而留下伴音(在錄制時兩通道中的原唱電平是一樣的,但是伴音是略有不同的)。

電子發燒友App

電子發燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網>電子技術應用>電子技術>電路圖>電工基礎電路圖>減法器電路

相關推薦

1336

1336

372

372

3722

3722

453

453

5873

5873 36625

36625

37

37 11504

11504 42334

42334

4

4 157219

157219

5077

5077 14405

14405 74

74 12577

12577

評論