來源:IMEC

Cu/SiCN鍵合技術的創新是由邏輯存儲器堆疊需求驅動的

晶圓到晶圓混合鍵合的前景

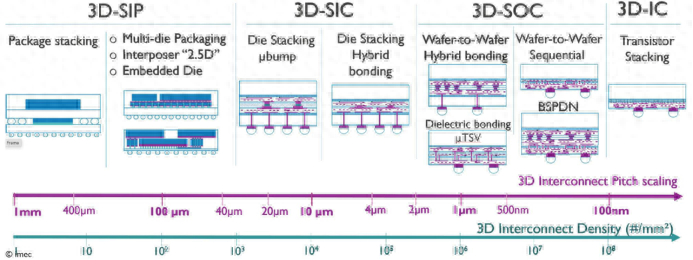

3D集成是實現多芯片異構集成解決方案的關鍵技術,是業界對系統級更高功耗、性能、面積和成本收益需求的回應。3D堆疊正在電子系統層次結構的不同級別(從封裝級到晶體管級)引入。因此,多年來已經開發出多種3D互連技術,涵蓋各種互連間距(從毫米到小于100納米)并滿足不同的應用需求。這種“3D互連前景”如下圖所示。該前景是高度動態的,每種技術都會及時擴展到更小的互連間距。在該技術“譜系”接近尾聲時,我們發現了晶圓到晶圓混合鍵合,有望實現高互連密度和小互連寄生效應。這種“混合”(銅到銅和電介質到電介質)鍵合技術使用銅鑲嵌技術來定義鍵合表面,可能允許非常精細的間距縮放。

圖1:imec 3D互連技術前景

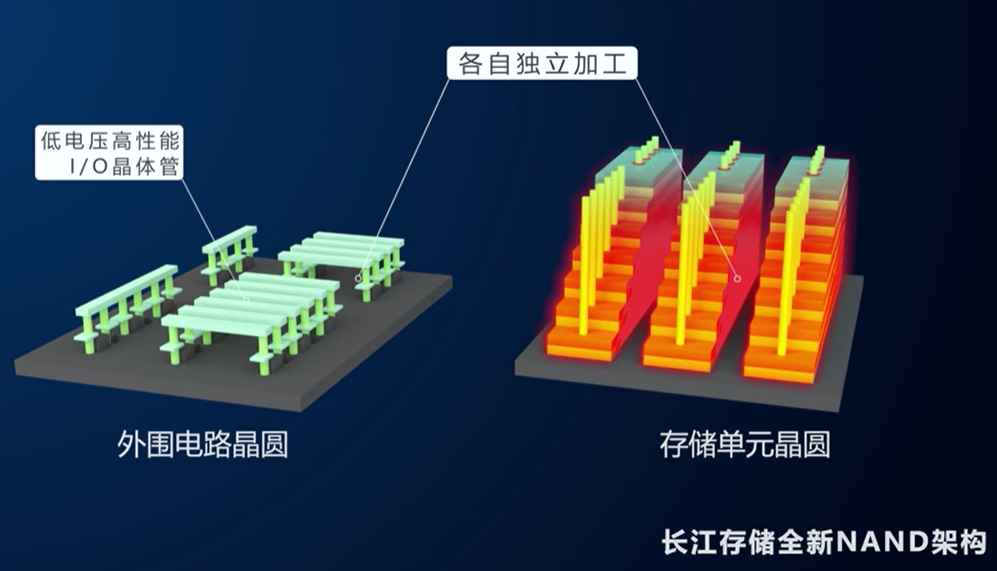

直到最近,晶圓到晶圓混合鍵合的大批量制造主要局限于信號處理電路層上的堆疊圖像傳感器領域。最近,該技術被用于在3D NAND層之上集成CMOS外圍電路。這些商業應用利用了該技術每平方毫米集成一百萬個互連的能力,這是通過約1μm的緊密銅互連間距實現的。該技術的另一個優點是可以“混合搭配”不同的材料和功能以及不同代的CMOS技術。

在未來的幾年里,我們預計應用領域將大幅度擴大。借助系統技術協同優化 (STCO),考慮到電路塊甚至標準單元,電路分區將發生在設計層次結構的更低級別。我們看到了邏輯存儲器應用的首次發布——例如邏輯之上的SRAM——這一直是開發先進晶圓到晶圓混合鍵合技術的主要驅動力之一。為了在這些情況下充分發揮晶圓到晶圓混合鍵合的潛力,研究人員必須成功地將互連間距縮小到遠低于1μm。

當前晶圓到晶圓混合鍵合的工藝流程

當今的晶圓到晶圓混合鍵合工藝流程從兩個經過完全處理的300mm晶圓開始,具有完整的前端生產線 (FEOL) 和后端生產線 (BEOL)。該流程的第一部分類似于片上BEOL鑲嵌工藝,其中在鍵合電介質中蝕刻出小空腔 - 主要使用 SiO2。空腔填充有阻擋金屬、晶種和銅。接下來是化學機械拋光 (CMP) 步驟,該步驟針對晶圓間的高均勻性進行了優化,以產生極其平坦的電介質表面,同時為銅焊盤實現幾納米的凹槽。精確對準后,通過使晶圓在晶圓中心接觸,在室溫下進行兩個晶圓的實際接合。拋光的晶圓表面粘附會產生強大的晶圓間吸引力,從而產生鍵合波,進而封閉從中心到邊緣的晶圓到晶圓的間隙。在室溫鍵合步驟之后,晶片在更高的溫度下退火以獲得永久的電介質-電介質和銅-銅鍵合。

新興應用挑戰當前工藝步驟

隨著應用領域的擴展,更先進的混合鍵合實現不斷涌現。如前所述,目前的趨勢是使鍵合工藝越來越靠近前端,以實現邏輯疊邏輯或存儲器邏輯疊層等功能。這不僅需要更精細的互連間距,而且還需要在鍵合步驟之后進行更多的后處理。

一個非常具體的例子是背面供電網絡 (BSPDN),其中晶圓到晶圓鍵合是關鍵步驟。在 BSPDN 處理中,第一個晶圓的正面被鍵合到載體晶圓上。然后減薄第一片晶圓的背面,并通過 n-TSV 圖案化、金屬填充和背面金屬化完成該工藝。在此示例中,BEOL處理的一部分(即集成用于電力傳輸的“最寬”互連線)是在晶圓鍵合工藝之后進行的。

這些應用提出了更嚴格的擴展需求,對當前的工藝流程提出了挑戰。主要缺陷涉及銅到銅的對準精度、鍵合前的晶圓純度和拓撲結構,以及小互連間距下電介質和銅焊盤的鍵合強度。

改進晶圓到晶圓混合鍵合工藝,實現400nm間距互連

在2023年IEEE國際電子設備會議 (IEDM 2023) 上,imec報告了一些重要創新,這些創新為前所未有的400nm互連間距鋪平了道路。這項工作是一項綜合研究的結果,該研究檢查了晶圓到晶圓混合鍵合的各個方面[1]。

改進設計以補償縮放和對齊限制

Imec研究人員首次提出了一種采用六邊形網格和圓形銅焊盤的測試樣品設計,而不是傳統的方形網格和方形或圓形焊盤設計。新設計具有多項優點。它允許銅焊盤以盡可能最密集的方式封裝,所有相鄰焊盤之間的距離相等。因此,隨著進一步縮放,這種配置更容易控制銅焊盤密度,同時最大化銅焊盤尺寸和間距。該團隊還在研究使用相等或不相等焊盤設計的影響。在后一種情況下,頂部晶圓的臨界銅焊盤尺寸設計得比底部晶圓更小。不相等焊盤設計也具有一些優點,包括更大的鍵合重疊公差、更低的寄生電容以及在小互連間距下更高的介電擊穿強度。

精確控制表面形貌

在兩個晶圓鍵合之前,兩個晶圓的表面必須極其平滑和清潔,以實現可靠的混合鍵合工藝。因此,CMP是一個要求非常高的工藝步驟。它還確保銅焊盤的均勻凹進,這意味著銅在鍵合之前保留在介電表面下方幾納米處。這是在退火后獲得無空隙接合所必需的。通過在布局設計中將先進的CMP工藝與虛擬焊盤相結合,研究人員成功地精確控制了整個晶圓上的銅焊盤高度和表面拓撲。

SiCN電介質具有更好的粘合強度和可擴展性

Imec此前提出SiCN作為小互連間距的首選電介質。與SiO2表面相比,SiCN表面表現出更高的鍵合能,這意味著需要更多的能量來破壞鍵合。此外,SiCN還可作為Cu和晶圓鈍化層的擴散阻擋層,阻止氣體擴散,從而形成熱穩定性更高的鍵合界面。當縮小混合鍵合互連間距時,這些特性變得越來越重要。基于納米壓痕(一種評估粘合強度的新興技術)的測量證實,SiCN-SiCN粘合強度明顯優于SiO2-SiO2粘合強度。只需250°C的鍵合后退火即可獲得高鍵合強度,并且在更高溫度下不會降低。

400nm間距互連,具有出色的電氣性能

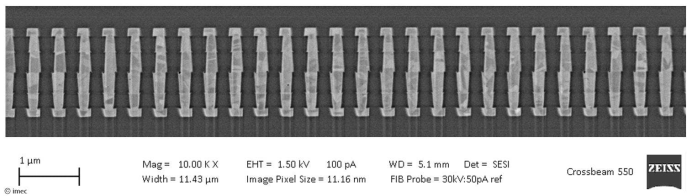

上述見解用于執行先進的晶圓到晶圓Cu/SiCN鍵合工藝。實際的鍵合是使用配備先進對準功能的商業高質量晶圓鍵合機進行的,這是該工藝成功的關鍵工具。300毫米晶圓成功鍵合,產生了前所未有的400納米間距的銅互連。

圖2:TEM圖像顯示了以400 nm間距連接的多個銅焊盤(相等焊盤設計)。

圖3:放大相等焊盤設計中的400nm節距長鏈,用于評估 Cu-Cu連接性(如 IEDM 2023 上所示)。

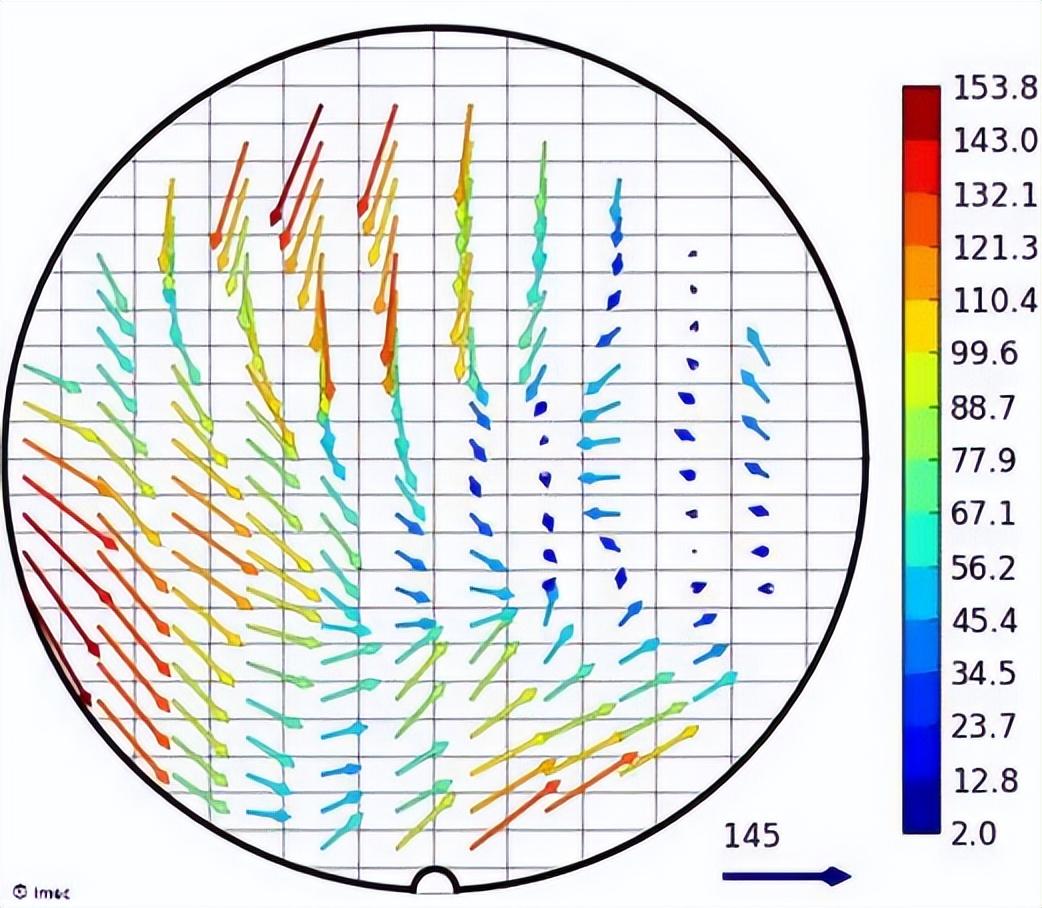

結果表明,成功控制了Cu/SiCN表面形貌、精確對準(導致覆蓋層低于150nm)以及良好的電氣性能(即低單接觸電阻)。

圖4:150nm以下的晶圓間鍵合覆蓋(如 IEDM 2023 上所示)。

需要<100nm覆蓋控制

該團隊還首次研究了鍵合覆蓋層與可靠性(即電介質擊穿和良率)之間的關系。結果證實,在小互連間距下,不均勻設計的銅焊盤比相等的焊盤具有更高的介電擊穿強度。該團隊還得出結論,對于這些400nm互連間距,覆蓋控制需要小于100nm,才能在大批量制造中獲得足夠的良率。因此,滿足未來3D-SOC設計的需求對下一代晶圓鍵合設備的疊合精度提出了嚴格的要求。

結論

晶圓到晶圓混合鍵合已成為一種很有前景的3D集成技術,可實現不斷增加的I/O密度以及功能芯片之間更高效的連接。為了實現邏輯存儲器等應用(其中晶圓到晶圓鍵合發生在靠近前端的位置),必須將銅互連間距的縮放推至其最終極限。網格設計的改進、表面形貌的增強控制、SiCN作為電介質的使用、對鍵合機制的基本理解以及改進的覆蓋控制被認為是在400nm(及以下)間距下實現電氣功能和可靠的Cu互連的關鍵推動因素。這些結果為開發未來具有更小互連間距的晶圓到晶圓鍵合工藝奠定了基礎。

本文最初發表于《Nature Review Electrical Engineering》。

審核編輯 黃宇

-

晶圓

+關注

關注

52文章

5130瀏覽量

129280 -

鍵合

+關注

關注

0文章

78瀏覽量

8067

發布評論請先 登錄

晶圓到晶圓混合鍵合:將互連間距突破400納米

晶圓到晶圓混合鍵合:將互連間距突破400納米

評論