來源:IMEC

設(shè)計探路PDK降低了學術(shù)界和工業(yè)界接觸最先進半導體技術(shù)的門檻

在2024年IEEE國際固態(tài)電路會議 (ISSCC) 上,世界領(lǐng)先的納米電子和數(shù)字技術(shù)研究與創(chuàng)新中心imec推出了其開放式工藝設(shè)計套件 (PDK),并通過EUROPRACTICE提供的相應培訓計劃 。PDK將支持IMEC N2技術(shù)中的虛擬數(shù)字設(shè)計,包括背面供電網(wǎng)絡。PDK將嵌入EDA工具套件中,例如來自Cadence Design Systems和Synopsys的工具套件,為設(shè)計探路、系統(tǒng)研究和培訓提供對廣泛的高級節(jié)點訪問。這將為學術(shù)界和工業(yè)界提供培訓未來半導體專家的工具,并使工業(yè)界能夠通過有意義的設(shè)計探路將其產(chǎn)品轉(zhuǎn)變?yōu)橄乱淮夹g(shù)。

晶圓代工PDK使芯片設(shè)計人員能夠訪問經(jīng)過測試和驗證的組件庫,以提供功能齊全且可靠的設(shè)計。一旦技術(shù)達到可制造性的關(guān)鍵水平,這些通常就可供生態(tài)系統(tǒng)使用。然而,準入限制和保密協(xié)議的需要為學術(shù)界和工業(yè)界在開發(fā)過程中獲取先進技術(shù)節(jié)點設(shè)置了很高的門檻。使用imec N2 PDK將有助于學術(shù)界和商業(yè)公司。” Logic Technologies副總裁Julien Ryckaert 說道:“如果我們想吸引新一代芯片設(shè)計人員,我們必須讓他們盡早接觸到在最先進技術(shù)節(jié)點上發(fā)展設(shè)計技能所需的基礎(chǔ)設(shè)施。隨附的培訓課程將使這些設(shè)計人員盡快掌握最新技術(shù),例如納米片器件和晶圓背面技術(shù)。設(shè)計探路PDK還將幫助公司將其設(shè)計過渡到未來的技術(shù)節(jié)點,并預防其產(chǎn)品的擴展瓶頸。

設(shè)計探路PDK包含基于一組數(shù)字標準單元庫和SRAM IP宏的數(shù)字設(shè)計所需的基礎(chǔ)設(shè)施。未來,設(shè)計探路PDK平臺將擴展到更高級的節(jié)點(例如A14)。該培訓計劃將于第二季度初開始,告知訂閱者N2技術(shù)節(jié)點的特性,并提供使用Cadence和Synopsys EDA軟件的數(shù)字設(shè)計平臺的實踐培訓。

Synopsys技術(shù)戰(zhàn)略與戰(zhàn)略合作伙伴副總裁Brandon Wang表示:“培養(yǎng)一支具備開發(fā)轉(zhuǎn)型產(chǎn)品所需技術(shù)的工程人員隊伍對于半導體行業(yè)至關(guān)重要。Imec的設(shè)計探路PDK是一個很好的例子,展現(xiàn)了行業(yè)合作伙伴關(guān)系為當前和下一代設(shè)計師拓寬先進工藝技術(shù)獲取途徑的方法,從而加速他們的半導體創(chuàng)新。我們與imec合作為其N2 PDK提供經(jīng)過認證的、人工智能驅(qū)動的EDA數(shù)字設(shè)計工藝,使設(shè)計團隊能夠使用基于PDK的虛擬設(shè)計環(huán)境進行原型設(shè)計并加速向下一代技術(shù)的過渡。”

Cadence學術(shù)網(wǎng)絡副總裁Yoon Kim表示:“Cadence致力于與大學和研究機構(gòu)合作,推動創(chuàng)新并支持納米和微電子行業(yè)的勞動力發(fā)展。Cadence和imec在多個項目上有著長期的成功合作,新的imec設(shè)計探路PDK代表了培訓下一代芯片設(shè)計人員的一個重要的新里程碑。Imec使用Cadence業(yè)界領(lǐng)先的AI驅(qū)動的數(shù)字和自定義/模擬全工藝中的所有工具來創(chuàng)建和驗證Open PDK,確保學術(shù)界和行業(yè)合作伙伴能夠在最先進的節(jié)點訪問完整的Cadence流程,使他們能夠無縫地過渡到下一代設(shè)計。”

設(shè)計探路PDK允許采用2nm環(huán)繞柵極(GAA)技術(shù)(包括背面連接)進行數(shù)字設(shè)計。

審核編輯 黃宇

-

半導體

+關(guān)注

關(guān)注

335文章

28723瀏覽量

234574 -

IMEC

+關(guān)注

關(guān)注

0文章

59瀏覽量

22525

發(fā)布評論請先 登錄

下一代高速芯片晶體管解制造問題解決了!

贛鋒鋰電推出首款10MWh儲能集裝箱系統(tǒng)解決方案

Cadence攜手臺積公司,推出經(jīng)過其A16和N2P工藝技術(shù)認證的設(shè)計解決方案,推動 AI 和 3D-IC芯片設(shè)計發(fā)展

AMD實現(xiàn)首個基于臺積電N2制程的硅片里程碑

比亞迪推出首款插電式混合動力車型BYD SHARK

2025年分布式光伏大變革:430與531節(jié)點后,行業(yè)如何破局掘金?

英特爾18A與臺積電N2工藝各有千秋

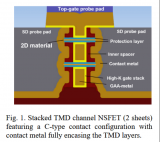

IEDM 2024先進工藝探討(三):2D材料技術(shù)的進展及所遇挑戰(zhàn)

Imec等推出無鉛量子點SWIR傳感器

臺積電分享 2nm 工藝深入細節(jié):功耗降低 35% 或性能提升15%!

時間復雜度為 O(n^2) 的排序算法

OFFSET N1和N2這兩個引腳不是都是兩個輸入性質(zhì)的引腳嗎?為什么會有固定的-12V輸出呢?

imec實現(xiàn)硅基量子點創(chuàng)紀錄低電荷噪聲

SF6 N2混合氣體回收分離設(shè)備的操作順序——每日了解電力知識

Imec推出首款針對N2節(jié)點的設(shè)計探路工藝設(shè)計套件

Imec推出首款針對N2節(jié)點的設(shè)計探路工藝設(shè)計套件

評論