Verilog是一種硬件描述語言,用于描述數(shù)字電路的行為和結(jié)構(gòu)。與其他編程語言相比,Verilog具有與硬件緊密結(jié)合的特點(diǎn),因此其接口機(jī)制也有一些與眾不同之處。本文將詳細(xì)介紹Verilog與其他編程語言的接口機(jī)制,并深入探討其原理和應(yīng)用。

- Verilog語言概述

Verilog是由美國專業(yè)電子設(shè)計(jì)自動化公司Cadence設(shè)計(jì)系統(tǒng)有限公司(前身是Gateway Design Automation公司)開發(fā)的一種硬件描述語言。它是一種結(jié)構(gòu)化,靜態(tài)和類型安全的編程語言,具有強(qiáng)大的硬件描述能力。

Verilog的主要特點(diǎn)是:

- 用于描述數(shù)字電路的行為和結(jié)構(gòu)。

- 具有豐富的模塊化和層次化設(shè)計(jì)特性。

- 支持并發(fā)處理和事件驅(qū)動模擬。

- 提供了三種抽象級別:結(jié)構(gòu)級、行為級和寄存器傳輸級。

- Verilog的接口機(jī)制

Verilog的接口機(jī)制類似于其他編程語言中的函數(shù)和過程調(diào)用機(jī)制。它用于定義模塊的輸入和輸出端口以及它們之間的連接關(guān)系。

在Verilog中,接口是一種數(shù)據(jù)類型,它定義了模塊內(nèi)外之間的數(shù)據(jù)通信協(xié)議。接口可以包含多個信號或端口,用于表示模塊與其他模塊或外部設(shè)備之間的通信通道。

接口的定義使用interface關(guān)鍵字,例如:

interface my_interface;

logic clk, rst, data_in;

logic [7:0] data_out;

endinterface

接口中的信號可以是各種類型,例如logic、wire、reg等。它們可以是單個信號或多個信號的數(shù)組。此外,接口還可以包含任務(wù)和函數(shù)等成員。

- Verilog接口與模塊之間的連接

在Verilog中,接口與模塊之間通過端口進(jìn)行連接。端口是模塊與外部環(huán)境之間的通信通道,其類型必須與接口定義中的信號類型一致。

端口的聲明使用input、output和inout等關(guān)鍵字,例如:

module my_module(input clk, rst, data_in, output [7:0] data_out);

// 模塊內(nèi)部的邏輯實(shí)現(xiàn)

endmodule

模塊內(nèi)部的邏輯通過連接接口的端口進(jìn)行數(shù)據(jù)傳輸。通過端口的連接,可以將一個模塊的輸入端口與另一個模塊的輸出端口相連,實(shí)現(xiàn)不同模塊之間的數(shù)據(jù)傳遞。

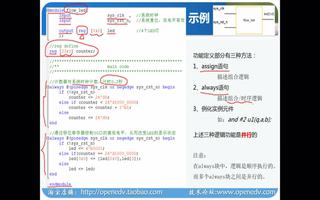

例如,從一個模塊的輸出端口向另一個模塊的輸入端口傳遞數(shù)據(jù),可以使用assign語句進(jìn)行連接,例如:

assign data_in = data_out;

通過端口連接,Verilog可以將多個模塊組合在一起,形成更大的功能單元,實(shí)現(xiàn)復(fù)雜的數(shù)字電路。

- Verilog接口與其他編程語言的接口機(jī)制的比較

與其他編程語言相比,Verilog的接口機(jī)制更加底層和直接,更適合于描述硬件的行為和結(jié)構(gòu)。

- 類型系統(tǒng):與其他編程語言相比,Verilog的類型系統(tǒng)更簡單,只有少數(shù)幾種類型可以用于描述硬件的行為和結(jié)構(gòu),例如

logic、wire、reg等。與其他編程語言相比,Verilog中的類型沒有額外的內(nèi)置方法和操作符。 - 并發(fā)性:Verilog具有天生的并發(fā)性,允許多個邏輯過程同時執(zhí)行。這與傳統(tǒng)的順序編程語言不同,需要通過多線程或多進(jìn)程機(jī)制才能實(shí)現(xiàn)并發(fā)執(zhí)行。

- 事件驅(qū)動模擬:Verilog中的模擬是事件驅(qū)動的,只有在事件發(fā)生時才執(zhí)行相應(yīng)的模擬代碼。這與其他編程語言中的循環(huán)或逐行執(zhí)行不同,使得Verilog更高效和逼真地模擬硬件的行為。

- 時序表示:與其他編程語言相比,Verilog中的時序表示更加直觀和自然。它使用

always塊來表示時鐘觸發(fā)的事件,使得時鐘和狀態(tài)的轉(zhuǎn)換更容易描述。 - 硬件描述能力:Verilog具有強(qiáng)大的硬件描述能力,可以精確地描述硬件的行為和結(jié)構(gòu)。與其他編程語言相比,Verilog更適合于描述數(shù)字電路,而不是一般的軟件應(yīng)用。

綜上所述,Verilog與其他編程語言的接口機(jī)制在一些方面有所不同。Verilog更加底層和直接,適用于描述硬件的行為和結(jié)構(gòu)。通過端口的連接,Verilog可以將多個模塊組合在一起,實(shí)現(xiàn)復(fù)雜的數(shù)字電路。

-

接口

+關(guān)注

關(guān)注

33文章

8971瀏覽量

153472 -

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

112062 -

編程語言

+關(guān)注

關(guān)注

10文章

1955瀏覽量

36401 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1638瀏覽量

81763

發(fā)布評論請先 登錄

數(shù)字電路設(shè)計(jì)中的一款強(qiáng)大工具—Verilog編程語言介紹

Python與其他編程語言有何不同?

基于Verilog HDL語言的FPGA設(shè)計(jì)

LabVIEW與其他應(yīng)用程序的接口設(shè)計(jì)

Verilog HDL語言在FPGA/CPLD開發(fā)中的應(yīng)用

什么是LabVIEW?LabVIEW與其他編程語言有什么差異?有什么優(yōu)勢?

正點(diǎn)原子開拓者FPGA:Verilog程序框架

verilog學(xué)習(xí)要點(diǎn)

Verilog編程語言界面入門知識簡介

Verilog是編程語言嗎

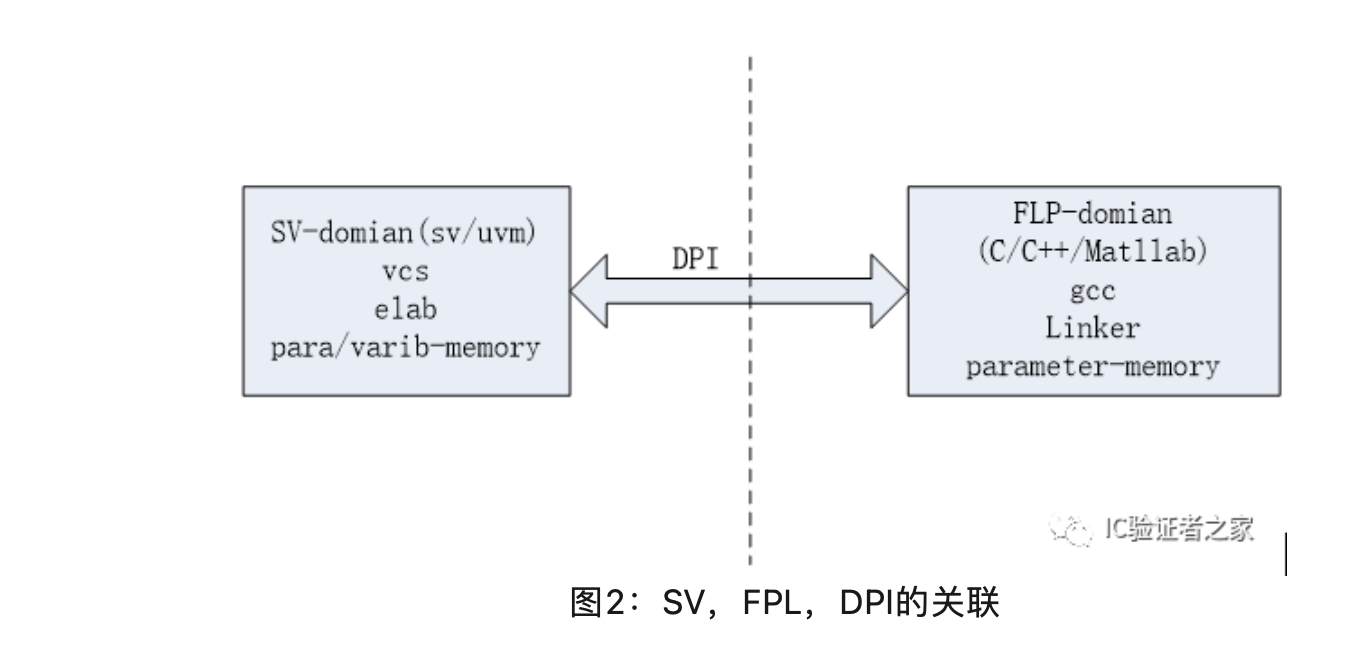

淺談System Verilog的DPI機(jī)制

verilog與其他編程語言的接口機(jī)制

verilog與其他編程語言的接口機(jī)制

評論