什么是Verilog HDL?

Verilog HDL (Hardware Description Language) 是一種硬件描述語(yǔ)言,可以在算法級(jí)、門級(jí)到開關(guān)級(jí)的多種抽象設(shè)計(jì)層次上對(duì)數(shù)字系統(tǒng)建模。它可以描述設(shè)計(jì)的行為特性、數(shù)據(jù)流特性、結(jié)構(gòu)組成以及包含響應(yīng)監(jiān)控和設(shè)計(jì)驗(yàn)證方面的時(shí)延和波形產(chǎn)生機(jī)制。此外,verilog提供了編程語(yǔ)言接口,通過(guò)該接口用戶可以在模擬、驗(yàn)證期間從外部訪問(wèn)設(shè)計(jì),包括模擬的具體控制和運(yùn)行。

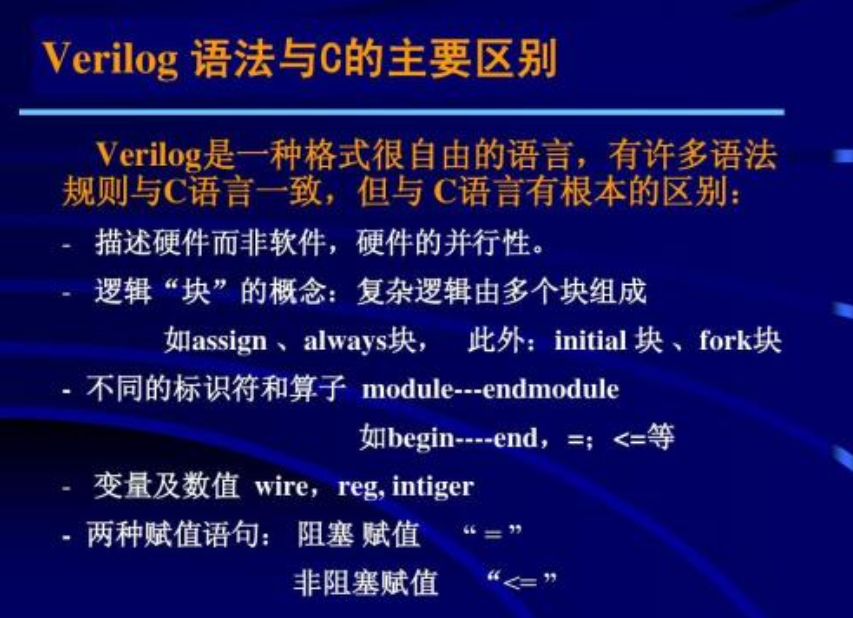

Verilog 不僅定義了語(yǔ)法,而且對(duì)每個(gè)語(yǔ)法結(jié)構(gòu)都定義了清晰的模擬、仿真語(yǔ)義。因此,用這種語(yǔ)言編寫的模型能夠使用 Verilog 仿真器進(jìn)行驗(yàn)證。Verilog 從C語(yǔ)言中繼承了多種操作符和結(jié)構(gòu),所以從結(jié)構(gòu)上看兩者有很多相似之處。

Verilog HDL是你在開發(fā) FPGA 、ASIC 時(shí)使用的語(yǔ)言,跟開發(fā)軟件使用 C語(yǔ)言一個(gè)道理。

Verilog是一種思維方式

先來(lái)談一下怎樣才能學(xué)好Verilog這個(gè)問(wèn)題。有人說(shuō)學(xué)Verilog很難,好像比C語(yǔ)言還要難學(xué)。有一定難度是真的,但并沒(méi)有比別的語(yǔ)言更難學(xué)。我們剛開始學(xué)C語(yǔ)言的時(shí)候也覺(jué)得C語(yǔ)言很難,直到我們把思維方式轉(zhuǎn)變過(guò)來(lái)了,把微機(jī)原理學(xué)好了,能模擬CPU的運(yùn)行方式來(lái)思考問(wèn)題了,就會(huì)發(fā)現(xiàn)C語(yǔ)言也沒(méi)那么難了。所以這里面存在一個(gè)思維方式的轉(zhuǎn)換的過(guò)程。這對(duì)于學(xué)Verilog來(lái)說(shuō)也是一樣的,只不過(guò)Verilog比C語(yǔ)言還要更加底層,我們只掌握了CPU的思維模式還不行,還需要再往下學(xué)一層“硬件電路的思維模式”,才能更好的掌握硬件編程語(yǔ)言。

Verilog設(shè)計(jì)謹(jǐn)記

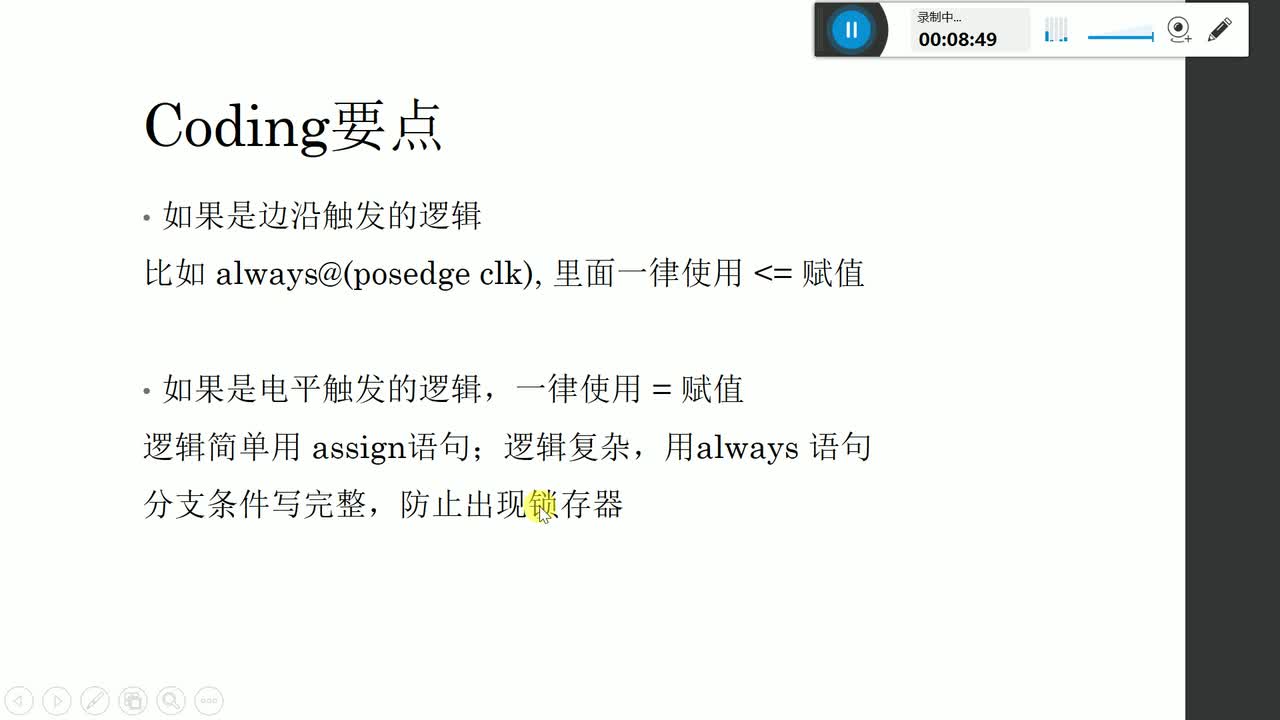

在學(xué)習(xí)Verilog過(guò)程中,總結(jié)了一些經(jīng)驗(yàn),為了保證Verilog HDL賦值語(yǔ)句的可綜合性,在建模時(shí)應(yīng)注意以下要點(diǎn):

不使用初始化語(yǔ)句;

不使用延時(shí)語(yǔ)句;

不使用initial。

不使用#10

不使用循環(huán)次數(shù)不確定的語(yǔ)句,如:forever,while等;

強(qiáng)烈建議同步方式設(shè)計(jì)電路;

盡量采用行為語(yǔ)句完成設(shè)計(jì);

always過(guò)程塊描述組合邏輯,應(yīng)在敏感信號(hào)表中列出所有的輸入信號(hào);

不能在一個(gè)以上的always過(guò)程塊中對(duì)同一個(gè)變量賦值。而對(duì)同一個(gè)賦值對(duì)象不能既使用阻塞式賦值,又使用非阻塞式賦值;

除非是關(guān)鍵路徑的設(shè)計(jì),一般不采用調(diào)用門級(jí)元件來(lái)描述設(shè)計(jì)的方法,建議采用行為語(yǔ)句來(lái)完成設(shè)計(jì);

所有的內(nèi)部寄存器都應(yīng)該可以被復(fù)位;

用戶自定義原件(UDP元件)是不能被綜合的;

在設(shè)計(jì)時(shí)總是記住時(shí)序問(wèn)題 ;

在一個(gè)設(shè)計(jì)開始就要考慮到地電平或高電平復(fù)位、同步或異步復(fù)位、上升沿或下降沿觸發(fā)等問(wèn)題,在所有模塊中都要遵守它 ;

在不同的情況下用if和case,最好少用if的多層嵌套(1層或2層比較合適,當(dāng)在3層以上時(shí),最好修改寫法,因?yàn)檫@樣不僅可以reduce area,而且可以獲得好的timing);

同一個(gè)變量的賦值不能受多個(gè)時(shí)鐘控制,也不能受兩種不同的時(shí)鐘條件(或者不同的時(shí)鐘沿)控制。

所有的內(nèi)部寄存器都應(yīng)該能夠被復(fù)位,在使用FPGA實(shí)現(xiàn)設(shè)計(jì)時(shí),應(yīng)盡量使用器件的全局復(fù)位端作為系統(tǒng)總的復(fù)位;

在鎖存一個(gè)信號(hào)或總線時(shí)要小心,對(duì)于整個(gè)design,盡量避免使用latch,因?yàn)樵贒FT時(shí)很難test;

確信所有的信號(hào)被復(fù)位,在DFT時(shí),所有的FlipFlop都是controllable;

永遠(yuǎn)不要再寫入之前讀取任何內(nèi)部存儲(chǔ)器(如SRAM);

從一個(gè)時(shí)鐘到另一個(gè)不同的時(shí)鐘傳輸數(shù)據(jù)時(shí)用數(shù)據(jù)緩沖,他工作像一個(gè)雙時(shí)鐘FIFO(是異步的),可以用Async SRAM搭建Async FIFO;

對(duì)時(shí)序邏輯描述和建模,應(yīng)盡量使用非阻塞賦值方式。對(duì)組合邏輯描述和建模,既可以用阻塞賦值,也可以用非阻塞賦值。但在同一個(gè)過(guò)程塊中,最好不要同時(shí)用阻塞賦值和非阻塞賦值;

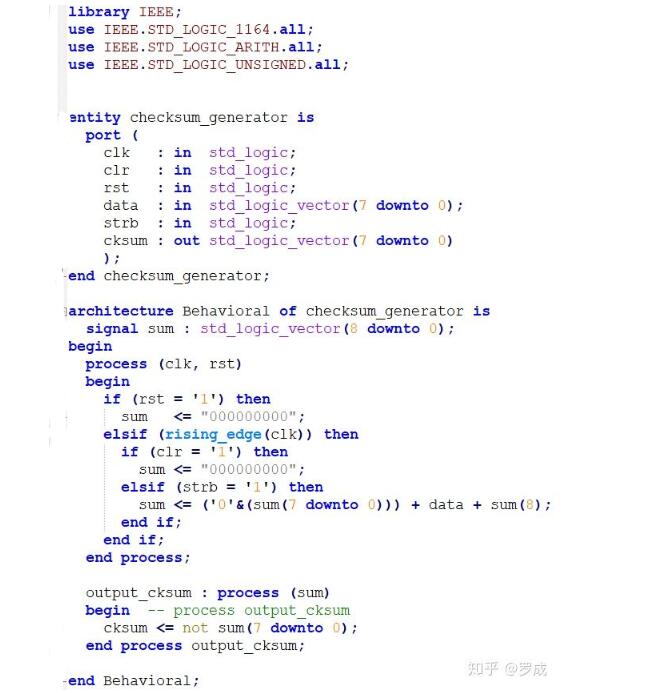

在VHDL中二維數(shù)組可以使用,它是非常有用的。在VERILOG中他僅僅可以使用在測(cè)試模塊中,不能被綜合 ;

遵守register-in register-out規(guī)則 ;

像synopsys的DC的綜合工具是非常穩(wěn)定的,任何bugs都不會(huì)從綜合工具中產(chǎn)生 ;

確保FPGA版本與ASIC的版本盡可能的相似,特別是SRAM類型,若版本一致是最理想的,但是在工作中FPGA版本一般用FPGA自帶的SRAM,ASIC版本一般用廠商提供的SRAM;

如果不打算把變量推導(dǎo)成鎖存器,那么必須在if語(yǔ)句或case語(yǔ)句的所有條件分支中都對(duì)變量明確地賦值。

在嵌入式存儲(chǔ)器中使用BIST ;

避免混合使用上升沿和下降沿觸發(fā)的觸發(fā)器;

虛單元和一些修正電路是必需的 ;

一些簡(jiǎn)單的測(cè)試電路也是需要的,經(jīng)常在一個(gè)芯片中有許多測(cè)試模塊 ;

除非低功耗不要用門控時(shí)鐘,強(qiáng)烈建議不要在design中使用gate clock ;

不要依靠腳本來(lái)保證設(shè)計(jì)。但是在腳本中的一些好的約束能夠起到更好的性能(例如前向加法器);

如果時(shí)間充裕,通過(guò)時(shí)鐘做一個(gè)多鎖存器來(lái)取代用MUX ;

不要用內(nèi)部tri-state, ASIC需要總線保持器來(lái)處理內(nèi)部tri-state,如IO cell;

在top level中作pad insertion ;

選擇pad時(shí)要小心(如上拉能力,施密特觸發(fā)器,5伏耐壓等),選擇合適的IO cell ;

小心由時(shí)鐘偏差引起的問(wèn)題 ;

不要試著產(chǎn)生半周期信號(hào) ;

如果有很多函數(shù)要修正,請(qǐng)一個(gè)一個(gè)地作,修正一個(gè)函數(shù)檢查一個(gè)函數(shù) ;

在一個(gè)計(jì)算等式中排列每個(gè)信號(hào)的位數(shù)是一個(gè)好習(xí)慣,即使綜合工具能做 ;

不要使用HDL提供的除法器 ;

削減不必要的時(shí)鐘。它會(huì)在設(shè)計(jì)和布局中引起很多麻煩,大多數(shù)FPGA有1-4個(gè)專門的時(shí)鐘通道。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論