Cadence近日宣布,其數(shù)字和定制/模擬流程在Intel的18A工藝技術(shù)上成功通過(guò)認(rèn)證。這一里程碑式的成就意味著Cadence的設(shè)計(jì)IP將全面支持Intel的代工廠(chǎng)在這一關(guān)鍵節(jié)點(diǎn)上的工作,并提供制程設(shè)計(jì)套件(PDK),助力開(kāi)發(fā)者加速一系列前沿應(yīng)用的開(kāi)發(fā),包括低功耗消費(fèi)電子、高性能計(jì)算(HPC)、人工智能和移動(dòng)計(jì)算設(shè)計(jì)。

值得一提的是,Cadence的研發(fā)團(tuán)隊(duì)與Intel代工廠(chǎng)緊密合作,確保了流程的兼容性和高效性。這次認(rèn)證不僅為客戶(hù)提供了一流的SoC(系統(tǒng)級(jí)芯片)和芯片系統(tǒng)設(shè)計(jì)能力,還推動(dòng)了更先進(jìn)的人工智能、高性能計(jì)算和高級(jí)移動(dòng)應(yīng)用的開(kāi)發(fā)。

Cadence為Intel 18A技術(shù)設(shè)計(jì)的IP具有廣泛的應(yīng)用范圍,特別在高性能計(jì)算(HPC)和人工智能/機(jī)器學(xué)習(xí)(AI/ML)領(lǐng)域表現(xiàn)出色。其中包括支持企業(yè)級(jí)PCI Express(PCIe)6.0和Compute Express Link(CXL)的解決方案,為數(shù)據(jù)傳輸和計(jì)算性能提供了強(qiáng)大的支持。此外,LPDDR5X/5 8533Mbps的多標(biāo)準(zhǔn)PHY則能夠滿(mǎn)足多樣化的存儲(chǔ)應(yīng)用需求。值得一提的是,UCIe技術(shù)將進(jìn)一步提升多芯片系統(tǒng)的封裝集成能力,而112G超長(zhǎng)距離SerDes則以其卓越的比特誤碼率(BER)性能,為數(shù)據(jù)傳輸提供了堅(jiān)實(shí)的保障。

此次認(rèn)證不僅證明了Cadence在半導(dǎo)體設(shè)計(jì)領(lǐng)域的領(lǐng)先地位,也為其客戶(hù)提供了更加可靠和高效的設(shè)計(jì)流程和設(shè)計(jì)IP。隨著這些先進(jìn)的工具和技術(shù)的廣泛應(yīng)用,我們有理由期待在未來(lái)看到更多創(chuàng)新的產(chǎn)品和應(yīng)用快速上市,滿(mǎn)足市場(chǎng)和消費(fèi)者的需求。

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28669瀏覽量

233451 -

Cadence

+關(guān)注

關(guān)注

67文章

966瀏覽量

143918 -

intel

+關(guān)注

關(guān)注

19文章

3493瀏覽量

188069

發(fā)布評(píng)論請(qǐng)先 登錄

Cadence攜手臺(tái)積公司,推出經(jīng)過(guò)其A16和N2P工藝技術(shù)認(rèn)證的設(shè)計(jì)解決方案,推動(dòng) AI 和 3D-IC芯片設(shè)計(jì)發(fā)展

新思科技與英特爾在EDA和IP領(lǐng)域展開(kāi)深度合作

BiCMOS工藝技術(shù)解析

英特爾 Panther Lake 移動(dòng) SoC 延遲上市,又是18A背鍋?

英特爾18A與臺(tái)積電N2工藝各有千秋

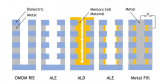

ALD和ALE核心工藝技術(shù)對(duì)比

Cadence數(shù)字和定制/模擬流程通過(guò)Intel 18A工藝技術(shù)認(rèn)證

Cadence數(shù)字和定制/模擬流程通過(guò)Intel 18A工藝技術(shù)認(rèn)證

評(píng)論