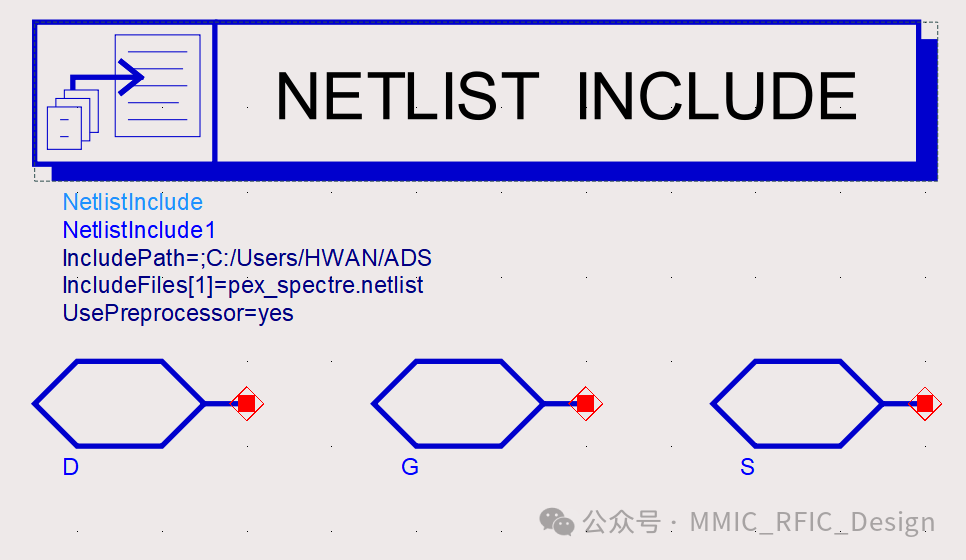

ADS是支持調(diào)用spice/spectre等網(wǎng)表文件進(jìn)行仿真的,可以用NetlistInclude控件來進(jìn)行調(diào)用。其中,spectre的網(wǎng)表可以直接讀取,并不需要執(zhí)行Import-->Design-->Netlist流程來進(jìn)行導(dǎo)入。

01

簡單示例

參考ADS的help文檔,調(diào)用netlist非常簡單。

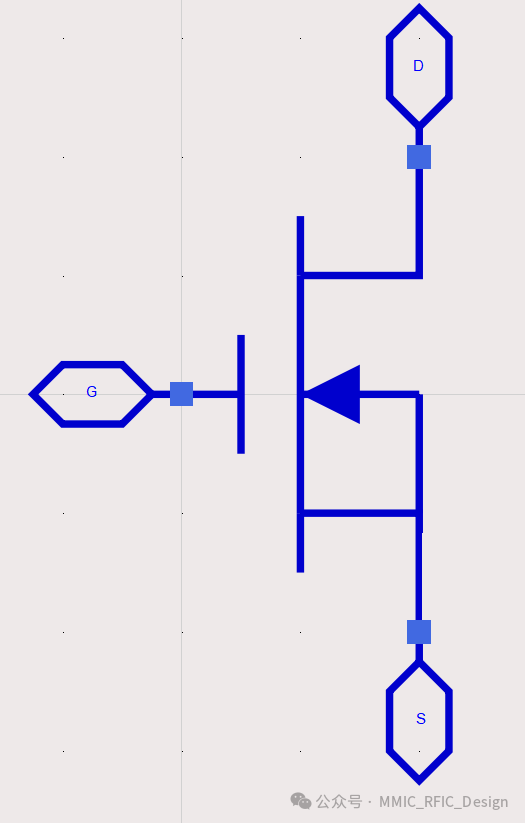

比如有一個PEX生成的spectre網(wǎng)表:pex_spectre.netlist,里面有一只MOS管,有三個端口D/G/S。只需要添加一個NetlistInclude控件,然后瀏覽并添加該網(wǎng)表,對應(yīng)放三個端口D/G/S,再生成一個Symbol就可以當(dāng)一個元件在ADS中來調(diào)用了。

02

薛定諤的NetlistInclude

然而作者在仿真過程中發(fā)現(xiàn)事情不沒有那么簡單,由于工藝PDK限制,該P(yáng)DK僅支持原理圖仿真和Layout繪制,但因為GDS Layer Number和Layer Purpose存在重復(fù),跟ADS不兼容,導(dǎo)致無法進(jìn)行EM仿真,EM仿真用的Substrate文件也沒有也沒有集成進(jìn)PDK中,因此無法像GaAs那樣全ADS搞定所有設(shè)計。

但是該工藝又單獨(dú)提供了一個用于ADS進(jìn)行EM仿真的Library(包含了Substrate文件,本文用EM_library代稱),它大致思路就是拋棄了大量EM無關(guān)的GDS Layer,例如DRC/LVS等驗證用的輔助識別圖層,而僅保留了EM仿真相關(guān)的幾個工藝圖層,例如金屬和過孔圖層,這樣就不存在圖層重復(fù)的問題了,要想進(jìn)行EM仿真,還需要從Cadence中導(dǎo)出GDS,然后導(dǎo)入進(jìn)ADS工程的EM_library中,再添加端口進(jìn)行EM仿真。

最后就導(dǎo)致了我為了進(jìn)行一個完整的芯片設(shè)計,需要在多個軟件環(huán)境、多個Library中來回折騰:

在Cadence中建立一個Library(本文用LVS_library代稱),attach到Cadence專用的PDK,進(jìn)行Schematic和Layout、DRC、LVS;

在ADS中建立一個EM仿真用的Library(本文用EM_library代稱),不需要attach到任何工藝包,這是廠家定義好的;

在ADS中建立一個聯(lián)合仿真用的Library(本文用Cosim_library代稱),attach到ADS專用的PDK,將PDK中的晶體管等元件與EM_library得到的emModel聯(lián)合起來進(jìn)行完整的仿真。

以上全部流程都沒有問題了,雖然繁瑣到令人反感、惡心、頭痛,但終歸是都能跑通,得到正常的仿真結(jié)果。

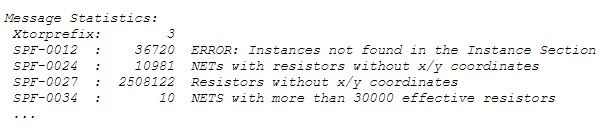

但當(dāng)我需要更進(jìn)一步,把晶體管等原理圖模型換成PEX提取的spectre網(wǎng)表進(jìn)行后仿時幽靈就出現(xiàn)了,我把它稱為薛定諤的NetlistInclude:

一開始,我參考前文示例中描述的那樣用NetlistInclude,生成symbol,再調(diào)用cell,OK沒問題;這個symbol我是放在Cosim_library中的;

后來,不知道什么時候由于什么原因,在調(diào)用這個Cosim_library中的cell仿真死活就不對了,表現(xiàn)出來的現(xiàn)象就等于這個cell是完全的、理想的開路狀態(tài),就是壓根沒接入電路中;

這時候,再把這個cell復(fù)制到一個新建的Library中,或者file-->import-->design-->netlist導(dǎo)入時選擇自動新建Library(本文用PEX_library代稱),最后再調(diào)用這個PEX_library中的cell,聯(lián)合仿真結(jié)果就正常了;

然后,把前面這個正常的PEX_library中的cell復(fù)制到Cosim_library中,重新調(diào)用,結(jié)果還是完全的、理想的開路狀態(tài),就是壓根沒接入電路中;

最后,用emCosim模式時,對應(yīng)器件partitioning選擇circuit/schematic調(diào)用ADS的PDK元件模型是正常的,但是調(diào)用PEX_library中的cell結(jié)果還是完全的、理想的開路狀態(tài),就是壓根沒接入電路中;

總之,這個NetlistInlude去調(diào)用PEX生成的spectre netlist仿真完全就是一個讓人琢磨不透的幽靈狀態(tài)。

審核編輯:劉清

-

MOS管

+關(guān)注

關(guān)注

109文章

2537瀏覽量

70044 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1071瀏覽量

55491 -

晶體管

+關(guān)注

關(guān)注

77文章

9989瀏覽量

140845 -

Layout

+關(guān)注

關(guān)注

15文章

413瀏覽量

62913 -

GaAs

+關(guān)注

關(guān)注

3文章

890瀏覽量

23770

原文標(biāo)題:作者求助:ADS調(diào)用spectre網(wǎng)表仿真異常——薛定諤的NetlistInclude

文章出處:【微信號:芯片設(shè)計之路,微信公眾號:芯片設(shè)計之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

spectre和hpeesofsim仿真直流電壓結(jié)果不同

網(wǎng)表包含不起作用

請問一下spectre19或spectre20做長時間仿真時出現(xiàn)error停止該如何解決?

Cadence IC617的Spectre下gm/ID曲線的仿真怎么設(shè)置?

請問在spectre仿真器中怎么去使用spice模型?

請大神指點(diǎn)為什么spectre不能連續(xù)進(jìn)行仿真?

誰能告訴我為什么spectre仿真窗口不能全屏設(shè)置?

實驗一ADS仿真基礎(chǔ)

如何解決常見的Spectre EMIR問題

Vivado調(diào)用Modelsim仿真

ADS調(diào)用spectre網(wǎng)表仿真異常—薛定諤的NetlistInclude

ADS調(diào)用spectre網(wǎng)表仿真異常—薛定諤的NetlistInclude

評論