最近的視覺AI模型必須處理動態(tài)和復(fù)雜的環(huán)境,因此在實時應(yīng)用中需要更高的能效和速度。

為了滿足市場需求,瑞薩發(fā)布了下一代動態(tài)可重構(gòu)人工智能處理器(DRP-AI)加速器。DRP-AI加速器提供10 TOPS/W的高功率效率,比傳統(tǒng)技術(shù)高出10倍,它可以在低功耗的傳統(tǒng)嵌入式處理器(MPU)上面運行復(fù)雜的圖像AI模型,而不需要像以前一樣采用高功耗的GPU來運行。

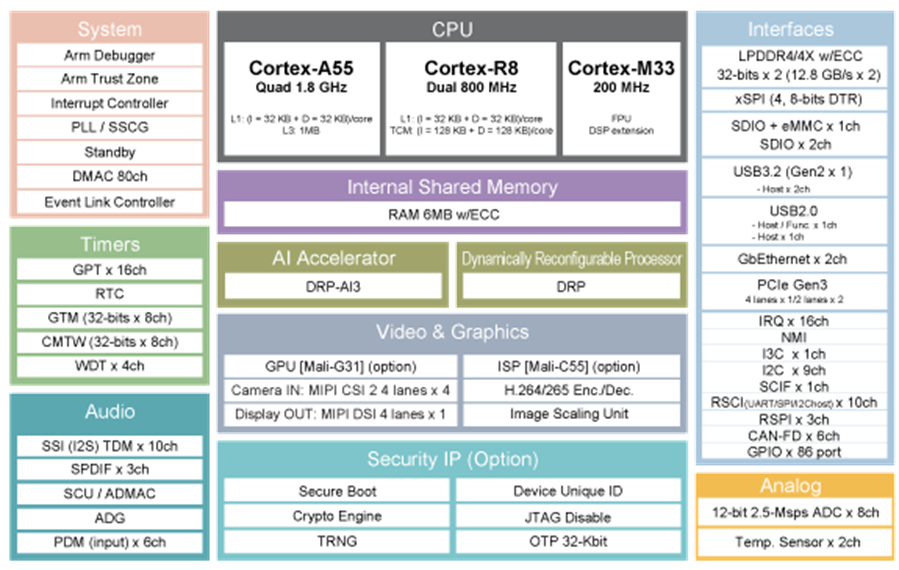

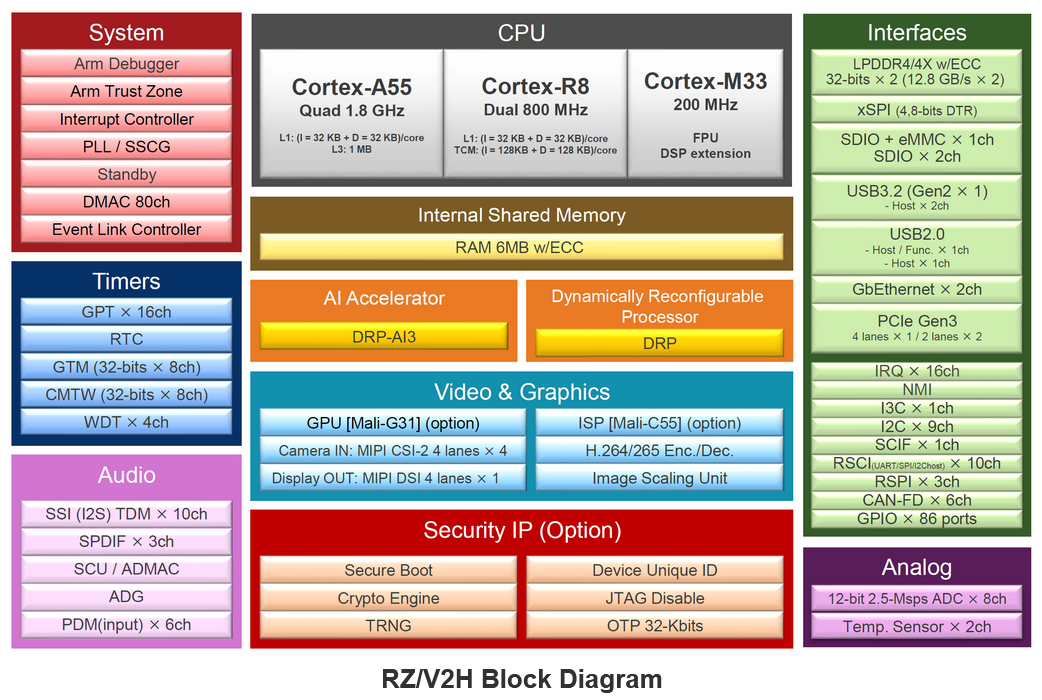

除了這個AI加速器外,高端RZ/V2H MPU還配備了使用動態(tài)可重構(gòu)處理器(DRP)的圖像處理加速器、運行頻率高達1.8GHz的四核Linux處理器Arm Cortex-A55、雙核800MHz Arm Cortex-R8高速實時處理器和I/O處理Arm Cortex-M33子內(nèi)核,采用異構(gòu)多處理器配置。

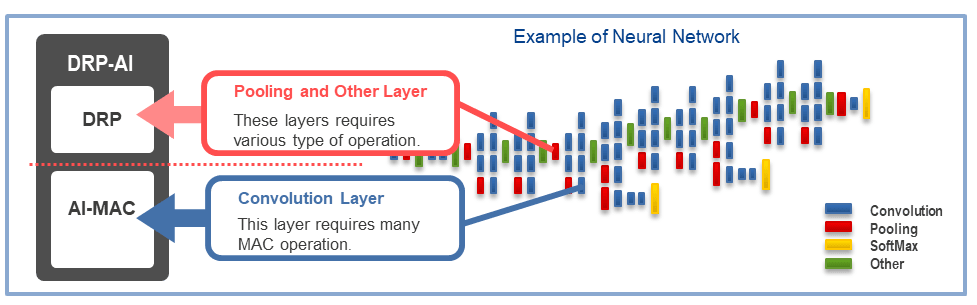

動態(tài)可重構(gòu)處理器(DRP)

七個基于Arm的CPU內(nèi)核、下一代DRP-AI和DRP的組合,可以立即處理機械控制中的圖像識別和AI判斷結(jié)果,使其成為下一代自主機器人、自主移動機器人、無人機和其他應(yīng)用的理想AI處理器。

下一代AI加速器DRP-AI

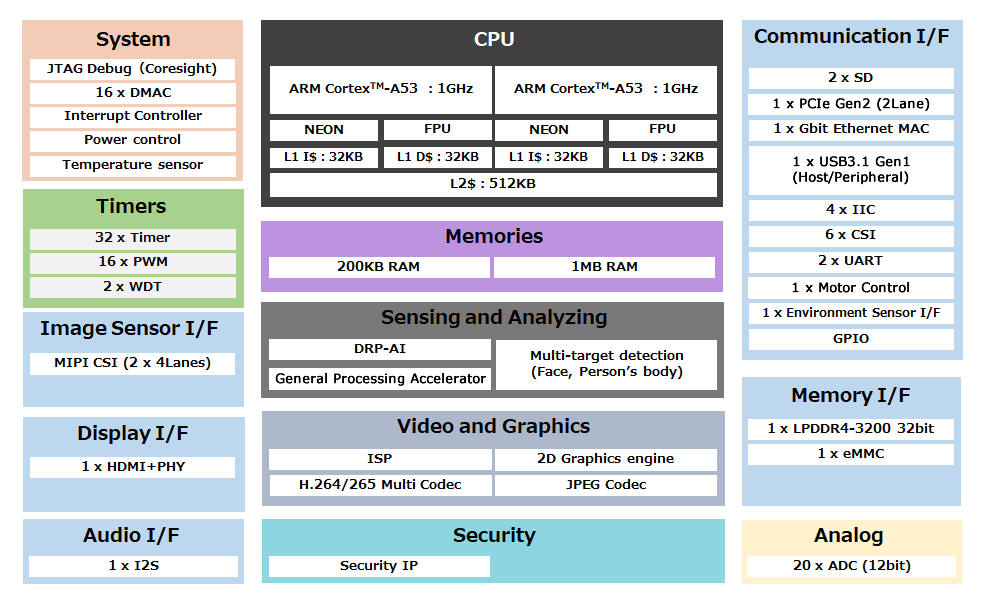

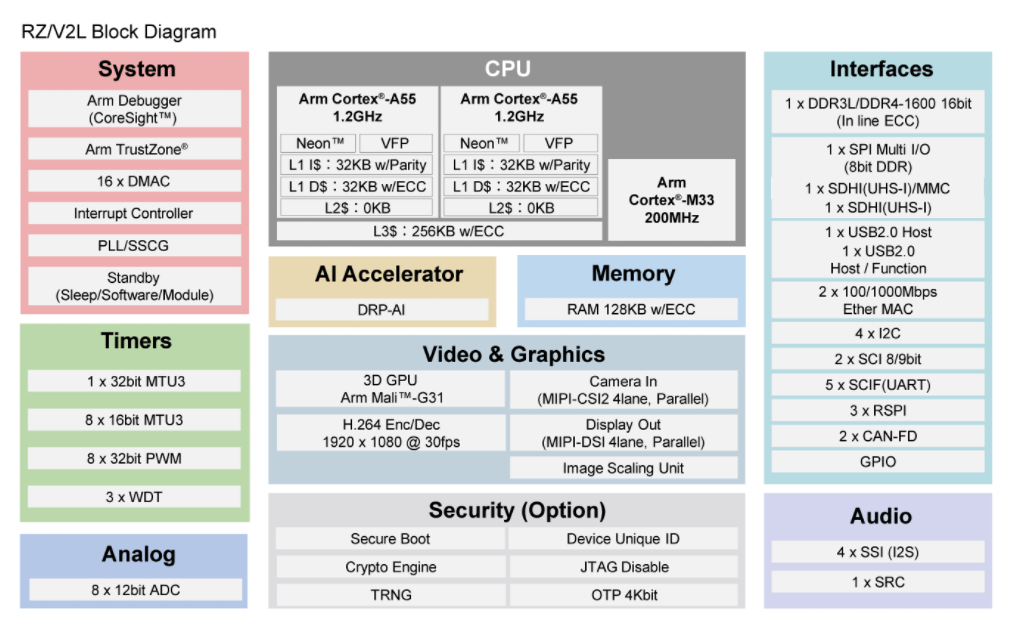

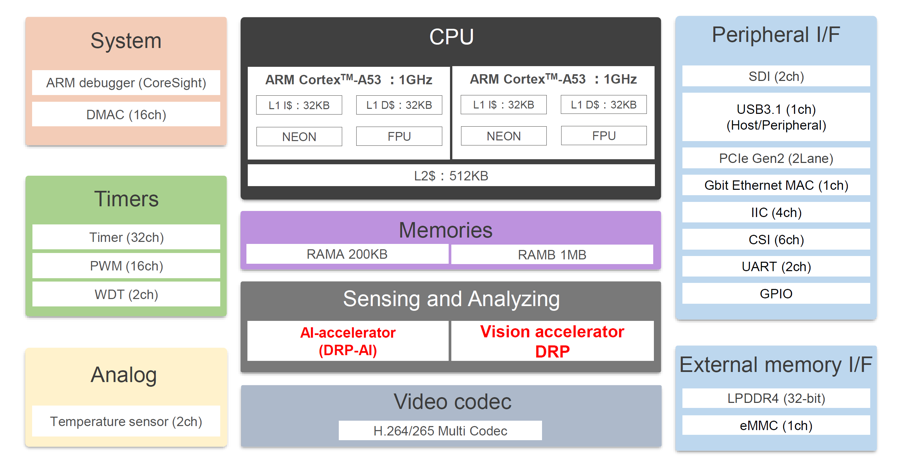

RZ/V2M、RZ/V2L和RZ/V2MA嵌入了瑞薩電子獨創(chuàng)的DRP-AI加速器,但瑞薩已將其獨創(chuàng)的AI加速器DRP-AI升級為下一代,以滿足最近的市場需求。

為了大幅提高電源效率,DRP-AI應(yīng)用了INT8量化和硬件支持,用于非結(jié)構(gòu)化修剪,這是傳統(tǒng)AI加速器難以實現(xiàn)的,以實現(xiàn)高達80 TOPS的推理性能和10 TOPS/W的電源效率。

下一代高能效AI加速器(DRP-AI3):自治系統(tǒng)高級AI中的嵌入式處理速度提高10倍”白皮書

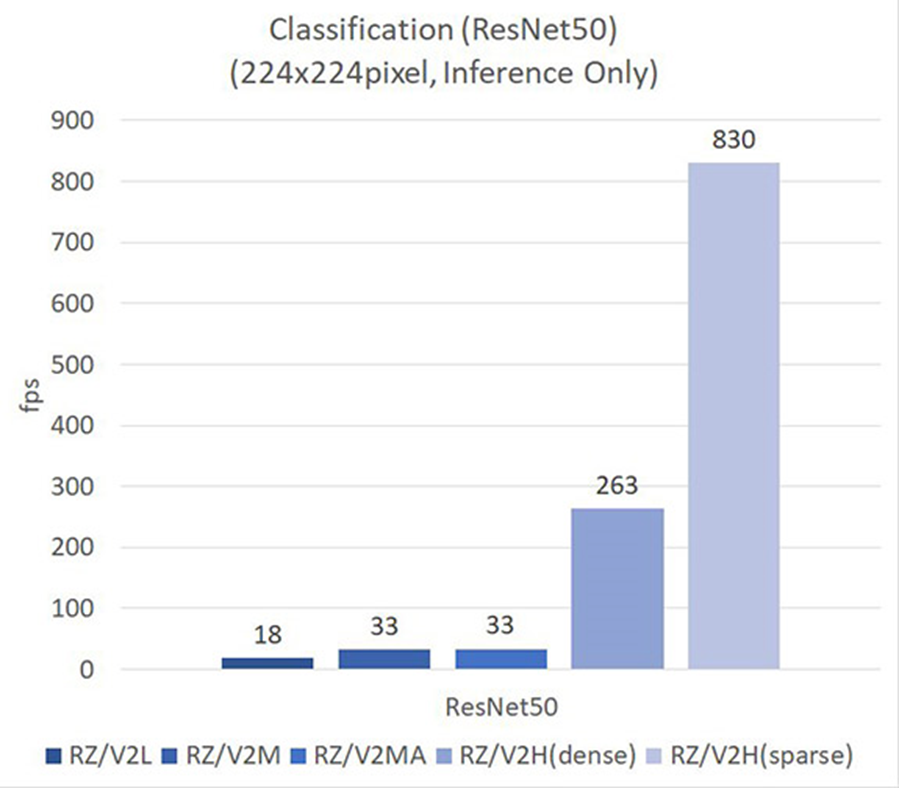

下圖1顯示了AI推理性能與其他RZ/V產(chǎn)品的比較。以ResNet-50為例,典型的分類卷積神經(jīng)網(wǎng)絡(luò)(CNN)的性能比不修剪的RZ/V2L高14倍(密集模型),采用模型修剪后的RZ/V2H比RZ/V2L(密集模型)性能高45倍。

圖1 RZ/V系列AI推理性能(不包括前/后處理)

通過動態(tài)可重構(gòu)處理器DRP打開CV加速

甚至在深度學(xué)習(xí)出現(xiàn)之前,各種方法就已被用于圖像識別和決策的應(yīng)用中。OpenCV這個開源的計算機視覺庫就是這樣一個例子。即使現(xiàn)在有了AI圖像處理,OpenCV仍然是一項非常有用的技術(shù)。Vision AI和OpenCV現(xiàn)在都在適當(dāng)?shù)膱鼍耙黄鹗褂谩?/p>

為了加速AI和OpenCV等各種圖像處理算法,RZ/V2H MPU設(shè)計了與DRP-AI分離的動態(tài)可重構(gòu)處理器,為OpenCV加速器提供DRP庫,充分利用其靈活性。

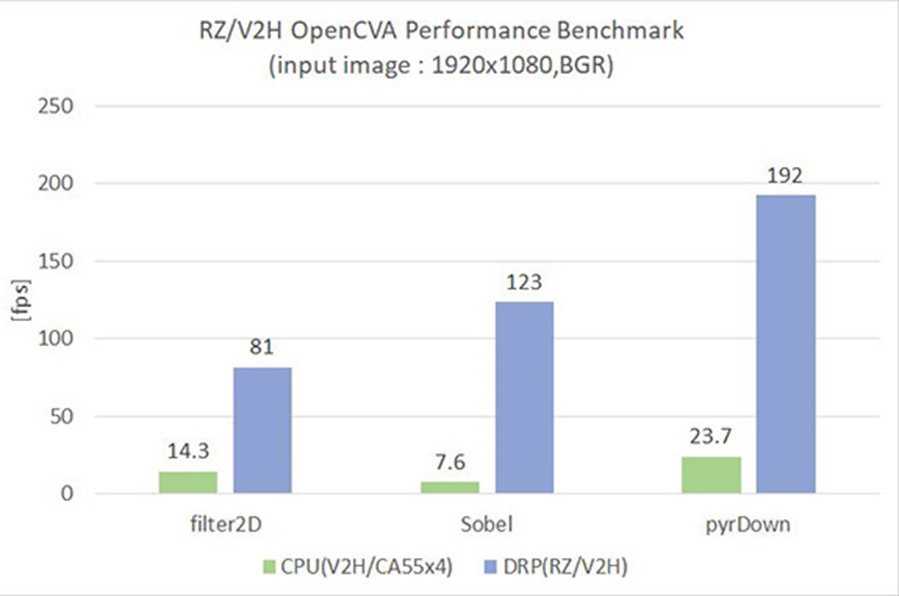

圖2比較了具有DRP的OpenCV加速器與RZ/V2H四核CPU的性能。例如,通過使用DRP加速,用于圖像邊緣檢測的Sobel濾波器從7.6fps提高到123fps的速度,提高了16倍。

圖2 OpenCV加速器性能基準測試

AI異構(gòu)配置+高速實時控制

雖然快速多核Linux處理器是圖像AI的最佳選擇,但它需要大量的內(nèi)存資源,并且很難實現(xiàn)機械控制所需的亞毫秒級實時性能。

為了解決這個問題,RZ/V2H使用四核Cortex-A55來運行包括AI處理在內(nèi)的Linux程序,并使用專用的高速實時處理器在需要高實時性能的應(yīng)用(如電機控制)中進行RTOS處理。

通過使用OpenAMP進行處理器間不同操作系統(tǒng)的通信連接,DRP-AI和Linux處理器做出的決策結(jié)果可以反映在RTOS處理器的實時機械控制中。

圖3 RZ/V2H框圖

具有這些獨特功能的RZ/V2H嵌入式AI微處理器已投入量產(chǎn),RZ/V2H評估板也可用于快速啟動您的下一個視覺AI開發(fā)。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19896瀏覽量

235244 -

機器人

+關(guān)注

關(guān)注

213文章

29748瀏覽量

212893 -

加速器

+關(guān)注

關(guān)注

2文章

827瀏覽量

39121 -

MPU

+關(guān)注

關(guān)注

0文章

415瀏覽量

49923 -

人工智能

+關(guān)注

關(guān)注

1806文章

49028瀏覽量

249529

原文標題:RZ/V2H MPU提高了機器人和自主應(yīng)用中的AI性能和實時控制

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Banana Pi 發(fā)布 BPI-AI2N & BPI-AI2N Carrier,助力 AI 計算與嵌入式開發(fā)

用于實時人類和物體識別的視覺-AI ASSP人工智能微處理器RZ/V2M數(shù)據(jù)手冊

3D圖形和視頻編解碼器引擎的通用微處理器RZ/V2L數(shù)據(jù)手冊

Banana Pi 與瑞薩電子攜手共同推動開源創(chuàng)新:BPI-AI2N

瑞薩推出集成DRP-AI加速器的RZ/V2N,擴展中端AI處理器陣容,助力未來智能工廠與智慧城市發(fā)展

蘋果加入UALink聯(lián)盟,共推AI加速器新標準

AI for Science:人工智能驅(qū)動科學(xué)創(chuàng)新》第4章-AI與生命科學(xué)讀后感

《AI for Science:人工智能驅(qū)動科學(xué)創(chuàng)新》第一章人工智能驅(qū)動的科學(xué)創(chuàng)新學(xué)習(xí)心得

Samtec AI 應(yīng)用詳述 | 人工智能加速器所需的連接器

risc-v在人工智能圖像處理應(yīng)用前景分析

IBM發(fā)布Telum II處理器:DPU性能飆升70%,引領(lǐng)技術(shù)創(chuàng)新浪潮

下一代高功能新一代AI加速器(DRP-AI3):10x在高級AI系統(tǒng)高級AI中更快的嵌入處理

瑞薩發(fā)布了下一代動態(tài)可重構(gòu)人工智能處理器(DRP-AI)加速器

瑞薩發(fā)布了下一代動態(tài)可重構(gòu)人工智能處理器(DRP-AI)加速器

評論