因?yàn)槲矣邢嚓P(guān)經(jīng)驗(yàn),解釋一下令人驚嘆的地方。

焊接挑戰(zhàn):

其實(shí)對(duì)于熟練焊工,焊點(diǎn)不良率控制在1ppm以下倒不是那么令人驚訝(對(duì)于一千個(gè)焊點(diǎn)的產(chǎn)品,1ppm的焊點(diǎn)缺陷意味著產(chǎn)品缺陷率為千分之一),如果采用有鉛焊錫,并不是很難。當(dāng)然,用無鉛焊錫(環(huán)保要求,現(xiàn)在正式工廠不讓用有鉛焊錫)難度會(huì)比有鉛很高很多。但是個(gè)人制作,不需要用無鉛焊錫,所以難度大大下降。

對(duì)于錯(cuò)件,原因有兩個(gè),圖紙錯(cuò)誤,插件錯(cuò)誤。前者可以靠仿真解決,電路圖對(duì)了,那么插件圖也就可以正確。后者靠細(xì)心同檢查了,也能解決。

最容易錯(cuò)的不是錯(cuò)件,而是錯(cuò)線。

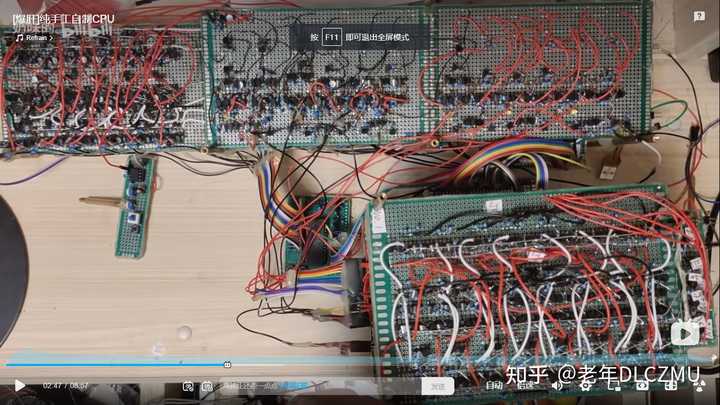

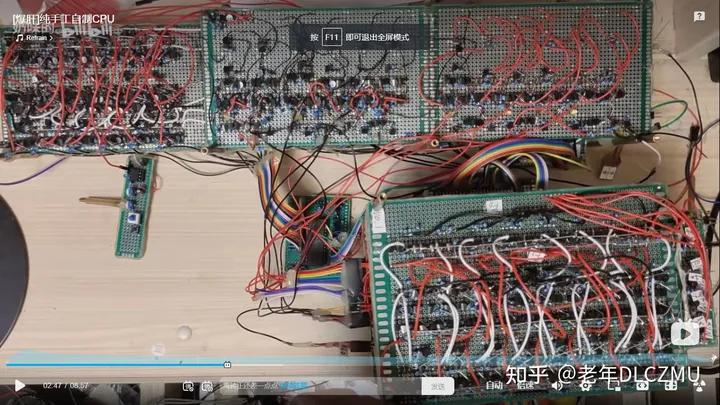

因?yàn)閺?a target="_blank">視頻中走線看,UP主不用線束,而是散線,所以很難畫走線圖。

用線束容易有干擾,除非用屏蔽線。我在90年代做高靈敏度磁頭放大器、高靈敏度電唱頭放大器的時(shí)候,曾經(jīng)面臨嚴(yán)峻的信號(hào)串?dāng)_的挑戰(zhàn)。

所以,在各種原型的制作中,有時(shí)候?yàn)榱私档透蓴_,要求走線很短很緊湊,確實(shí)不好用線束。

但是,不用線束不好畫走線圖,沒有走線圖的畫,這么多焊線太容易眼花導(dǎo)致出錯(cuò)了。

當(dāng)然,我們可以彩線來防止錯(cuò)線的。彩線種類太多,除了各種單色線(紅橙黃綠青藍(lán)色黑白),還有組合花色線(紅綠花、黑白花、紅白花、綠白花、橙白花。。。。)可以很好的解決這個(gè)問題。

這種彩線某寶上可以很方便的購(gòu)買,一排排的彩排線,不是很貴。

更不可思議的是,從視頻中看,該UP主主要用單色線。

其實(shí)該UP是有買彩排線,但是從視頻中看,該UP主僅僅是當(dāng)順序接線用,而不是當(dāng)亂序接線用。

其實(shí)彩排線如果作為順序線用,相比單色排線優(yōu)勢(shì)不大,其優(yōu)勢(shì)主要是在亂序接線中。

UP主不知是沒有經(jīng)驗(yàn),還是自信,居然在亂序接線中用的單色線,而不是用彩線。

干擾挑戰(zhàn):

1、這東西如果想像ENIAC那樣工作的話,必須模塊化設(shè)計(jì),另外,必須解決信號(hào)竄擾的問題。

ENICA是用電子管做的,早年的電子管信號(hào)的上升沿跟下降沿都很緩慢,并且工作頻率僅僅大概是5K左右,串?dāng)_不是很嚴(yán)重。

而現(xiàn)在的三極管開關(guān)性能遠(yuǎn)遠(yuǎn)強(qiáng)于以前的電子管,上升沿跟下降沿都很陡峭,會(huì)有嚴(yán)重的高次諧波成分。

如果用現(xiàn)在的三極管,為了讓上升沿下降沿變得緩慢,需要用電容濾波。

未見措施:

視頻中導(dǎo)線僅僅是裸線而不是屏蔽線,更要命的是這些線都離得很近。

大家別看到有別的設(shè)備線離得很近就照抄照搬。

如果是加了驅(qū)動(dòng)的輸出信號(hào),因?yàn)樵醋杩沟停瑢?duì)于數(shù)字電路來說,并不容易到干擾。

注意,必須是雙向低阻,推挽電路(比如CMOS)必須上拉或者下拉,共源電路漏極開路或者共射電路集電極開路接上拉電阻的不行,除非上拉電阻很小(很小的上拉電阻又會(huì)造成很大的電流)

但是如果是輸入信號(hào),因?yàn)樽杩垢撸呐率菙?shù)字電路,當(dāng)其他信號(hào)快速變化時(shí),假如電平上升或者下降的速度過快,該輸入端會(huì)收到其他信號(hào)上升沿同下降沿的信號(hào),從而產(chǎn)生毛刺。

這些信號(hào)毛刺通過電容、施密特電路等等措施處理掉之后,不會(huì)影響后面的邏輯。

元件太少:

但是,UP完全沒提到施密特電路同電容。實(shí)際上從UP說的元件數(shù)量,其集成度也不支持做那么多施密特電路。

地彈挑戰(zhàn)

很明顯,該UP主用的電路不是現(xiàn)在流行的差分電路,而是單端信號(hào)電路。(不學(xué)電子很多年了,忘了怎么叫了,大家明白意思就行了)

現(xiàn)在大家都用差分電路,所以這個(gè)問題可能已經(jīng)很難碰到了。

單端信號(hào)電路有個(gè)重大的問題很難解決,該UP主居然提都沒提。

這個(gè)問題就是地彈問題(rebound,我不知中文怎么講,我學(xué)電子的時(shí)候,國(guó)內(nèi)沒這個(gè)概念。這個(gè)概念是90年代跟老外學(xué)的。地彈這是我自己的翻譯)。

地彈原理:

在非射頻電路中,需要形成回路才能形成電流。在單端信號(hào)中,從信號(hào)線流出去,從地線流回來。

主要,地線可不是大家畫原理圖中理想的地線。原理圖中的地線是沒有電抗的(包括電阻、電感)的,實(shí)際的地線是有電抗的。信號(hào)“流出”的時(shí)候,經(jīng)過地線會(huì)產(chǎn)生壓降。

本來這不是問題,信號(hào)“流出”的時(shí)候,也會(huì)在信號(hào)線上產(chǎn)生壓降。數(shù)字電路容限大,給數(shù)字電路設(shè)置合適的閾值就行了,不會(huì)是問題。

但是,對(duì)于單端信號(hào)來說,地線是公用的,這就要了命了,多個(gè)信號(hào)都會(huì)地線上產(chǎn)生壓降,這個(gè)壓降等于瞬時(shí)電流x電抗。

對(duì)于輸入端來說,輸入的信號(hào)是輸出的信號(hào)疊加上地線的電壓。因?yàn)樾盘?hào)眾多,信號(hào)輸入端產(chǎn)生復(fù)雜的疊加,產(chǎn)生干擾。

因?yàn)榧w效應(yīng),導(dǎo)體電感等等因素,頻率越高,電抗越大,所以地彈越嚴(yán)重,干擾越嚴(yán)重。

所以,這個(gè)也會(huì)在輸入信號(hào)中形成毛刺。并且這個(gè)毛刺沒經(jīng)驗(yàn)的人很難發(fā)覺(因?yàn)槟銣y(cè)試的時(shí)候,你測(cè)到信號(hào)是基于參考點(diǎn)的,測(cè)到什么信號(hào),取決于你的參考點(diǎn))

有兩種方法可以改善這個(gè)問題。

1、合適的防止退耦電容來短路信號(hào)回路、

2、大面積敷銅來降低電抗(所謂接地層).

在該三極管CPU視頻發(fā)布之后一個(gè)月,另外有個(gè)UP主上傳了一個(gè)用門電路手搓CPU的視頻中,我看到相關(guān)的UP采用了這種方法來處理

在本三極管CPU的視頻中,我看不到相關(guān)措施。

頻率挑戰(zhàn):

因?yàn)樵揅PU有如此長(zhǎng)的線,信號(hào)在這些線上傳輸會(huì)產(chǎn)生復(fù)雜的延時(shí)、干擾,所以頻率不能過高。

做個(gè)參照,

@溫戈

回答(見文末鏈接)中提到的ENICA,我記得是5KHz。

該CPU雖然尺寸明顯更小,但是設(shè)計(jì),工藝明顯更差,我覺得很難超過ENICA的工作頻率。

再找另外一個(gè)參照Intel 4004,這是是英特爾制造的一款微處理器,片內(nèi)集成了2250個(gè)晶體管,晶體管之間的距離是10微米,能夠處理4bit的數(shù)據(jù),每秒運(yùn)算6萬次,頻率為108KHZ,前端總線為0.74MHz(4bit)。4004的最高頻率有740kHz,能執(zhí)行4位運(yùn)算,支持8位指令集及12位地址集

有人回答說說該CPU的工作頻率是“100KHz左右“,我是不太信的。

在視頻中這種工藝、設(shè)計(jì)的水平下,我非常驚訝達(dá)到這種頻率。

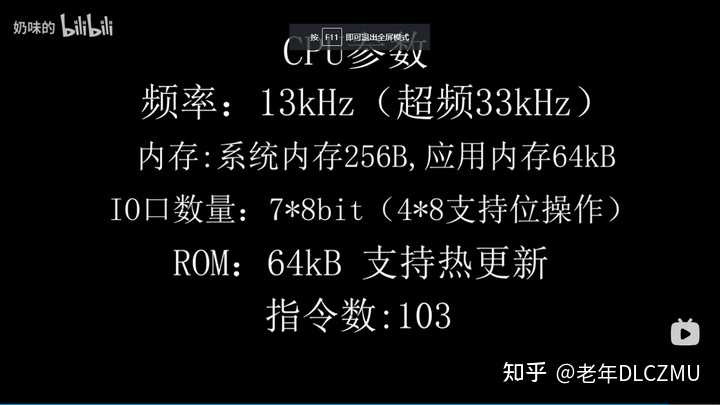

原UP主在另外一個(gè)視頻中說頻率是13KHz,更合乎邏輯。

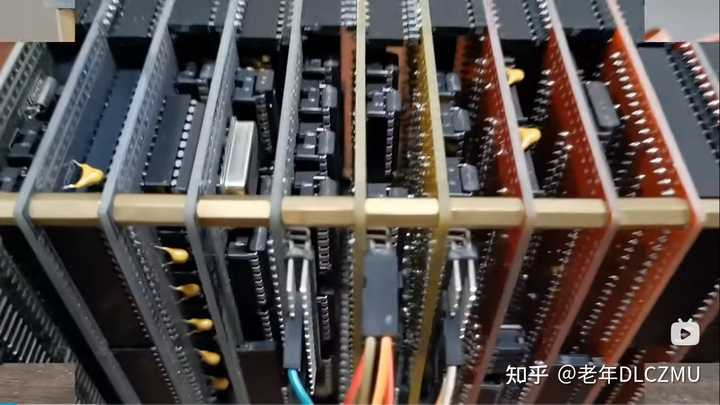

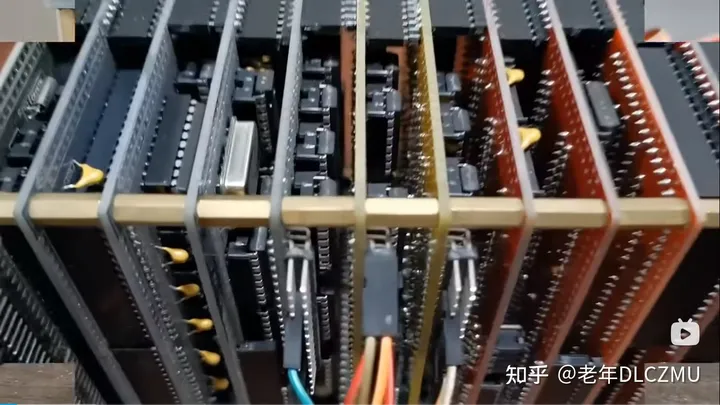

內(nèi)存挑戰(zhàn):

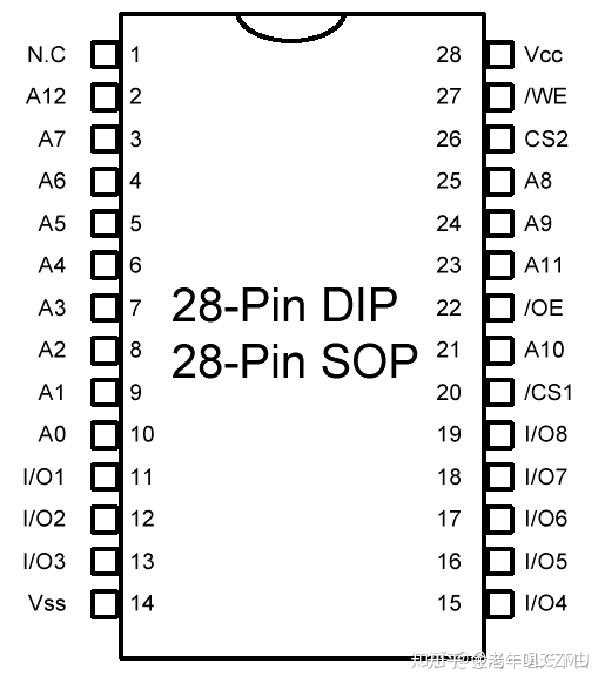

手搓CPU,我直覺上最多用8KB(64Kbit)的HM6264(如下圖) 8K*8bit,

芯片圖來自文獻(xiàn)2, 但原文獻(xiàn)所說2V電壓不對(duì),100ns,50/100uA, 55mA 4.5V 至 5.5V,通過使用兩個(gè)芯片使能輸入(/CE1、CE2)和低電平有效輸出使能 (/OE),

這種RAM不像后來的FP DRAM(Fast Page RRAM)同EDO DRAM(ExtendedDateOut DRAM),是沒有地址鎖存功能,所以不分行地址、列地址,容量每擴(kuò)大一倍,就要多一條地址線。

但是很多回答引用的文章說該UP主直接上了512KB的HM628512,當(dāng)然,這個(gè)問題不是很大,多出來的A線直接短接置0或者置1都行。

注意,HM628512的數(shù)據(jù)位寬是8位的512KB SRAM,該UP主視頻寫的是64KB.

注意,我們說的英特爾4004、8008等等早期低集成度的CPU是不帶內(nèi)存控制器的。

4位 Intel 4004 微處理器僅僅是 4 芯片組的一部分,這個(gè)被稱為 Intel MCS-4 的 4 芯片組包括微處理器、ROM、RAM 和用于 I/O 擴(kuò)展的移位寄存器

代碼挑戰(zhàn):

注意,很多答主引用的文章HM628512是ROM,我沒看懂。這個(gè)ROM做什么用?

ROM要求掉電后數(shù)據(jù)依然存在,HM628512掉電后數(shù)據(jù)就沒了,這點(diǎn)我沒看懂。

從手扣代碼的視頻來看,代碼部分像是用一大堆的撥動(dòng)開關(guān)實(shí)現(xiàn)的,

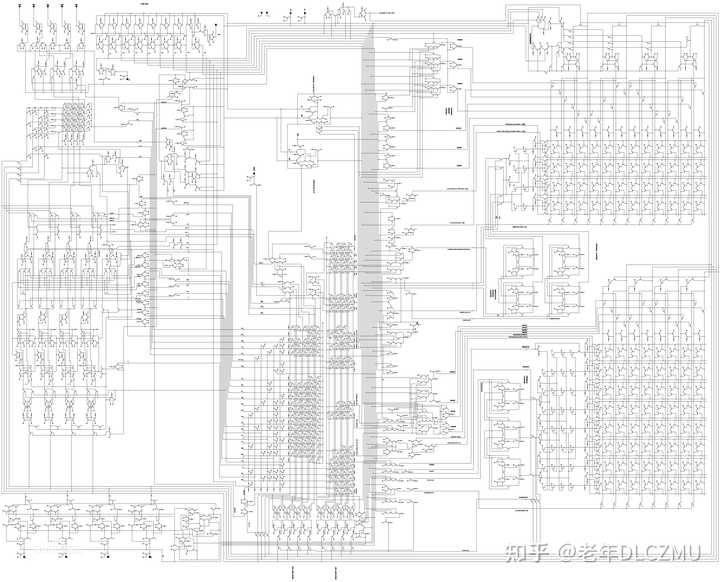

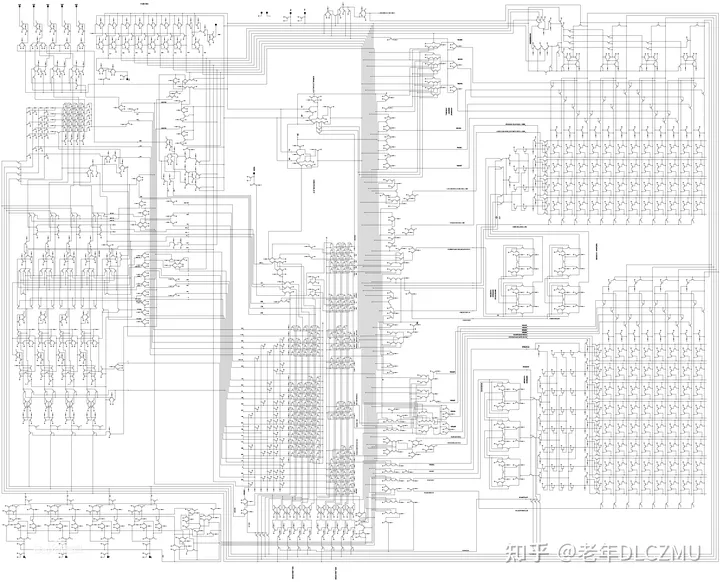

規(guī)模挑戰(zhàn):

4004的CPU是2250個(gè)晶體管,4位機(jī)。

最早的8位微處理器8008是3500 個(gè)晶體管,8008可以支援到16KB的內(nèi)存。

對(duì)應(yīng)的 CTC 8 位板級(jí)處理器,內(nèi)置約 100 個(gè) SSI (Small-scale-integration小規(guī)模集成電路)和 MSI(Middle-scale-integration中規(guī)模集成電路) TTL 芯片

本三極管CPU做的是8位機(jī),1000多個(gè)三極管、2000多個(gè)二極管,電阻數(shù)量2000多,直覺上感覺元器件數(shù)量不夠。

不過,很多門電路如果用三極管實(shí)現(xiàn),可以簡(jiǎn)單化,比如一個(gè)與非門,可以直接用兩個(gè)二極管加一個(gè)三極管做共射電路實(shí)現(xiàn)。但是,會(huì)產(chǎn)生我前面提到的問題。

而從原視頻中看相關(guān)工藝,又似乎并未嘗試去解決這些問題。

不知道熟悉電路的

@朱玉龍

大神,

@invalid s

有啥感想。

我的隱憂:

從工藝的角度看,用門電路手搓CPU我倒還是相信,我早年接觸的IBM XT的主板上也全是74系列門電路來實(shí)現(xiàn)內(nèi)存控制,IO轉(zhuǎn)換,工藝上沒有太大的問題。

并且,那個(gè)手搓門電路CPU的UP主還把各種設(shè)計(jì)文件開源了。

用三極管手搓CPU,也不是不可能,只是我覺得工藝上要非常小心。

看了三極管CPU的視頻同大家回答中轉(zhuǎn)載的介紹,因?yàn)闆]有看到其設(shè)計(jì)文件,總是難以置信。

這感覺就像看到有人手搓迷你版的運(yùn)載火箭一樣。

運(yùn)載火箭都變成迷你版了,當(dāng)然也不是不能手搓。但是看到這個(gè)迷你版的運(yùn)載火箭,用的是便宜的水洗煤,這個(gè)我就驚訝了。

所以,我一直想排除一種可能:

該三極管CPU最終制作失敗了,作者被折騰得精疲力竭,但是又不想白忙,畢竟亞歷山大大帝當(dāng)年也是一劍劈開了Gordian knot。傳說:戈?duì)柕蠟跛箛?guó)王打了一個(gè)十分難解的結(jié),即戈?duì)柕现Y(jié)(Gordian knot),并稱誰能解開便會(huì)成為亞洲的統(tǒng)治者,結(jié)果亞歷山大大帝大刀一揮揮劍將結(jié)斬?cái)唷?/p>

于是:

1、因?yàn)榧兇怛?qū)動(dòng)LED對(duì)邏輯的準(zhǔn)確性沒有太嚴(yán)格要求,錯(cuò)了對(duì)顯示結(jié)果的影響也不明顯,所以改成了一排排LED的驅(qū)動(dòng)電路,然后用單片機(jī)實(shí)現(xiàn)了相關(guān)功能。

2、因?yàn)樽隽魉疅舨恍鐲PU,可以用雙穩(wěn)態(tài)加延時(shí)等等很多方法實(shí)現(xiàn),原作者最后僅僅做了流水燈的一套實(shí)現(xiàn)電路

然后作者拍了視頻上傳說是CPU成功了。

后話:

原UP主花了兩年時(shí)間做這個(gè)奇跡工程,其心血同汗水值得尊重。并且,他在板上安置了大量LED(發(fā)光二極管)看起來也像是為了方便查找問題(其實(shí),這種情況下,用發(fā)光二極管取代普通二極管是一種很好的調(diào)試方法)。

如果該CPU確實(shí)其實(shí)沒有正常運(yùn)行,我希望它能夠早日正常運(yùn)行。

如果該CPU確實(shí)運(yùn)行正常了,我希望看到更多設(shè)計(jì)詳情以滿(da)足(xiao)好(yi)奇(wen)心。

作者:老年DLCZMU

來源:知乎

著作權(quán)歸作者所有。商業(yè)轉(zhuǎn)載請(qǐng)聯(lián)系作者獲得授權(quán),非商業(yè)轉(zhuǎn)載請(qǐng)注明出處。

審核編輯 黃宇

-

led

+關(guān)注

關(guān)注

242文章

23742瀏覽量

671455 -

晶體管

+關(guān)注

關(guān)注

77文章

9989瀏覽量

140845 -

中央處理器

+關(guān)注

關(guān)注

1文章

126瀏覽量

16791

發(fā)布評(píng)論請(qǐng)先 登錄

什么是中央處理器

中央處理器cpu性能排名

CPU中央處理器操作原理及應(yīng)用

B 站焊武帝爆火出圈:純手工拼晶體管自制 CPU,耗時(shí)半年,可跑程序

如何看待視頻博主耗時(shí)半年時(shí)間純手工拼晶體管自制成功中央處理器(CPU)?

如何看待視頻博主耗時(shí)半年時(shí)間純手工拼晶體管自制成功中央處理器(CPU)?

評(píng)論