一、簡介

MicroBlaze是AMD FPGA推出的一款32/64位軟核嵌入式處理器,其高度可配置,可滿足通信、工業(yè)、醫(yī)療、汽車、以及消費(fèi)類各場景需求。MicroBlaze是AMD FPGA嵌入式產(chǎn)品的重要組成部件,具有多功能互聯(lián)系統(tǒng),可支持各種嵌入式應(yīng)用。

MicroBlaze的易用性使得其開發(fā)如AMD其它嵌入式SoCFPGA一樣簡單。客戶在搭建含MicroBlaze IP的工程后,經(jīng)常遇到的問題是,如何將.bit文件與應(yīng)用程序.elf文件結(jié)合,固化到存儲器件中(一般指串型/并行FLASH)。下面將結(jié)合原理與固化過程,詳細(xì)描述此問題。

二、疑難理解

首先,要理解的一點是,AMD FPGA在配置了適當(dāng)?shù)膯幽J胶螅想娂磿丛撃J饺ゼ虞d配置文件。以7系列FPGA為例,假設(shè)設(shè)置模式引腳M[2:0]=3’b001,上電后FPGA會以MasterSPI方式嘗試從FLASH加載配置文件,其與工程是否含有MicroBlaze IP無關(guān)。其次,客戶經(jīng)常遇到的問題是,含MicroBlaze IP的工程中,需要考慮程序的運(yùn)行地址空間(涉及DDR MIG IP);需要考慮應(yīng)用程序的加載(涉及AXI Quad SPI IP),在固化時某些選項配置錯誤,導(dǎo)致系統(tǒng)無法啟動。

三、固化過程詳解

思考一個問題,在含有MicroBlaze的設(shè)計中,DDR MIG IP和AXI Quad SPI IP必須同時存在嗎?帶著這個疑問,下面詳細(xì)講解MicroBlaze兩種應(yīng)用場景下的固化過程。演示過程以7系列FPGA器件,以vitisv2022.2版本工具,以SPI FLASH存儲器件為例,其它系列器件和工具版本類似。

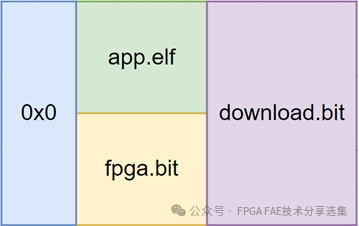

場景一,MicroBlaze運(yùn)行簡單的應(yīng)用。如GPIO控制,IIC、UART等低速嵌入式總線應(yīng)

用,或者負(fù)責(zé)一些復(fù)雜IP和外圍IC的初始化輔助性工作。此時,F(xiàn)PGA固化固件組成形式如下圖所示。

?

?

在這個場景下,vivado生成的fpga.bit文件和vitis生成的應(yīng)用程序app.elf文件,合并為download.bit文件,燒錄到FLASH的起始地址0x0中。此設(shè)計中,不需要借助AXI Quad SPI IP的應(yīng)用搬運(yùn)能力,對是否含有DDR MIG IP也無要求。下面展示該固化流程:

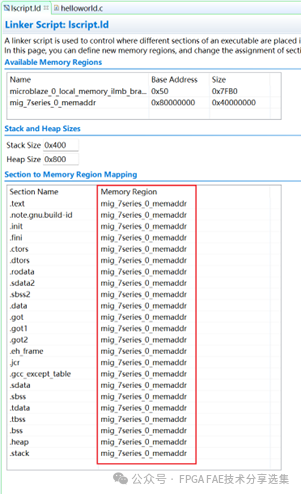

為增加迷惑性,設(shè)計中含有DDR MIG IP。vivado生成.bit文件后,導(dǎo)出.xsa文件,創(chuàng)建vitis軟件工程。應(yīng)用程序的ld腳本默認(rèn)Memory Region Mapping指向外部DDR。

?

?

點擊Program Device菜單生成download.bit文件將出現(xiàn)address mapped error錯誤,無法生成download.bit文件。

注意:

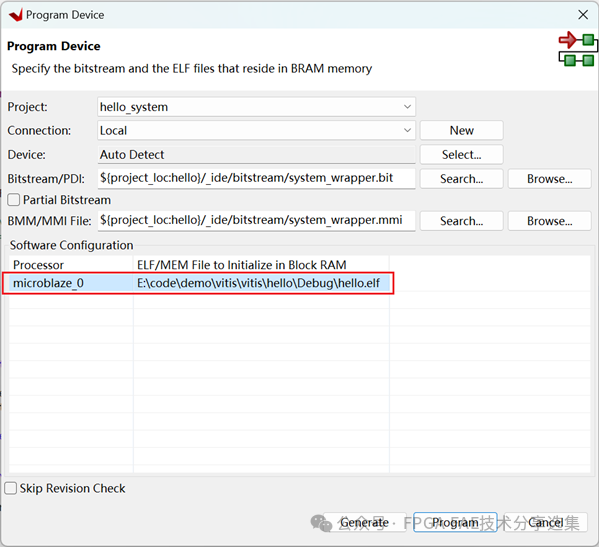

需要選擇應(yīng)用程序生成的.elf文件(如圖示的hello.elf文件),而不是vitis默認(rèn)的bootloader。 ?

?

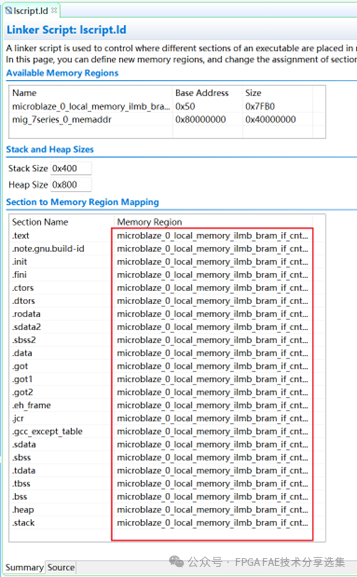

此時需要修改工程ld腳本文件,將MemoryRegion Mapping設(shè)置為local bram,如下圖所示

?

?

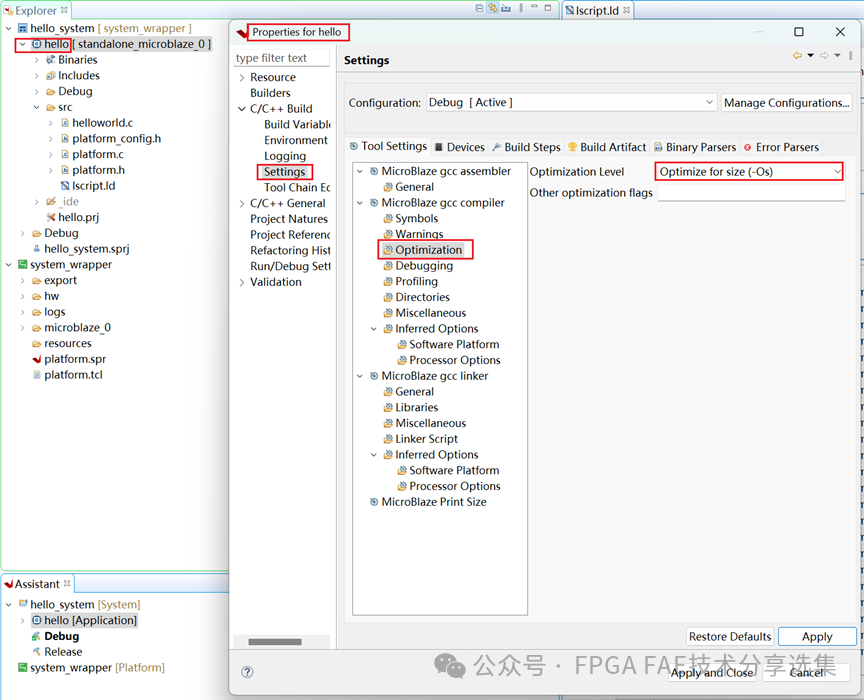

再次點擊Program Device菜單生成download.bit文件即可。由于一般情況下,為節(jié)省FPGA block ram資源,用于MicroBlaze的local bram并不會設(shè)置很大,可使用下圖所示優(yōu)化選項,減小固件的大小。 ?

?  ?

?

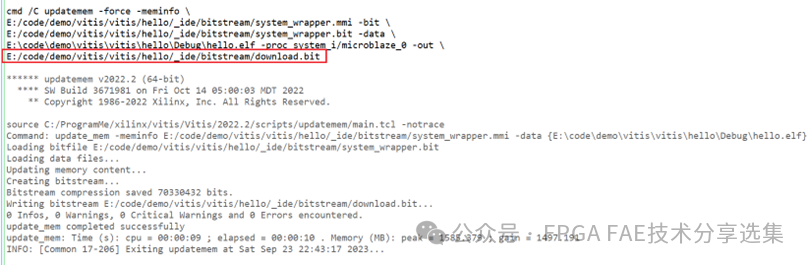

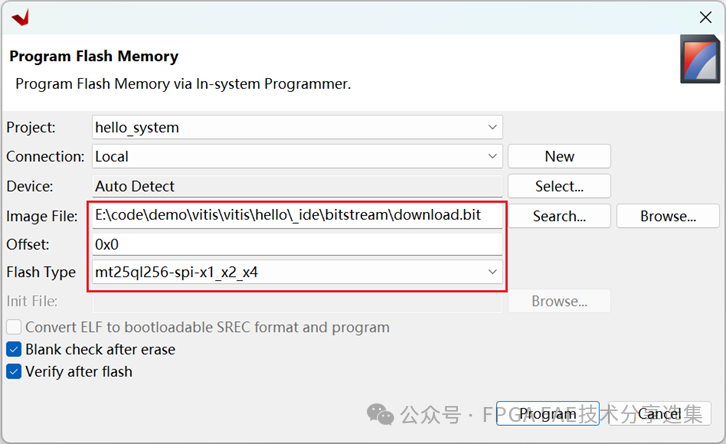

生成download.bit文件后,JTAG模式下,燒錄固件到FLASH中,注意Offset項為0x0。

?

?

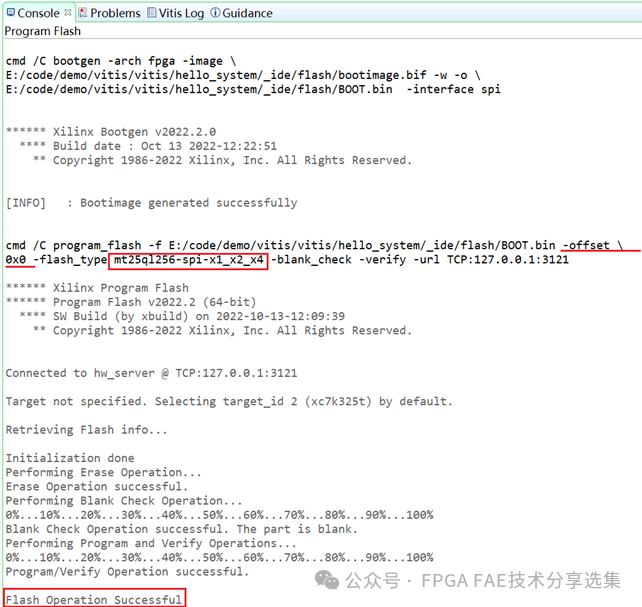

燒錄過程log記錄:

?

?

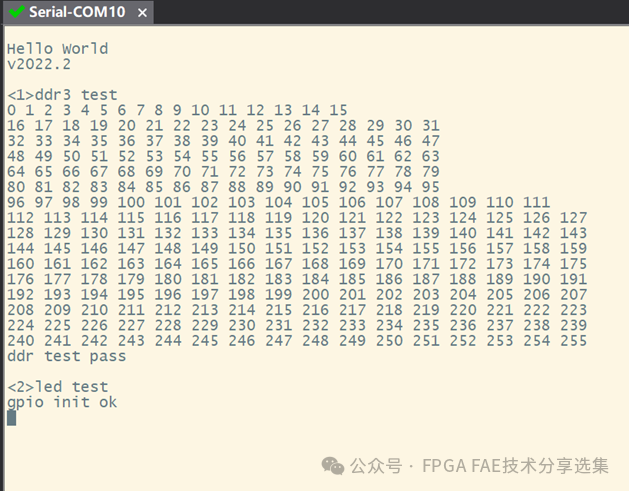

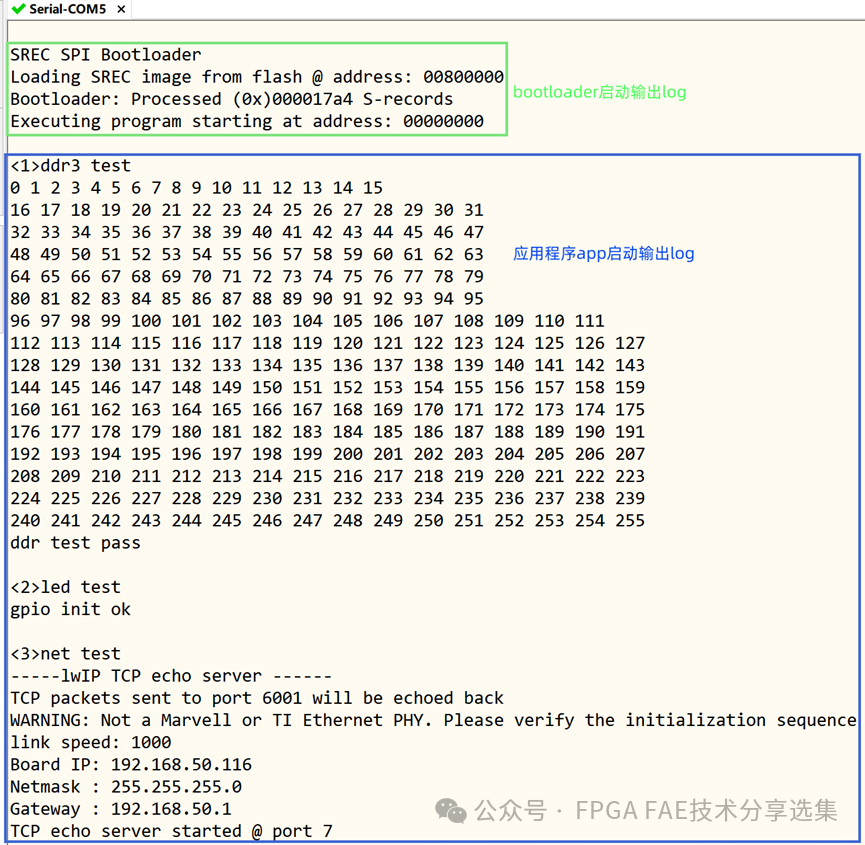

斷電,將啟動模式設(shè)置為Master SPI,系統(tǒng)啟動log如下:

上述展示了一個簡單的應(yīng)用程序的固件固化過程。

場景二,MicroBlaze運(yùn)行復(fù)雜的應(yīng)用。如輕量級的網(wǎng)絡(luò)協(xié)議棧LwIP,加載嵌入式文件

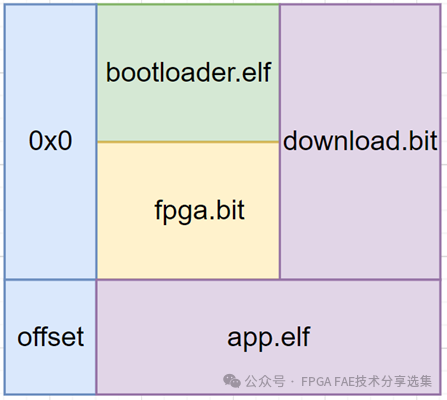

系統(tǒng)等。此場景一般生成的固件達(dá)到MB級別,對內(nèi)存也有一定需求,需要借助DDR來運(yùn)行應(yīng)用程序。此時,F(xiàn)PGA固化固件組成形式如下圖所示

?

?

在這個場景下,vivado生成的fpga.bit文件和vitis生成的應(yīng)用引導(dǎo)程序bootloader.elf文件,合并為download.bit文件,燒錄到FLASH的起始地址0x0中;復(fù)雜的應(yīng)用程序app.elf文件,燒錄到FLASH的指定offset地址中。

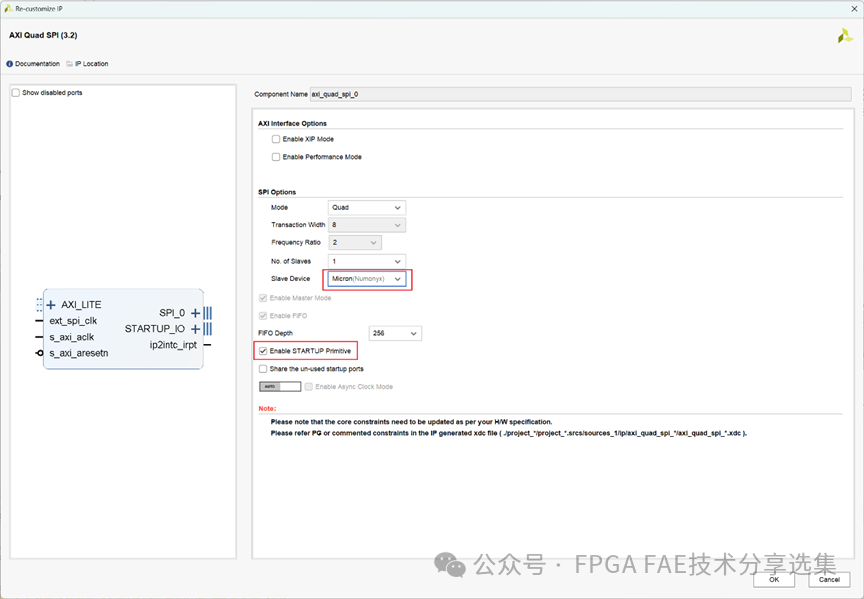

此設(shè)計中,必須借助AXI Quad SPI IP的應(yīng)用搬運(yùn)能力,復(fù)雜應(yīng)用程序一般對DDR也有要求,也即設(shè)計需要DDR MIG IP。下面展示該固化流程:

首先在vivado中,需要對AXI Quad SPI IP做正確的設(shè)置,選擇FLASH的型號,使能STARTUPPrimitive選項。

?

?

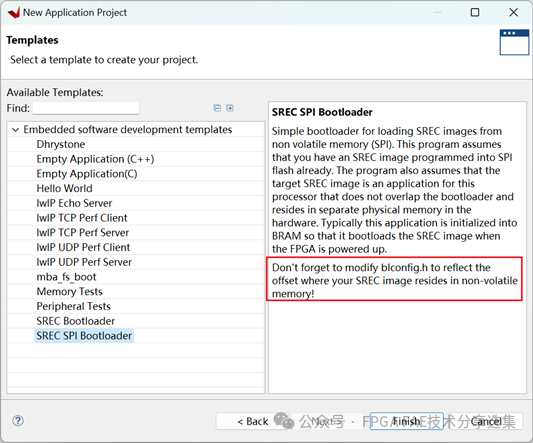

然后創(chuàng)建bootloader引導(dǎo)工程,如下

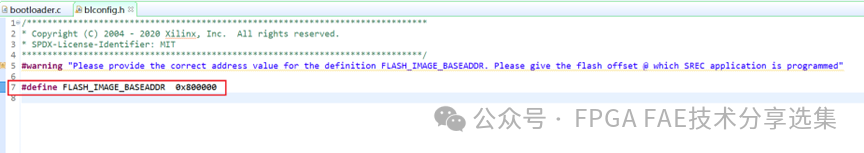

vitis工程引導(dǎo)界面提示修改合適的應(yīng)用程序offset address。

?

?

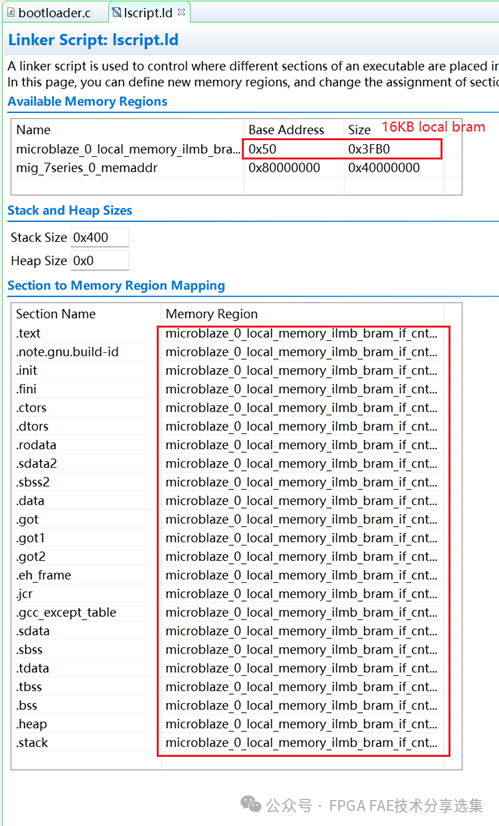

查看bootloader工程的ld腳本,確定bootloader工程的Memory Region Mapping指向為local bram。

?

?

同時需要修改應(yīng)用程序在FLASH中的程序地址,根據(jù)FLASH的容量大小,選擇合適的偏移地址。這里修改為0x800000(起始地址偏移8MB空間)。

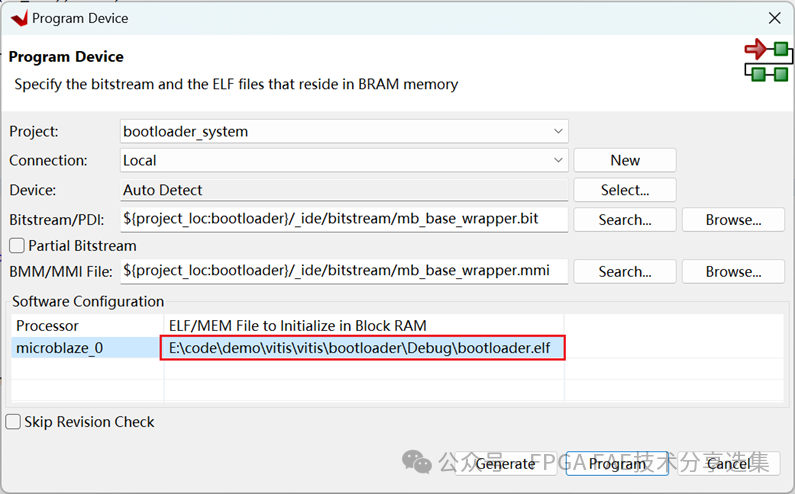

點擊Program Device菜單生成download.bit文件,注意選擇的是bootloader.elf文件。

備注:

vitis IDE中,此菜單項包含Generate和Program選項,一般JTAG未連接板卡時選擇Generate選項;連接JTAG在線調(diào)試時,選擇Program。但是無論是否連接JTAG,兩個選項都能生成download.bit文件。

?

?

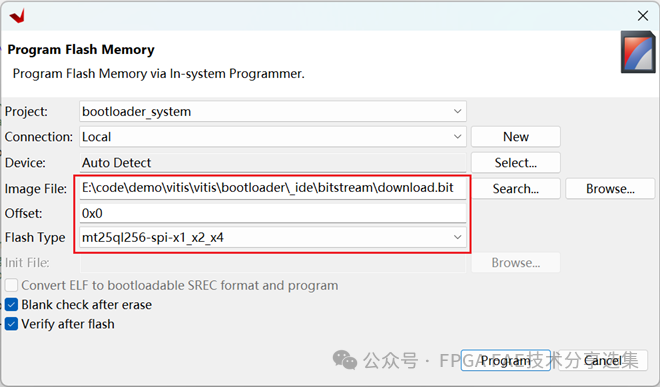

將生成的download.bit文件燒錄到FLASH的0x0地址中。

?

?

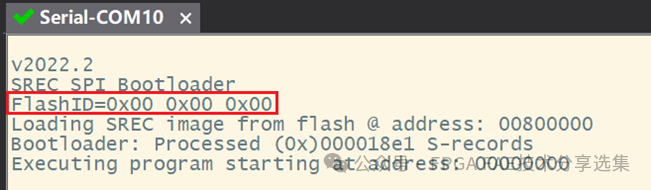

斷電,將啟動模式設(shè)置為Master SPI ,可驗證bootloader是否燒錄成功,其啟動log如上。

log顯示bootloader將從00800000地址中加載應(yīng)用程序固件,證明bootloader燒錄成功。

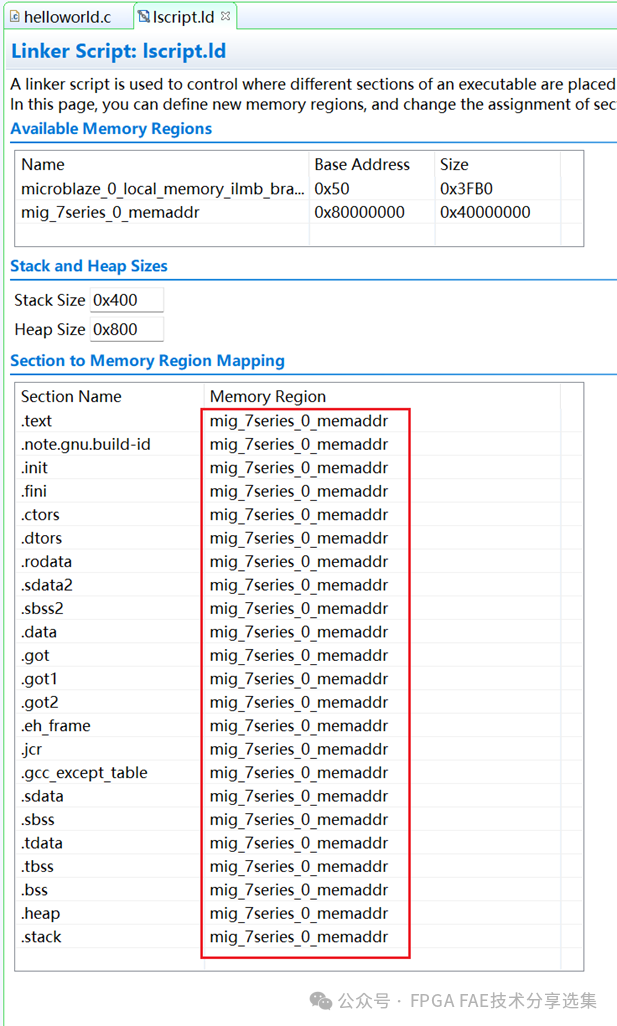

接下來創(chuàng)建應(yīng)用工程,應(yīng)用工程較復(fù)雜,所需運(yùn)行內(nèi)存較大,應(yīng)用工程的ld腳本文件Memory Region Mapping指向外部DDR。

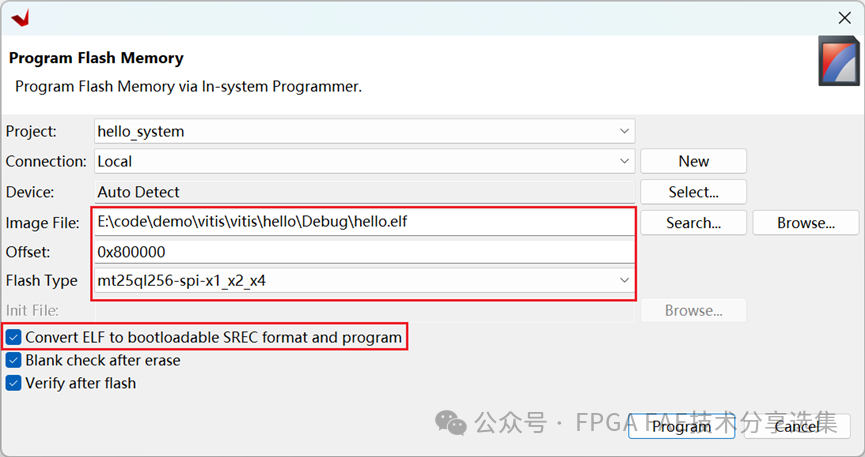

點擊Program Flash Memory菜單,將應(yīng)用程序hello.elf燒錄到FLASH中,注意Offset項為之前bootloader工程設(shè)置的0x800000,且需要勾選SREC轉(zhuǎn)換選項。

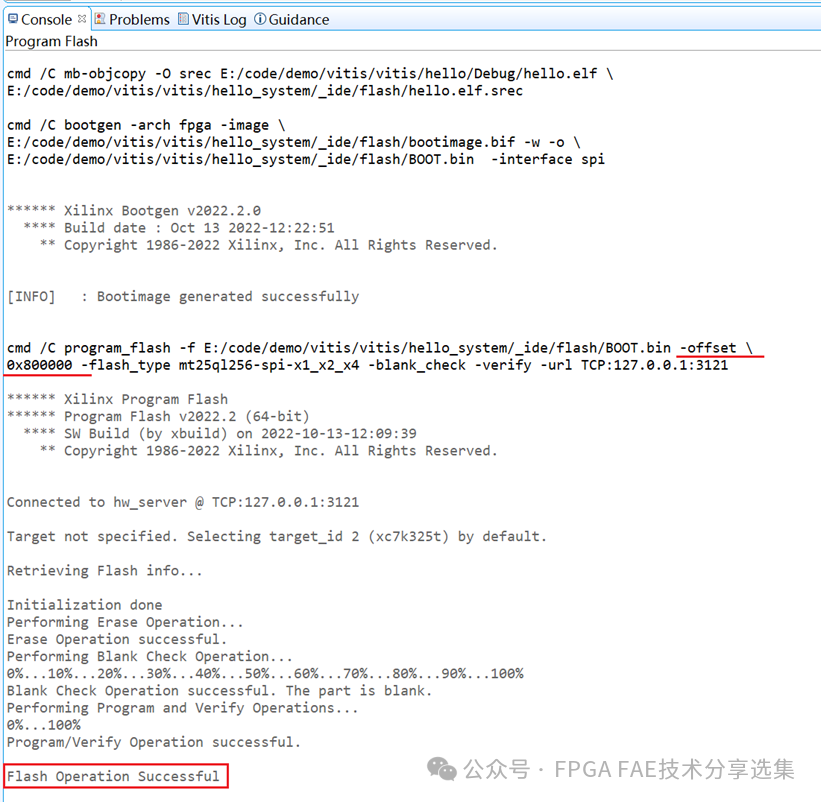

燒錄過程輸出log記錄。

斷電,將啟動模式設(shè)置為Master SPI,系統(tǒng)啟動log如下:

上述演示了一個稍復(fù)雜的應(yīng)用程序的固件固化過程。

四、總結(jié)與拓展

1. 通過燒錄過程可發(fā)現(xiàn),場景二的bootloader引導(dǎo)應(yīng)用程序即相當(dāng)于場景一的用戶程序;

2. 場景二的系統(tǒng)啟動速度相對場景一較慢,AMD FPGA提供了一種加速方法,詳細(xì)參考

https://support.xilinx.com/s/article/75646?language=en_US

3. 從2019.2版本工具開始,F(xiàn)LASH的驅(qū)動程序發(fā)生了變更,詳細(xì)參考

https://support.xilinx.com/s/article/73329?language=en_US

4. 從SDK到Vitis,上述固化過程原理不變,但一些菜單選項細(xì)節(jié)稍有不同;

5. 從UltraScale系列開始支持的SPIx8模式,細(xì)節(jié)上有一些區(qū)別,詳細(xì)參考官方手冊UG570。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1643文章

21966瀏覽量

614153 -

DDR

+關(guān)注

關(guān)注

11文章

731瀏覽量

66397 -

嵌入式處理器

+關(guān)注

關(guān)注

0文章

256瀏覽量

31131 -

GPIO

+關(guān)注

關(guān)注

16文章

1274瀏覽量

53586 -

SPI Flash

+關(guān)注

關(guān)注

1文章

13瀏覽量

10540

原文標(biāo)題:AMD FPGA的MicroBlaze固化流程

文章出處:【微信號:Comtech FPGA,微信公眾號:Comtech FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

MicroBlaze MCS和MicroBlaze的區(qū)別在哪?

【Artix-7 50T FPGA試用體驗】Vivado程序固化

關(guān)于使用232下載固化FPGA程序,尋求外包

Virtex-5中的Microblaze和Capture-Restore過程出現(xiàn)問題

如何使用PowerPC或Microblaze重新配置FPGA?

采用FPGA和MicroBlaze進(jìn)行嵌入式系統(tǒng)設(shè)計

基于MicroBlaze 軟核的FPGA 片上系統(tǒng)設(shè)計

基于MicroBlaze軟核的FPGA片上系統(tǒng)設(shè)計

基于MicroBlaze軟核的FPGA片上系統(tǒng)設(shè)計

基于MicroBlaze處理器的BPIFlash操作

MicroBlaze性能詳解

FPGA+MicroBlaze裸機(jī)程序加載與固化

TI AM57X FPGA MicroBlaze裸機(jī)案例開發(fā)

AMD FPGA中MicroBlaze的固化流程詳解

AMD FPGA的MicroBlaze固化過程詳解

AMD FPGA的MicroBlaze固化過程詳解

評論