關于作者

Abhijit Athavale

Abhijit Athavale是Xilinx公司連接功能解決方案部市場營銷經理,其職責包括為公司的高速串行和并行連接功能產品完成戰略開發、產品定位和營銷計劃。自1995年加入Xilinx以來,他擔任過營銷、應用和軟件工程方面的多種職務。之前,Athavale曾任Meltron公司研發工程師之職,主要設計通信產品。他擁有印度旁尼大學電子工程學士學位和德克薩斯農業大學電子工程碩士學位。他是一名很有造詣的演說家和作家,發表了數篇論文。

I/O性能極限輸入/輸出( I/O)在計算機和工業應用中一直扮演著關鍵角色。但是,隨著信號處理越來越復雜,I/O通信會變得不可靠。在早期的并行I/O總線中,接口的數據對齊問題影響著與外部設備的有效通信。并且,隨著更高的傳輸速度在數字設計中日漸普及,對信號延遲的管理也變得困難重重。

針對I/O的數字設計解決方案數字電路設計者采用了一系列方法來提高信號速度和消除I/O問題。例如,采用差分信號處理來提高芯片間的通信速度。信號同步、源同步和自同步之類的設計方法改善了內部IC(集成電路)通信,在滿足計算機行業所需速度的前提下,提供了可靠的輸入/輸出。

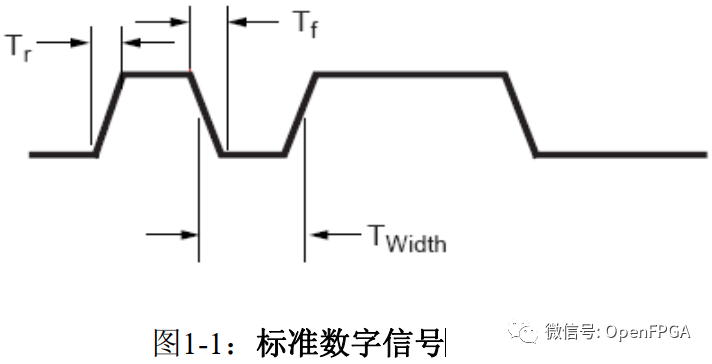

千兆位級串行技術介紹圖1-1為典型的數字信號。

注意圖中列出的時間測量值:

TR = 20 ps

TF = 20 ps

TWIDTH = 0.10 ns

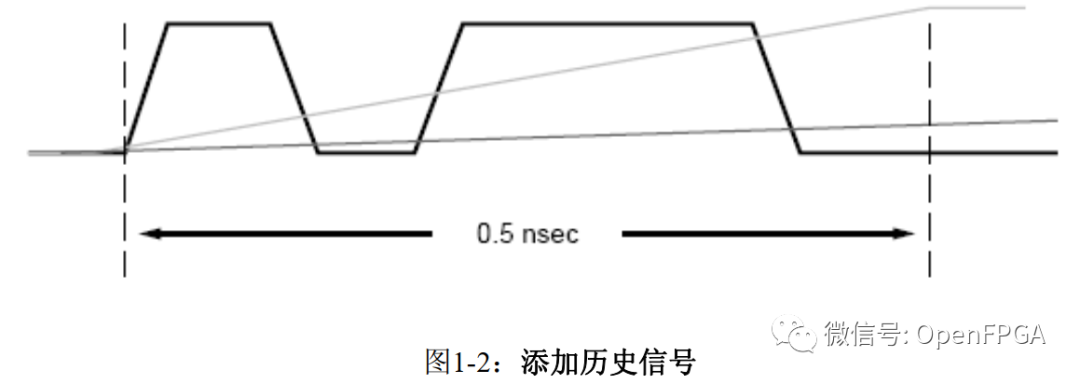

這些值描繪出了一個變化很快的波形。圖1-2添加了作為參考的歷史信號,以便說明該波形的變化有多快 。

大多數信號的上升時間甚至不能在這個信號的五個比特周期內結束。那么,為什么要討論這個信號呢?因為它代表了數字 I/O 領域最熱門的潮流——千兆位級串行通信。

這類信號在市場上引起軒然大波。它被廣泛采用,從局域網( LAN)設備到尖端醫療成像設備,再到先進的戰斗機技術,不一而足。千兆位級信號迅速成為延伸信息化時代的關鍵因素。為了解這一飛速發展的科技進步技術,讓我們首先回顧一下I/O設計的歷史。

設計考慮

通常設計工程師都處于進退兩難的境地。一方面,他希望能堅持使用已經過驗證的、可靠的解決方案,因為這些方案的結果可靠并能夠預見。另一方面,他也必須努力改進各項參數性能,如:數據流、引腳數、電磁干擾(EMI)、成本和背板效率等。那么,他會考慮使用千兆位串行輸入/輸出(I/O)嗎?

千兆位串行I/O的優勢

千兆位串行I/O的主要優勢是什么?答案是:速度。在從片內/片外、板內/板外或盒內/盒外獲取數據時,沒有什么技術可以超過高速串行鏈路。這種技術的線速范圍為1Gb/s~12Gb/s,有效負載范圍為0.8Gb~10Gb,因此可以進行大量的數據傳送。由于引腳數較少、沒有大量的同時開關輸出(SSO)問題、 EMI較低且成本較低,所以高速串行就成為了理所當然的選擇。當需要進行大量數據的快速傳輸時,使用千兆位級收發器(MGT)是個不錯的方法。讓我們首先分析一下千兆位串行I/O的優勢。

MGT:千兆位級收發器——千兆位級串行器/解串器(SERDES)的別名。接收并行數據,并允許在串行鏈路上進行大帶寬數據傳輸。

最大數據流

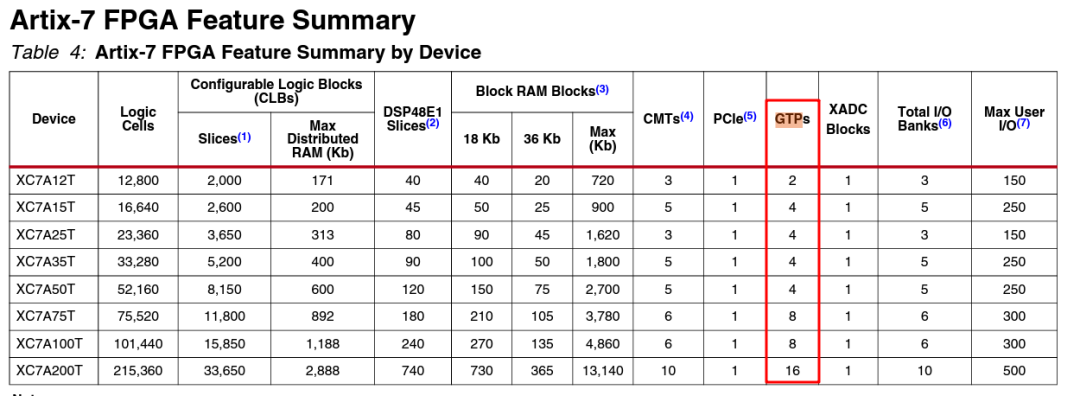

某些大型可編程邏輯器件具有20個或更多個10Gb串行收發器,可以實現總帶寬為200Gb/s的輸入和輸出。不過那只是極端情況,我們來看一個應用實例,它向我們展示了串行I/O的速度是如何幫助系統架構師、電路板設計師和邏輯設計師的。

缺點是什么?

在我們認為千兆位級串行I/O技術出色的近乎不真實之前,來看看它的弊端吧。設計中,首先我 們必須密切注意信號完整性問題。例如,有個供應商報告說,他們第一次試圖將高速、千兆位級串行設計用于某種特定應用時,失敗率為90%。為了提高成功率,我們可能需要進行模擬仿真,并采用更復雜的新型旁路電路。事實上,我們甚至需要對旁路電路進行仿真和建模。而且,阻抗控制的 PC(印刷電路)板、高速連接器和電纜的費用較高。我們必須處理數字仿真中的復雜性和時基較小的問題。并且,在利用預設協議的時候,必須為集成過程計劃時間,并且為協議的開銷安排額外的邏輯電路或 CPU 時鐘周期。

千兆位I/O用于何處?

起初,千兆位級串行器/解串器(SERDES)僅局限于用在電信行業和少數縫隙市場(如廣播視頻)。如今, MGT應用出現在電子行業的各個角落——軍事、醫療、網絡、視頻、通信等等。

MGT也可以用于背板或機箱之間的PCB上。對于電子行業的發展前景而言, MGT至關重要。下面是采用千兆位級SERDES的行業標準示例。

? 光纖通道(FC)

? PCI Express

? RapidIO串行

? 先進交換互連(Advanced Switching Interface)

? 串行ATA

? 1-Gb以太網

? 10-Gb以太網(XAUI)

? Infiniband 1X、 4X、 12X

芯片到芯片SERDES最初用于盒間通信。但是,因為它能出色地處理同一塊電路板上的芯片間通信,因而在市場上引起了轟動。先前,芯片間通信僅采用并行技術。用于串行化和解串行化的邏輯門數量遠遠超過了因引腳數目減少而節省的邏輯門數量。

但是,采用深亞微米結構,就可以在極小的芯片上獲得數量驚人的邏輯門電路,從而使SERDES也能夠以極低的芯片成本實現。除此之外,對I/O帶寬日益增長的需求使得SERDES迅速成為進行芯片間大量數據傳輸的合理選擇。使用SERDES進行芯片間通信具有如下好處:

? 引腳數:更小、更經濟的封裝。

? 引腳數:PCB層數減少。

? 更小的封裝:電路板更小、更經濟;設計更緊湊。

? SSO:較少的引腳和差分信令消除了SSO問題。

? 功耗:通常,高速串行鏈路的功耗要小于并行鏈路。這一特點在一些有源偏置/終端的高速并行標準,例如高速晶體管邏輯(HSTL)中尤為明顯。

? 內含控制線路:通常,并行接口除了數據線外,還需要一些控制線和使能線。大多數協議下使能和控制性能都可以嵌入到串行鏈路中。

還是老規矩,原文很長 很長 很長。。。。

鏈接: https://pan.baidu.com/s/1K0AVtbrwTJ7SzXbwnUWTWQ

提取碼: jx35

審核編輯:黃飛

-

以太網

+關注

關注

40文章

5594瀏覽量

174968 -

數據傳輸

+關注

關注

9文章

2005瀏覽量

65758 -

信號處理

+關注

關注

48文章

1055瀏覽量

103933 -

邏輯門電路

+關注

關注

2文章

67瀏覽量

12207

原文標題:輕松實現高速串行I_O,有助于理解GTP/GTX工作原理

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA設計之GTP、GTX、GTH以及GTZ四種串行高速收發器

RocketIO高速串行接口

問一下路過的FPGA大神,ADI的參考設計用的高速通道是GTX,GTH,怎么移植到高速通道是GTP的FPGA里?跪求!!!

在Virtex-5/6 GTP / GTX收發器中如何實現JTAG

怎么實現RocketIOTM GTP在串行高速接口中的位寬設計?

RocketIOTM GTP在串行高速接口中的位寬設計

基于Virtex-5 RocketI0TM GTP收發器實現串行高速接口的開發應用

GTX/GTH/GTY/GTP/GTZ/GTM有什么區別

高速串行I/O輕松實現,GTP/GTX工作原理詳解

高速串行I/O輕松實現,GTP/GTX工作原理詳解

評論