本文接著解析SDF3.0的Timing Checks Entries、Timing Environment Entries兩個(gè)部分。

(一)SDF3.0 Timing Checks主要分以下兩種:

VCS/NC-Verilog后仿真在timing violation時(shí)報(bào)出warning;

Timing Sign-Off工具報(bào)出timing check violations;

以時(shí)序分析工具Sign-Off為主,后仿為輔,SDF3.0 Timing Checks具體的類型如下:

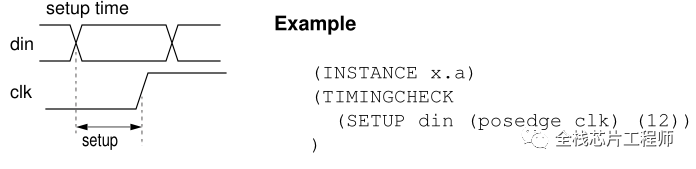

Setup Timing Check

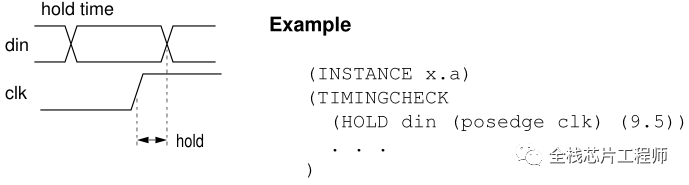

Hold Timing Check

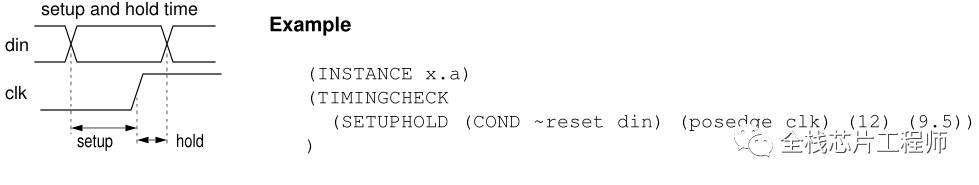

SetupHold Timing Check

注意,示例中~reset必須為真(Ture),timing check才會(huì)進(jìn)行,此外,12是建立時(shí)間要求,9.5是保持時(shí)間要求。

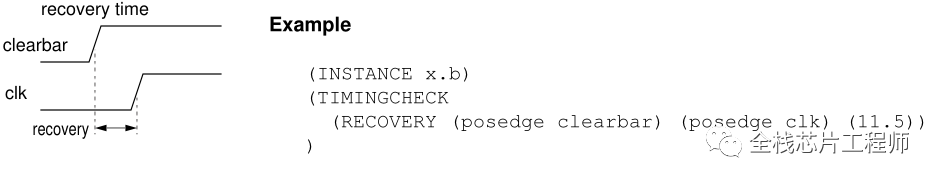

Recovery Timing Check

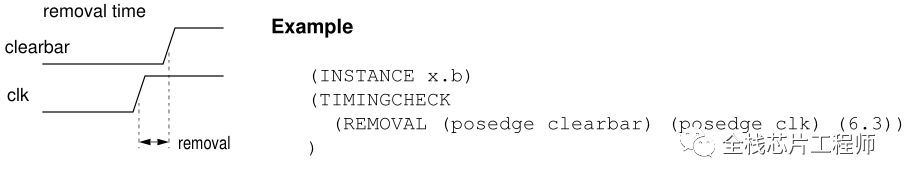

Removal Timing Check

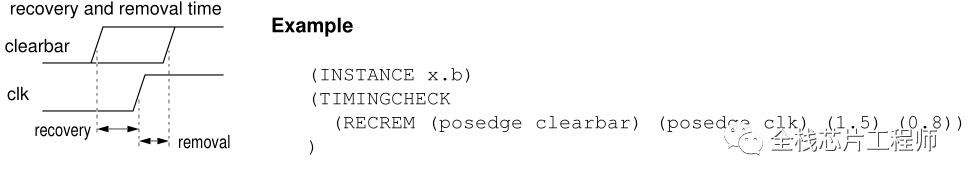

Recovery/Removal Timing Check

示例中,recovery time為1.5個(gè)time unit,removal time為0.8個(gè)time unit。

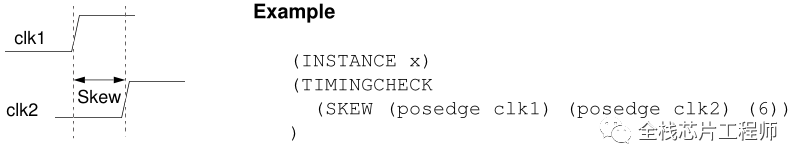

Skew Timing Check

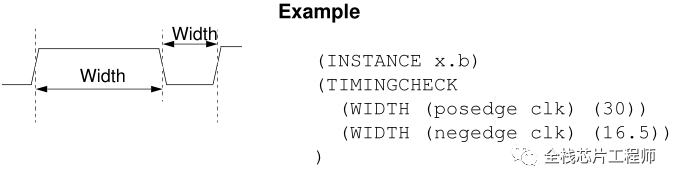

Width Timing Check

示例中,第一個(gè)minimum pulse width檢查是posedge clock驅(qū)動(dòng)的high phase;第二個(gè)minimum pulse width檢查是negedge clock驅(qū)動(dòng)的low phase;

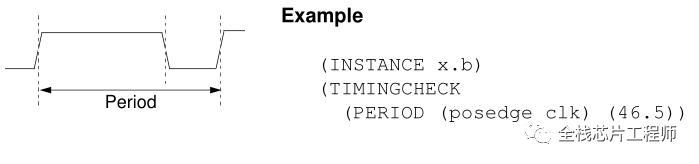

Period Timing Check

示例中,兩個(gè)連續(xù)上升沿之間或兩個(gè)連續(xù)下降沿之間的最小Cycle時(shí)間。

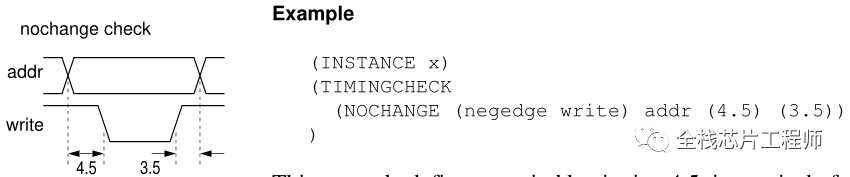

No Change Timing Check

示例中,addr提前write下降沿4.5個(gè)time unit, addr晚于write上升沿3.5個(gè)time unit。

(二)SDF3.0 Timing Environment Entries

SDF3.0 Timing Environment Entries分成Constraints與Timing Environment兩個(gè)部分,首先解析Constraints。

1.Constraints

首先,SDF3.0 Timing Environment包括以下幾類constraints:

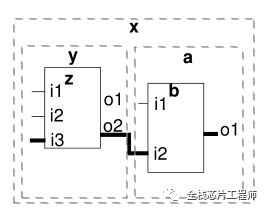

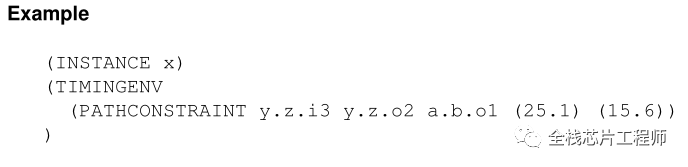

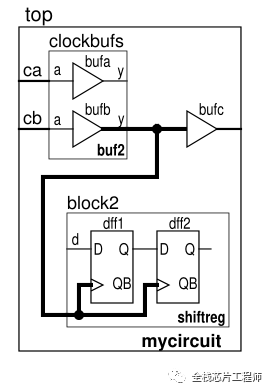

a)Path Constraint 針對timing analysis中發(fā)現(xiàn)的關(guān)鍵路徑添加的約束,PR工具可以利用這些約束優(yōu)化physical design,該約束指定路徑的最大延時(shí); 如下圖, y.z.i3是path起點(diǎn),a.b.o1是path終點(diǎn),25.1是起點(diǎn)和終點(diǎn)之間的maximum rise delay,15.6是起點(diǎn)和終點(diǎn)之間的maximum fall delay。

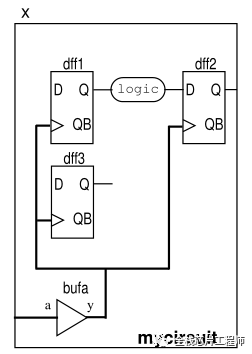

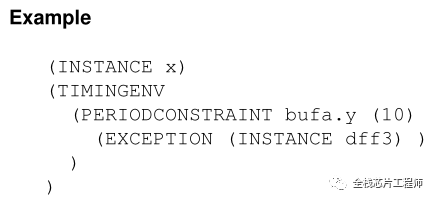

b)Period Constraint

時(shí)鐘樹上common clock到其驅(qū)動(dòng)的leaf cell的路徑的最大延遲約束。

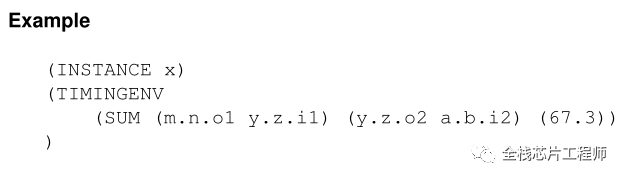

c)Sum Constraint

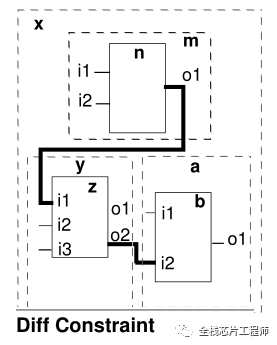

顧名思義,指的是幾條路徑的延時(shí)之和。示例中,約束兩條net的延時(shí)之和小于67.3個(gè)time unit。

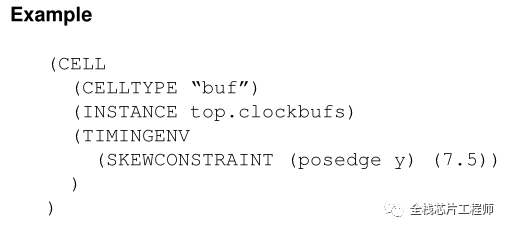

d)Skew Constraint

SDF3.0 Timing Environment Entries分成Constraints與Timing Environment兩個(gè)部分,上文解析了Constraints,現(xiàn)在解析Timing Environment。Timing Environment包含以下4點(diǎn)約束

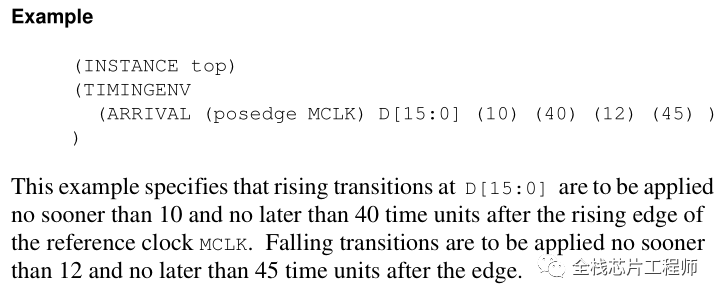

a)Arrival Time

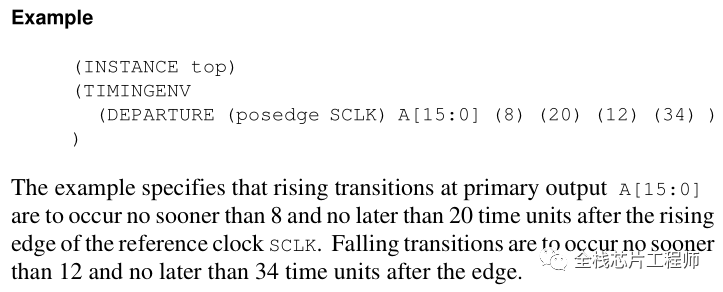

b)Departure Time

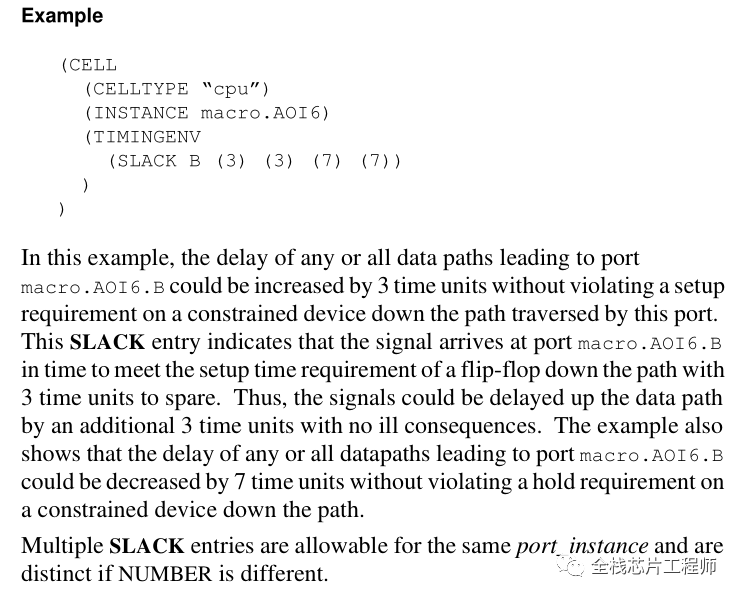

c)Slack Time

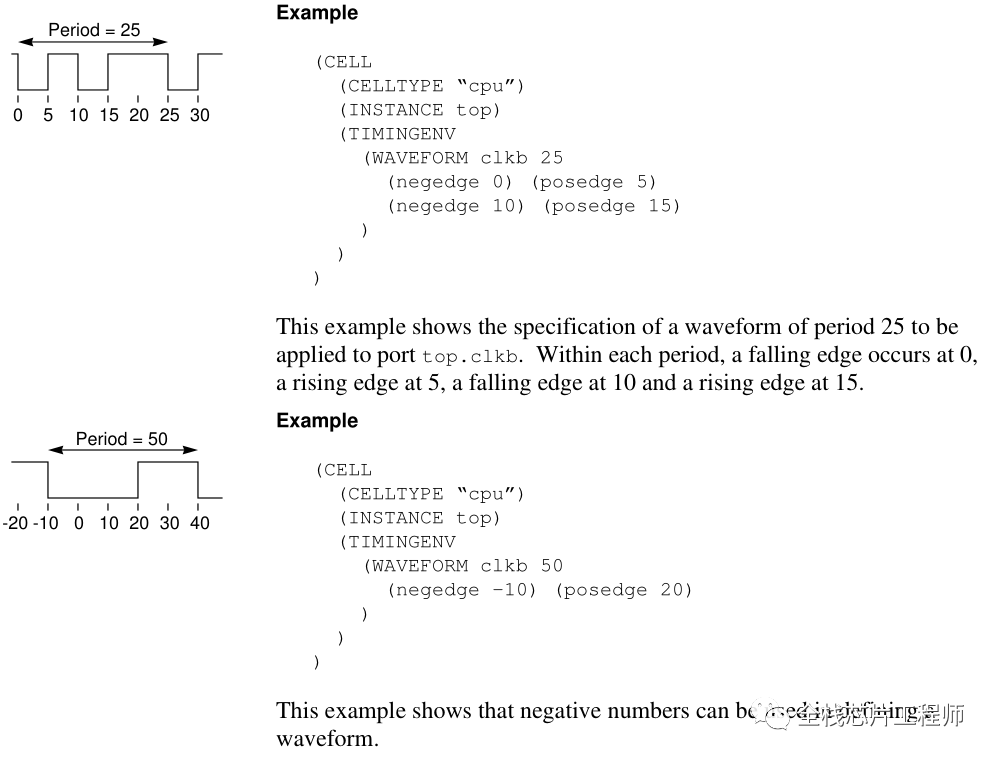

d)Waveform Specification

審核編輯:劉清

-

仿真

+關(guān)注

關(guān)注

52文章

4290瀏覽量

135918 -

VCS

+關(guān)注

關(guān)注

0文章

80瀏覽量

9934 -

時(shí)序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

23830 -

時(shí)鐘樹

+關(guān)注

關(guān)注

0文章

56瀏覽量

11049

原文標(biāo)題:芯片后仿之SDF 3.0解析(三)

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

我后仿出現(xiàn)了10種警告。。。求助

運(yùn)行后實(shí)現(xiàn)時(shí)序仿真后重新生成sdf文件

如何將PT產(chǎn)生的SDF文件反標(biāo)設(shè)計(jì)進(jìn)行后仿真?

怎樣用calibreview格式提取參數(shù)做后仿?有哪幾種方法

NodeMCU V3.0 Arduino開發(fā)之點(diǎn)燈測試程序

STM8S全解析之系列文章3---STM8S芯片配置,軟件框架搭建

ZigBee3.0數(shù)據(jù)包解析

Python在IC中的應(yīng)用——文本處理

什么是數(shù)字后仿?淺談芯片數(shù)字后仿的那些事

解析SDF的Header Section信息與Cell Entries信息

詳解芯片SDF文件 MCU芯片全流程設(shè)計(jì)

芯片后仿及SDF反標(biāo)

芯片后仿之SDF 3.0解析

芯片后仿真要點(diǎn)

芯片后仿之SDF 3.0解析(三)

芯片后仿之SDF 3.0解析(三)

評論