上拉電阻有助于降低系統的總功耗,同時保持電路的功能性和穩定性。那么上拉電阻如何實現低功耗設計呢?

以下是上拉電阻實現低功耗設計的幾種方法:

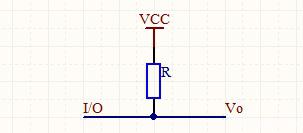

選擇合適的上拉電阻值:

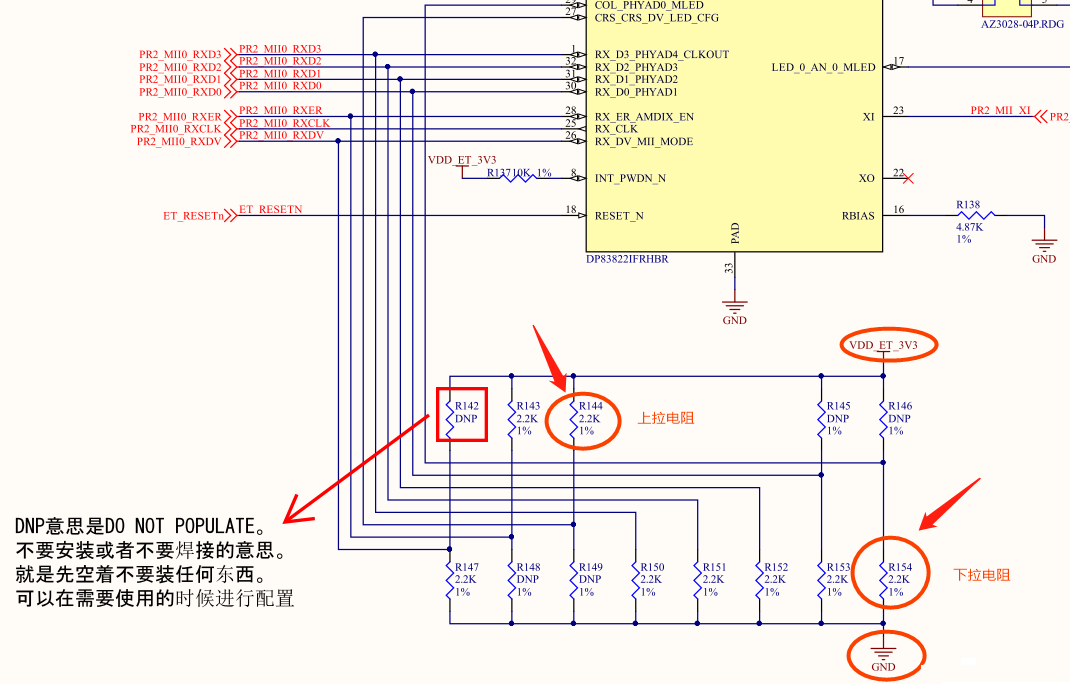

功耗與電阻值成反比關系,一個較大的上拉電阻會限制流過電阻的電流,從而減少功耗。但同時,太大的上拉電阻會影響信號上升時間和下降時間,進而影響電路性能。因此,需要根據具體電路特性和信號頻率來選擇一個折中的電阻值。

動態控制上拉電阻:

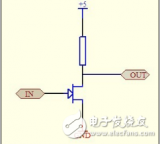

在能夠容忍信號懸空的應用中,可以通過開關或晶體管動態地斷開上拉電阻,僅在必要時才將上拉電阻接入電路,其余時間將其從電源中斷開以節省能源。

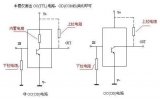

利用開漏(Open-Drain)/開集(Open-Collector)輸出:

開漏/開集輸出不主動提供高電平,而是通過外部的上拉電阻來實現。當總線處于空閑狀態時,由于上拉電阻的存在,不需要額外的能量就能維持高電平,這有助于降低靜態功耗。

使用可編程上拉電阻:

一些現代微控制器和接口提供了可編程的上拉電阻選項,允許軟件控制上拉電阻的啟用與禁用。這為基于實際運行情況調整功耗提供了靈活性。

優化I/O端口配置:

對于未使用的I/O端口,正確配置其為輸入并使用上拉電阻可以避免潛在的電源損耗,同時防止因懸空輸入而引入的不確定性。

考慮信號傳輸質量與功耗之間的權衡:

在設計通信總線時,如SPI、I2C等,需要平衡總線的電容負載與上拉電阻的大小,以確保信號質量和功耗之間的最佳折中。

綜上所述,通過以上策略,設計師可以在保證電路正常工作的同時最小化上拉電阻引起的功耗。這些方法需要在系統設計初期就進行仔細考慮,并在實驗和調試階段進行驗證和優化,以確保達到預期的低功耗效果。

-

電流

+關注

關注

40文章

7125瀏覽量

134596 -

上拉電阻

+關注

關注

5文章

366瀏覽量

31115 -

控制器

+關注

關注

114文章

17054瀏覽量

183593

發布評論請先 登錄

如何選擇正確值的上拉電阻和下拉電阻?

上拉電阻的作用

STM8L調低功耗方法

上拉電阻如何實現低功耗設計

上拉電阻如何實現低功耗設計

評論