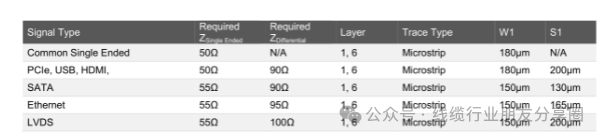

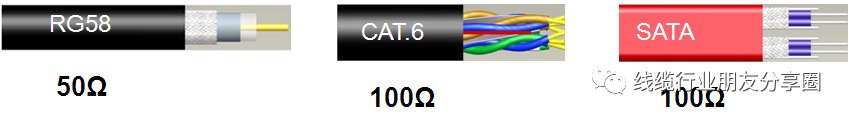

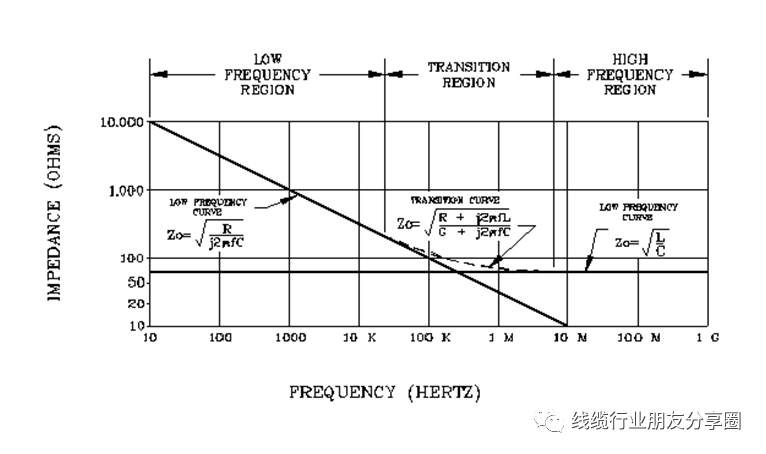

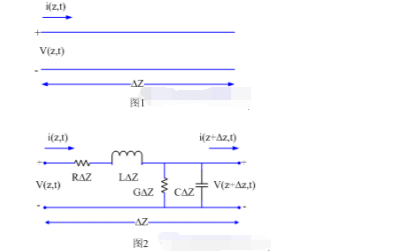

特征阻抗這個名詞是對于交流信號(或者說高頻信號)來說的;特征阻抗屬于長線傳輸中的一個概念,信號在傳輸線中傳輸的過程中,在信號到達的一個點,傳輸線和參考平面之間會形成電場,由于電場的存在,會產生一個瞬間的小電流,這個小電流在傳輸線中的每一點都存在。同時信號也存在一定的電壓,這樣在信號傳輸過程中,傳輸線的每一點就會等效成一個電阻,這個電阻就是我們提到的傳輸線的特征阻抗。如今,高速系統面臨著許多必須在同一堆疊中實現的同步阻抗要求 ;如以太網的100歐姆差分阻抗,90歐姆的USB,85歐姆的PCIe以及無數的單端DDR要求。我們希望遵循規范,以正確的阻抗選擇組件和布線走線。然而,有時也存在一些障礙——首選元件不是85歐姆,或者上游封裝是另一種阻抗。規范怎么說?我上傳了如下圖片有常用接口的阻抗要求,可以參考一下;

什么樣的信號線需要50歐姆阻抗,85歐姆阻抗,90歐姆阻抗,100歐姆阻抗

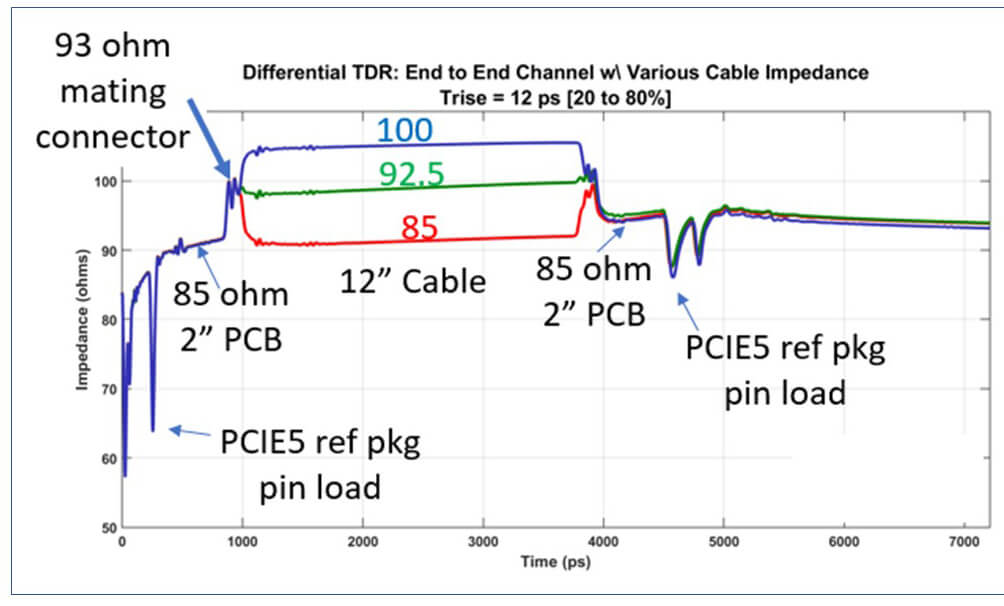

我們知道,較高的阻抗,插入損耗會比較好(衰減會比較小),之前我們做過數據分析,85歐姆和100歐姆阻抗之間的損耗差高達14%。而較高阻抗的PCB確又有具有更大的損耗;也就是說,阻抗和損耗之間的關系與PCB關系又成反比。舉例:目前PCIE平行對的線材阻抗有85歐姆和100歐姆兩種,看了一個關于PCI Express Layout gudie的文檔,其中關于阻抗的要求PCI Express link traces must maintain 100 ? differential / 60 ? single-ended impedancefor 4-layer or 6-layer boards; and 85 ? differential / 55 ? single-ended impedance for 8-layer or 10-layer boards. 這里就提到PCB板層不一樣會有不同的阻抗要求;按照行業數據分析,PCB板子的層數多了,層間距小了,要滿足原來的阻抗要求就可能導致走線太細,不能滿足工藝要求,所以適當地降低阻抗目標值來保證有足夠的走線寬度。這個主要是方便布線;4~6層主力布線層是top/botm,85Ω在表層線寬/間距會很大,100Ω的就會好很多。降低阻抗后,負載變重,抗干擾能力要強一點。4到6層板布線都在外層,需要考慮抗干擾能力;強制疊層和線寬間距的情況下,8層板厚度減少,阻抗就變低.

阻抗的概念和重要性

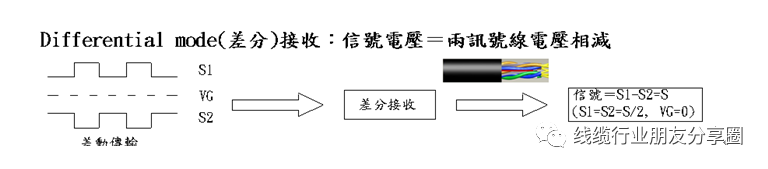

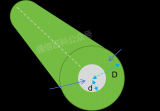

在測同一被測線材時,其阻抗會因在該被測線材上傳輸的信號型式不同,而分為單端阻抗,同模(共模)阻抗及差分阻抗,其差異主要表現在測試的信號條件上。將傳輸線始端的輸入阻抗簡稱為阻抗;將信號隨時遇到的及時阻抗稱為瞬時阻抗如果傳輸線具有恒定不變的瞬時阻抗,就稱之為傳輸線的特性阻抗;和電阻,電容,電感一樣,傳輸線也是一種理想的電路元件,但是其特性卻大不相同,用于仿真效果較好,但電路概念卻比較復雜;依傳輸的訊號型式不同.單端阻抗 Zse (Single Ended):差動阻抗 Zdiff (Differential Mode);同模阻抗 Zcom (Common Mode).

早期的數字總線大部分使用單端信號做信號傳輸,如TTL/CMOS信號都是單端信號。所謂單端信號,是指用一根信號線的高低電平的變化來進行0、1信息的傳輸,這個電平的高低變化是相對于其公共的參考地平面的。單端信號由于結構簡單,可以用簡單的晶體管電路實現,而且集成度高、功耗低,因此在數字電路中得到最廣泛的應用。

當信號傳輸速率更高時,為了減小信號的跳變時間和功耗,信號的幅度一般都會相應減小。比如以前大量使用的5V的TTL信號現在使用越來越少,更多使用的是3.3V/2.5V/1.8V/1.5V/1.2V的LVTTL電平,但是信號幅度減小帶來的問題是對噪聲的容忍能力會變差一些。進一步的,很多數字總線現在需要傳輸更長的距離,從原來芯片間的互連變成板卡間的互連甚至設備間的互連,信號穿過不同的設備時會受到更多噪聲的干擾。更極端的情況是收發端的參考地平面可能也不是等電位的。

因此,當信號速率變高、傳輸距離變長后仍然使用單端的方式進行信號傳輸會帶來很大的問題。為了提高信號在高速率、長距離情況下傳輸的可靠性,大部分高速的數字串行總線都會采用差分信號進行信號傳輸。差分信號是用一對反相的差分線進行信號傳輸,發送端采用差分的發送器,接收端相應采用差分的接收器。采用差分傳輸方式后,由于差分線對里正負信號的走線是緊密耦合在一起的,所以外界噪聲對于兩根信號線的影響是一樣的。而在接收端,由于其接收器是把正負信號相減的結果做為邏輯判決的依據,因此即使信號線上有嚴重的共模噪聲或者地電平的波動,對于最后的邏輯電平判決影響很小。

相對于單端傳輸方式,差分傳輸方式的抗干擾、抗共模噪聲能力大大提高。采用差分方式進行信號傳輸會使得收發端的電路變得復雜,系統的功耗也隨之上升,但是由于其優異的抗干擾能力以及可靠的傳輸特性,使得差分傳輸方式在需要進行高速數字信號的傳輸或者惡劣工作環境的領域得到了廣泛的應用,如LVDS、PCI-E、SATA、USB、1394、CAN、Flexray等總線都是采用差分的信號傳輸方式。

一般而言儀器的端口是以單端50Ω的阻抗最為常見。如欲以NA量測“差分訊號”時,需經由Bulan轉換將NA的“單端訊號”轉換成差分訊號。TDR的“單端訊號”轉成“差分訊號”或“同模訊號”時,只需設定儀器端口即可。其實,阻抗匹配的概念并不止于此,如果將兩段均勻的同軸電纜連接起來,在連接點處如果“加工”工藝視屏高,金屬銜接平順,沒有出現微觀結構意義上的阻抗突變現象,則我們也把這兩段同軸線的連接也稱作匹配。

推而廣之,凡是阻抗連續的連接點我們都說它們是“匹配”的。按照這個思路,我們就知道通常在雙絞線和模塊的連接點處,阻抗是很可能有“失配”現象存在的,一條布線鏈路中的接插件和連接件所在的位置經常也是阻抗不連續的位置(或者說是阻抗失配的位置)。不連續的原因主要是傳輸線的幾何結構或材質(包含絕緣介質的材質)發生了突變。凡是阻抗不連續點,也“一定是”一個信號能量的反射點(回波源)。對于產品設計和生產商來說,就是要制作出連接點阻抗盡量平順連續的產品 —模塊、跳線、各種工業連接器、各種異型非標接插件等等。

-

CMOS

+關注

關注

58文章

5737瀏覽量

236159 -

PCB板

+關注

關注

27文章

1452瀏覽量

52000 -

DDR

+關注

關注

11文章

716瀏覽量

65564 -

TTL電平

+關注

關注

1文章

116瀏覽量

12088 -

差分阻抗

+關注

關注

1文章

26瀏覽量

10407

原文標題:什么樣的信號線需要50歐姆阻抗,85歐姆阻抗,90歐姆阻抗,100歐姆阻抗,阻抗的重要性?

文章出處:【微信號:線纜行業朋友分享圈,微信公眾號:線纜行業朋友分享圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AppCAD計算天線信號線特性阻抗

你能想象嗎,傳輸線能控到多少阻抗還要看隔壁信號線的臉色?

TE Connectivity的Z-PackTinMan100歐姆和85歐姆連接器,占位阻抗易匹配

如何使用AppCAD實現計算天線信號線特性阻抗

什么樣的信號線需要50歐姆阻抗,85歐姆阻抗?

什么樣的信號線需要50歐姆阻抗,85歐姆阻抗?

評論