存算一體技術發展歷程

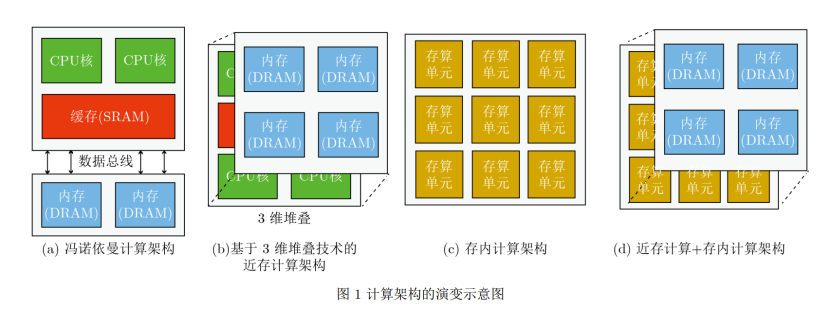

存算一體包括近存計算與存內計算,其概念最早在1969年被提出[9,10],后續各國學者在電路、算法、計算架構、操作系統、系統應用等層面開展了一系列相關研究。例如, 1997年,文獻[11]展示了一種智能內存(Intelligent RAM)方案,其將處理器和DRAM集成在單顆芯片上,算力可達到當時最先進的Cray向量處理器(Cray T-90)的5倍。 1999年,文獻[12]提出了一種嵌入計算功能的靈活內存(FlexRAM)方案,仿真結果表明該芯片架構可使計算性能提升25~40倍。但是,早期由于缺少大數據

處理的應用需求,加之芯片的制造成本昂貴、設計復雜,存算一體技術多年來僅停留在研究階段。

2015年以來,由于摩爾定律的逐漸失效與馮.諾依曼架構的局限性越來越明顯,加之大數據應用的驅動,工藝水平的不斷提高,存算一體技術重新受到關注,并成為研究熱潮。例如,在2017年微處理器頂級年會(Micro2017)上,眾多高校和企業都推

出了他們的存算一體芯片或系統原型[13–15],包括蘇黎世聯邦理工學院、加利福尼亞大學圣巴巴拉分校、英偉達、英特爾、微軟、三星等。 2019年,文獻[16]提出的SRAM存算一體芯片可實現二值權重的神經網絡卷積計算。 2020年,文獻[17]展示了一

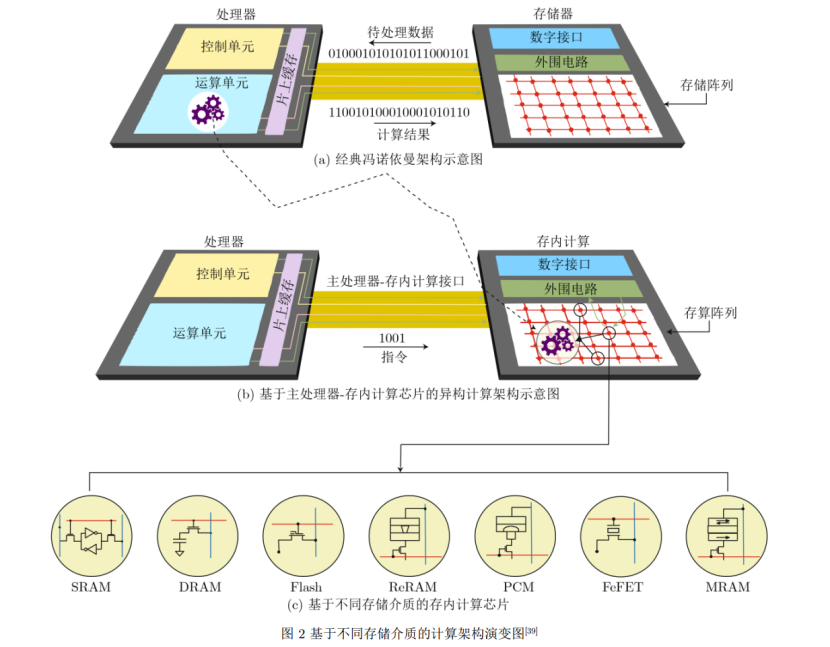

款ReRAM存算一體芯片,在降低計算延遲的同時大幅提升能效。 2021年,文獻[18]提出三值DRAM存算一體架構實現神經網絡運算加速。 2022年,文獻[19]提出了多芯粒的存算一體集成芯片。文獻[20–24]基于SRAM/ReRAM發表了一系列存算一體器件、芯片與系統相關的研究成果。迄今,基于SRAM,DRAM, Flash, ReRAM, PCM, FeFET, MRAM等各類存儲介質,涌現出了一系列相關研究工作[25–38],

存算一體芯片研究百花齊放,如圖2所示。特別地, 2021-2022年,被譽為芯片領域奧林匹克的頂級國際會議ISSCC收錄了存算一體相關論文20余篇,研究單位包括三星、臺積電、麻省理工學院、普林斯頓大學、清華大學、北京大學、復旦大學、

中國科學院大學等國際頂尖高校和企業。

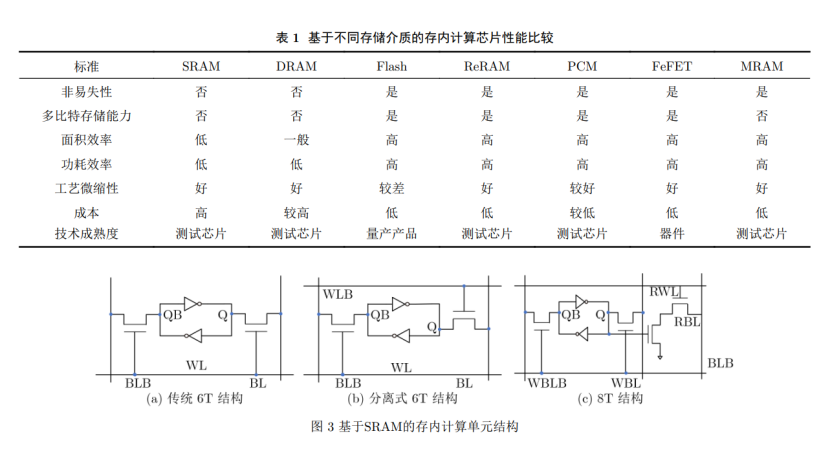

雖然基于各類存儲介質的存算一體芯片研究百花齊放,但是各自在大規模產業化之前都仍然面臨一些問題和挑戰。更具體地, SRAM工藝成熟,且微縮性好;但是屬于易失性存儲器(掉電數據丟失),且單元面積較大,成本較高,難以通過較低成本實現大規模、大算力存內計算芯片。 DRAM工藝成熟,且單元面積較小;但同屬易失性存儲器,需定期刷新,且存在漏電問題,難以實現高精度存內計算芯片,近年來被廣泛應用于近存計算。ReRAM屬于非易失性存儲器,且能夠實現大規模交叉點陣列,是未來實現存內計算芯片的潛力介質之一;但是目前的工藝尚不成熟,存儲單元的多比特精度較低(低于8 bit),且一致性/魯棒性較差。

PCM屬于非易失性存儲器,且能夠實現大規模交叉點陣列;但是功耗較大,速度較慢,耐久性較差。 FeFET可實現非易失性存儲,且能實現交叉點陣列;但是目前的工藝也尚不成熟。 MRAM是非易失性存儲器,具有高耐久性、高速度、低功耗等優點,工藝相對較成熟,擴展性較好,但是器件的阻值(約幾千歐姆)與高低阻值比率(約250%)相對較小,在實現多比特存內計算芯片方面具有一定挑戰。 Flash是非易失性存儲器,掉電數據不丟失,且工藝成熟,成本低,已實現量產芯片(如Mythic的M1076,知存科技的WTM2101),但在微縮性方面存在一定挑戰;幸運的是,隨著2.5D/3D先進封裝技術的快速發展,可以實現與先進邏輯工藝的兼容集成。綜上,基于不同存儲器介質的存算一體芯片之間的性能比較如表1所示。

存算一體技術在產業界的進展同樣十分迅速,

國內外多家企業在積極研發,例如我國臺灣的臺積電,韓國三星、日本東芝、美國Mythic,國內的知存科技等。但是當前最接近產業化的主要是臺積電、 Mythic和知存科技。從2019年至今,臺積電得益于其強大的工藝能力,已基于SRAM與ReRAM發表了一系列存算一體芯片研究成果[40,41],具備量產代工能力。 Mythic已于2021年推出基于NOR Flash

的存內計算量產芯片M1076,可支持80 MB神經網絡權重,單個芯片算力達到25 TOPS,主要面向邊緣側智能場景。知存科技于2021年推出基于NOR Flash的存內計算SoC芯片WTM2101,其算力比市場同類芯片高出兩個數量級,功耗低于1 mW,主要面向端側低功耗、低成本應用場景。

存內計算芯片研究現狀

由于計算范式和存儲介質的不同,存內計算芯片可以有不同的分類方法。根據計算范式的不同,主要分為模擬式和數字式兩種。模擬式存內計算是指存儲單元內部或陣列周邊的信號以模擬信號的方式進行操作,數字式存內計算是指在實際運算過程中,存儲單元內部或陣列周邊的信號以數字信號的方式進行操作。其中,諸多的研究工作同時包含了

模擬和數字兩種運算方式。同時,根據存儲介質的不同,存內計算芯片可分為基于傳統存儲器和基于新型非易失性存儲器兩種。傳統存儲器包括SRAM,DRAM和Flash等;新型非易失性存儲器包括ReRAM,PCM, FeFET, MRAM等。其中,距離產業化較近的是基于NOR Flash和基于SRAM的存內計算芯片。

SRAM存內計算

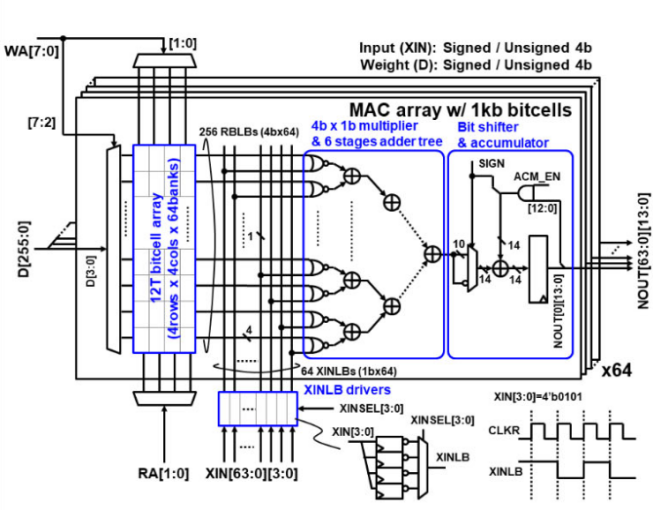

基于SRAM的存內計算芯片以典型的6T(6-Transistor)基本單元為基礎,如圖3(a)所示。由于SRAM是二值存儲器,二值乘累加運算等效于同或累加運算,可以用于二值神經網絡運算,其核心思想是網絡權重存儲于SRAM單元中,激勵信號從字線給入,最終利用外圍電路實現同或累加運算,結果通過計數器或模擬電流/電壓輸出。如果要實現

多比特精度運算,通常需要多個單元進行拼接,這不可避免地會帶來面積開銷。對6T基本單元的一個簡單修改是將字線進行拆分,如圖3(b)所示。此外,為了解決讀寫干擾問題,可以采用8T基本單元,但明顯增加了布局面積,如圖3(c)所示。基于SRAM

的存內計算技術由于其工藝成熟度與良好的微縮性,受到業界的高度關注,近幾年的ISSCC會議上連續報道了多篇相關論文。例如2021年,存內計算共有兩個分論壇,共收錄8篇論文,其中5篇是SRAM存內計算芯片。在2022年的ISSCC中,北京大學提出了一種基于動態邏輯且無模數轉換器的SRAM存內計算芯片[42]。 SRAM存內計算技術的主

要應用難點是在保證運算精度的前提下,實現高算力和小面積。

DRAM存內計算

基于DRAM的存內計算芯片層次結構可分為陣列、子陣列和單元,一組陣列由若干子陣列和用于讀寫操作的相關外圍電路組成,而子陣列則包含若干行1T1C(1-Transistor-1-Capacitor)單元、感知放大器和本地解碼器。其基本原理是利用DRAM單元之間的電荷共享機制[13,43]。如圖4所示為一種典型實現方案[43],當多行單元同時被選通時,不同單元之間因為存儲數據的不同會產生電荷交換共享,從而實現邏輯運算。 DRAM存內計算方案的主要難點有二:一是其本身為易失性存儲器,計算操作

會破壞數據,需要每次運算后進行刷新,帶來功耗問題;二是實現大陣列運算時難以保證運算精度。

ReRAM/PCM存內計算

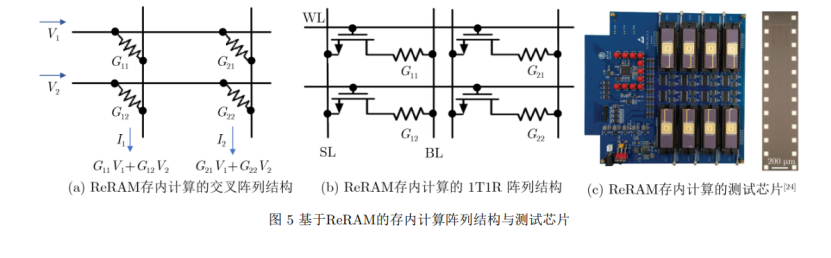

ReRAM/PCM存內計算的基本原理是利用存儲單元的模擬多比特特性,通過基于電流/電壓的歐姆定律與基爾霍夫定律進行矩陣乘加運算,主要有1T1R (1-transistor-1-resistance)結構和交叉陣列結構兩種實現方案,如圖5(a)和圖5(b)所示。 ReRAM能夠實現大規模交叉點陣列,使其成為學術界的熱點研究方向。自2008年ReRAM首次實驗發現以來,基于ReRAM的存內計算研究就層出不窮。

尤其2020年,清華大學研發出基于多個ReRAM陣列的存內計算系統,該系統在手寫數字集上的識別準確率達到96.19%,與軟件的識別準確率相當,證明了存內計算架構全硬件實現的可行性,其測試芯片如圖5(c)所示[24]。 ReRAM存內計算技術未來具有

非常大的應用潛力,目前的主要難點在于工藝尚不太成熟,多比特精度實現較困難,一致性/魯棒性較差。

MRAM存內計算

MRAM存內計算主要有兩種技術方案: (1) 基于讀/寫操作的數字式存內計算; (2) 基于基爾霍夫電流定律和歐姆定律的模擬式存內計算。早期的MRAM存內計算大多基于數字式方案,如2015年日本東北大學提出基于讀操作實現多種布爾邏輯并流片驗證,獲得了48.3%的能效提升[44]; 2019年,北京航空航天大學提出基于單次寫操作的數字式MRAM存內計算方案,實現計算結果原位存儲的同時降低了延時和功耗 [45–47]。基于MRAM的模擬式存內計算的難點在于器件的阻值(約幾千歐姆)與高低阻值比率(約250%)相對較小,難以實現多比特精度。近年來,得益于計算范式、器件、電路的多層次創新突破, MRAM模擬存內計算發展迅速。 2021年,美國普林斯頓大學通過電路級優化,流片驗證了第一款基于STT-MRAM的模擬存內計算硬核[ 4 8 ];2022年,韓國三星公司在Nature期刊上發表了基于電阻累加方案的MRAM模擬存內計算芯片原型,并實現了最高405 TOPS/W的能效比[49],其陣列的布局圖、顯微圖和結構如圖6所示。

NOR Flash存內計算

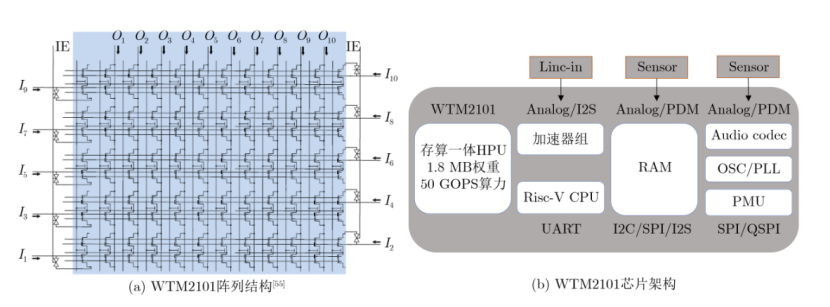

基于NOR Flash的存內計算技術原理與ReRAM類似,如圖7(a)所示。目前, NOR Flash存內計算芯片技術相對較成熟,已于2021年實現量產。美國的Mythic和國內的知存科技都已推出NOR Flash存內計算芯片產品,其中, Mythic推出了M1076芯片(如圖7(b)所示),知存科技推出了WTM2101量產SoC芯片(如圖7(c)所示)。

基于其他介質的存內計算

此外,學術界還發表了基于NAND Flash以及新型納米器件(如FeFET、斯格明子等)的存內計算相關工作,其基本原理與上述方案類似,但是目前僅僅是概念階段,這里不再詳述。

存內計算芯片應用現狀:以WTM2101

為例

隨著萬物互聯的不斷發展,智能設備主要包括3類:云端、邊緣端和終端。云端設備的要求主要是高算力、大吞吐量、高可靠性,當前的存內計算進展還難以滿足需求。邊緣端設備,如安防、自動駕駛等,對算力、時延、功耗、安全性等具有相對綜合的需求;終端設備則主要關注功耗、成本和隱私。目前存內計算芯片應用方面尚處于起步階段,

本節以知存科技推出的量產SoC芯片WTM2101為例,討論其在邊緣端和終端的應用,側重于語音場景的介紹,同時介紹其核心電路與芯片架構、性能與應用場景。

核心電路與芯片架構

在NOR Flash存內計算芯片當中,向量-矩陣乘法運算基于電流/電壓的跨導與基爾霍夫定律進行物理實現,如圖7(a)所示。因此,其核心是設計NOR Flash單元陣列以滿足大規模高能效向量-矩陣乘法運算。同時,在核心電路的基礎上,根據算法特征設計芯片架構,以充分利用神經網絡數據流式的特點來實現芯片的并行化與流水線。在傳統NOR Flash陣列中,對某一個特定器件編程會不可避免地改變同一行上其他器件的狀態,稱為行干擾。作為存內計算應用, NOR Flash編程需要逐個器件進行單獨操作,每個器件存儲8 bit(256個量化狀態)以上的信息,微小的干擾就將導致狀態的變化。因此,需要抗編程干擾陣列結構來消除編程干擾。除此之外, NOR Flash基于浮柵中電子的數量

來存儲信息,隨著時間的增加,電子會泄露,造成閾值電壓漂移。作為存儲應用的NOR Flash器件通常只保存1~2 bit信息(對應2~4個不同狀態),狀態之間的裕量比較大,不用特殊設計即可保存信息10年以上。但在存內計算應用中, NOR Flash器件需要存儲8 bit(256個不同狀態)以上信息,狀態之間的裕量非常小,且通過整個陣列同時工作。因此,閾值電壓漂移的影響非常大。 WTM2101通過特殊的電路設計抑制閾值電壓漂移對計算精度的影響。此外,為了同時實現低功耗計算與低功耗控制, WTM2101結合了RISC-V指令集與NOR Flash存內計算陣列,其陣列結構與芯片架構如圖8所示,包括1.8 MB NOR Flash存內計算陣列,一個RISC-V核,一個數字計算加速器組, 320 kB

RAM以及多種外設接口。

性能與應用場景

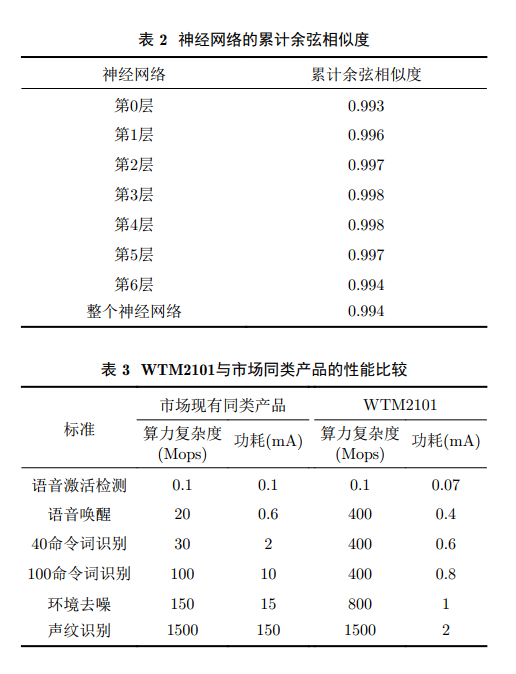

WTM2101基于40 nm工藝進行流片,單個NOR Flash 器件能夠存儲8 bit權重,因此可以進行8 bit精度的矩陣乘加運算。如圖9所示為輸入信號與輸出電流之間的關系,單元和芯片均呈現良好的線性關系。 WTM2101具有4大優勢特點: (1)基于存內計算架構,可高效地實現神經網絡語音激活檢測和上百條語音命令詞識別。 (2)以超低功耗實現神經網絡環境降噪算法、健康監測與分析算法。(3)典型應用場景下,工作功耗均在微瓦級別。(4)采用極小封裝尺寸。基于以上優勢特點, WTM2101 可應用于智能可穿戴設備、智能家居、安防監控、玩具機器人等;適應多種應用,如語音識別、語音降噪/增強、輕量級視覺識別、健康監測和聲紋識別等。如圖10所示為搭載WTM2101的耳機產品及

其自動化部署流程。如圖11所示為基于WTM2101的耳機降噪前后效果的波形和頻譜對比。如表2所示為部署在WTM2101的神經網絡的各層累計余弦相似度(指存內計算相對于8-bit量化計算的余弦相似度),可以看到經過8層神經網絡計算,余弦相似度依舊保持在0.99以上。如表3所示為WTM2101在語音激活檢測、語音喚醒、命令詞識別、環境去噪和聲紋識別方面與市場同類產品的對比。

存內計算芯片的應用前景與挑戰

存內計算芯片技術,因其高算力、低功耗、低成本等優勢,未來可為物聯網、大數據和人工智能等具有海量數據特征的智能應用場景提供高能效硬件解決方案。但要實現大規模產業化仍存在諸多挑戰: (1)模擬計算精度提升困難,模擬存內計算的精度受到信噪比的影響,很難做到8 以上。數字存內計算則不受信噪比的影響,但其能效、面積和成

本需要綜合權衡。近年來,通過數模混合的設計方式,可以在精度、成本與功耗之間得到很好的折中,是存內計算發展的一大重要方向。 (2)工具鏈環節需更加完善以建立良好的生態:存內計算芯片產業化處于起步階段,目前面臨相關工具鏈支持不足的問題,導致算法/應用廠商移植困難。隨著存內計算技術的快速發展,以及企業在這個技術領域持續加大投入,相應的編譯、優化等工具鏈可以快速進步,有望建立初步的應用生態。 (3)跨層協同設計需進一步加強:存內計算芯片涉及器件-芯片-工藝-算法-應用等多層次的跨層協同,各層環環相扣,密不可分,需要跨層協同來實現性能(精度、功耗、時延、可靠性等)與成本的最優。

審核編輯 黃宇

-

sram

+關注

關注

6文章

778瀏覽量

115468 -

頻譜

+關注

關注

7文章

891瀏覽量

46167 -

存算一體

+關注

關注

0文章

106瀏覽量

4541 -

存內計算

+關注

關注

0文章

30瀏覽量

1458

發布評論請先 登錄

相關推薦

存內計算芯片研究進展以及應用-以基于Nor Flash的卷積神經網絡量化以及部署

存內計算芯片研究進展及應用

存內計算芯片研究進展及應用

評論