| 選項 | 說明 |

| Usereditor | 一般軟件自帶的編輯器功能有限,而外部編輯器功能要強大很多。所以建議大家使用外部編輯器。在User editor中輸入編輯器的路徑。 |

| Use user editor as default editor for all files。 | 如果希望每次點擊文件時是通過外部編輯器打開的,可以勾選Use user editor as default editor for all files。反之,如果希望使用自帶編輯器打開則不用勾選。 |

| Top level project path | 指定新建工程目錄。 |

| Enable flow data integrity check | |

| Open last project on startup | 如果勾選此選擇,會打開上次關閉的工程 |

| openfile usingdefault system application | |

| Use lastwindow layoutsetting | 使用上次軟件關閉時的窗口布局。 |

| Auto-correct Tcl command | 在tcl命令窗口中輸入命令時可以自動修改存在的錯誤。 |

| Auto-loadPlace andRoute data | 打開軟件是自動加載布局布線的數據。建議關閉。 |

| Migrate interfacedesign withdevicechange | 修改器件時,interface desiger中的配置也要修改。 |

| EnableIP upgrades prompt on project load | 用新版本打開老的軟件建的工程時,打開該選項會提示IP需要更新,如果不想更新IP可以關閉這個選項。 |

二、新建工程

Step1:點擊設置

Step2:在Top level project path中輸入路徑

Step3:點擊File -> Open Project,路徑會指向step2中設置的路徑

注意:易靈思的工程名為

把retiming和seq_opt設置為0

點擊ok,新建工程完成。

三、添加源文件

四、管腳約束

這里我們以一個LED點燈為例,代碼如下:

Efinty是通過interface designer工具來設置IO等和外設相關的接口及電氣屬性的。Interface designer操作界面的打開通過下面的Open Interface Desinger來實現。

Core 與interface的關系

Eifinty采用的把邏輯資源和硬核資源分開的架構,代碼部分只針對邏輯資源,也就是我們這里提到的Core,而IO及其他硬核部分的配置在interface Designer工具中。下圖是interface與Core的關系,它們之間通過被稱作Siganl Interface的連線資源實現互聯。

因為習慣問題,使用者在最初一定會存在一些問題,但是習慣之后它也是有不少優勢存在的。比如說,在前期的硬件設計中,只需要在Interface Designer中添加已添加的IO及其他需要的硬件接口,并通過一鍵檢測就可以很清楚的知道與外設的連接是否合理,不需要考慮內部因為沒有完整的程序而可能被優化的風險。另外有些interface的選項在修改之后可以不需要先編譯而直接生成數據流。

interface與core的關系

interface界面

告訴軟件FPGA目前的bank電壓,硬件電路的bank電壓要和interface中的一致,如果電壓設置不一致可能存在長時間運行致使芯片失效。設置位置在Device Setting -->I/O Banks

Step1:右鍵選擇GPIO

Step2:根據選擇的是單線還是多線來選擇Create Block還是Create Bus

Step3:編輯IO屬性,IO屬性如下:

選項 | 選擇 | 說明 |

Mode | Input, | Input:把FPGA管腳設置為輸入; Output:把FPGA管腳設置為輸出; Inout:把FPGA管腳設置為雙向管腳; Clkout:把FPGA管腳設置為時鐘輸出 |

Connection Type | Normal,gclk,pll_clkin,VREF | gclk走全局時鐘網線,可以驅動PLL也可以直接驅動內部邏輯 用于普通的GPIO; PLL_CLKIN表示這個IO是用于驅動PLL的; 用于存儲器的參考管腳 |

Register Option | None,register | 是否添加IO寄存器,推薦添加。 |

I/O Standard | 3.3v,1.8v,1.2V,1.5v | 設置IO的電平 |

Double Data I/O Option | None,normal,resync | 是否設置IO為雙延采樣 |

Clock | 當打開IO寄存器時需要添加指定寄存器的時鐘 | |

Drive Strength | 1,2,3,4 | 設置輸出IO的驅動能力 |

Enable Slew Rate | Yes,no | 是否命名能slew rate |

| Instance Name | 用戶定義 | |

| PLLResourec | ||

| Output ClockInversion | on,off | 翻轉時鐘輸出 |

| ConnectionType | gclk, rclk | 時鐘類型 |

| Clock Source | External, Dynamic,Core | External指時鐘通過IO驅動;Dynamic:支持多路時鐘選擇;Core:時鐘通參考通過core供給 |

Automated clock Calculation | 打開時鐘計算和設置窗口 |

檢測Interface設計是否存在問題。

保存設置,點擊Check Design,檢查interface是否存在問題。

再點Generate Efinity Constraint Files,我們就可以在Result --> interface下面看到生成一些文件。通過xxx_template.v復制例化接口

六 添加約束

添加約束的目的是為了告訴FPGA你的設計指標及運行情況。在上面的生成約束之后,在Result àxx.sdc中提供約束參考(請注意該文件不能直接添加到工程中,需要熱復制到別的指定目錄),對于gclk時鐘需要手動添加約束的時鐘周期,對于PLL生成的時鐘已經約束完整。

編譯完成之后可以查看時序報告,也可以通過routing àxx.timing.rpt來查看路徑詳細延時信息,如果想查看更可以通過指令來打印或者通過print_critical_path來控制打印的路徑數量 。

編譯

點擊dashboard中Toggle Automated Flow來設置是單步還是全程編譯(暗色是單步),下面是綜合,布局,布線,生成數據流,stop的相應按鍵。軟件左下角會的編譯進行提示編譯進程。

七 添加debug

7.1通過向導添加debug

點擊Open Debugger Wizard

(1)設置Buffer Depth

(2)Input Pipeline Stage

(3)Capture control

(4)JTAG USER TAP

(5)修改時鐘域

(6)Probe Type

7.2手動debug

手動debug的方式就是自己一個個添加debug的信號 ,當然這種方式也可以添加 VIO,VIO可以通過JTAG產生一些控制信號。手動添加debug的方式如下。

step1:點擊OpenDebugger打開Efinity Debugger頁面,在Perpectives下面選擇Profile Editor.

Step2:根據需要選擇添加VIO或者LA.

Step3: 以添加LA為例,點擊右側的add_probe來添加需要的信號,然后在Name中修改信號名字,Width中指定信號位寬及Probe Trigger or Data中設置信號的觸發屬性。如果要刪除信號就點擊右側的帶“X"的remove Probe.

另外可以指定Data Depth,也就是數據采樣深度,Input Pipeline Stage對可以數據打拍,用于優化時序。

step4 添加VIO。根據需要選擇vio界面的add source和add probe 來添加自己需要的信號。如果要刪除信號則選擇remove source/probe.

step5:點擊Generate,會在工程目錄下就會生成一個debug_top.v,把該文件添加到工程并例化。效果如下。

step6.添加JTAG。打開interface Designer,右擊選擇JTAG User Tap,添加JTAG Block,并指定JTAG resource,如下圖中選擇JTAG user1.然后生成約束例化信號。

注意通過向導添加Debugger和通過手動添加debuger這兩種方式不能共存。另外要注意在interface Designer中添加了User Tap之后,在添加向導時要選擇不同的User Tap號,否則會提示接口有占用。如下圖指示“ERROR: jtage resource = JTAG USER1 has been occupied"。

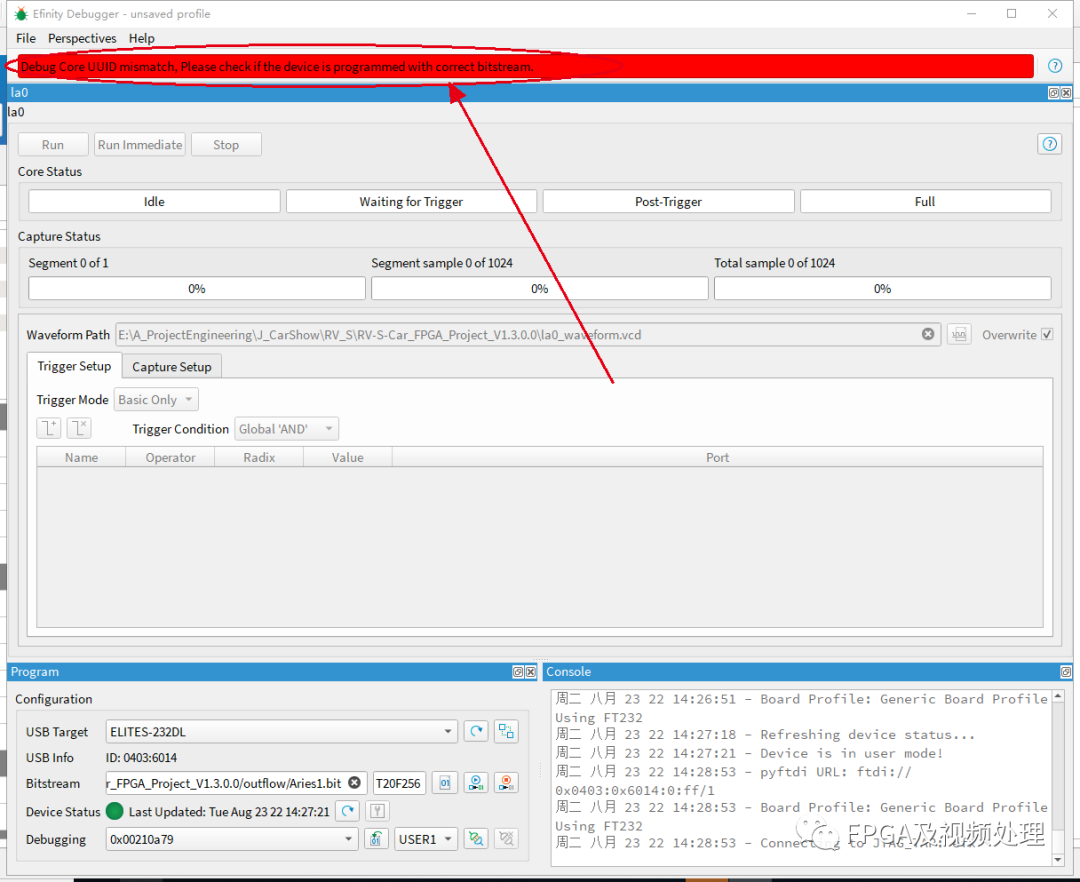

7.3 在線調試

該步驟需要在配置FPGA之后再能操作。

觸發條件的設置

捕獲設置:

?觸發位置

?分段數量

?窗口嘗試

| 主動模式(SPI Active)— AS模式 | 通過SPI專用插座在線燒寫FLASH,FLASH離線燒寫好了再焊接,FPGA自己主動通過從非易失性的SPI FLASH讀取bit流進行加載,支持X1 X2 X4,x8(不同的FPGA支持的位寬有區別) |

| 被動模式(SPI Passive)— PS模式 | |

| JTAG模式 | 上位機通過JTAG口將bit流文件發送到FPGA,對FPGA進行加載 |

| SPI Active using JTAG bridge — Bridge模式 | 通過FPGA的JTAG口燒寫和FPGA連接的SPI FLASH |

九 仿真

易靈思為所有IP提供了仿真模型

以FIFO為例,在工具欄中選擇IP Catalog

另外 關于interfce Designer接口的仿真模型在路徑C:\Efinity\2023.1\pt\sim_models\Verilog下。

原文標題:Efinity入門使用-v3

文章出處:【微信公眾號:易靈思FPGA技術交流】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614605

發布評論請先 登錄

云平臺連接(SC171開發套件V3)

SC171開發套件V3 技術資料

平臺介紹及基本使用(SC171開發套件V3)

AI端側部署案例(SC171開發套件V3)

Efinity debuger常見問題總結-v3

瑞聲科技助力雷鳥V3 AI拍攝眼鏡發布

虹軟AI視覺賦能雷鳥V3 AI拍攝眼鏡發布

Efinity軟件安裝-v5

淺析SDIO協議V2和V3版本的區別

InterfaceDesinger 使用案例-v3

Efinity RISC-V IDE入門使用-3

Efinity入門使用-v3

Efinity入門使用-v3

評論