FPGA(現場可編程門陣列)是一種高度靈活的集成電路,通過編程可以實現多種數字功能。在FPGA中實現單總線協議可以有效地簡化模塊之間的通信。單總線協議指的是所有設備或模塊共用一條通信線路(總線),這樣可以減少硬件連接的復雜度和成本。

1

什么是單總線協議?

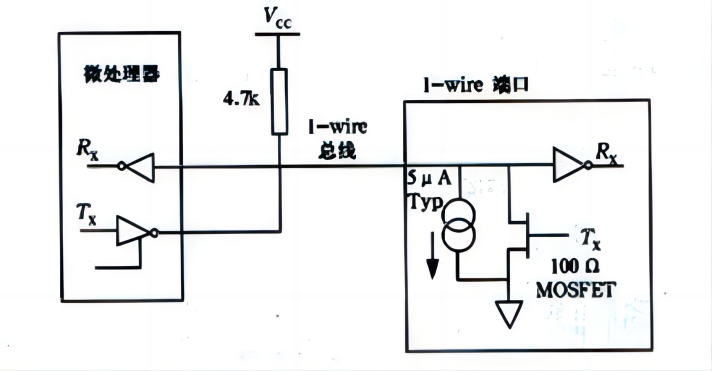

單總線協議是一種共享總線的通信方式,主要特點是所有設備共用一條通信線路。通常,單總線系統包括一個主控模塊(Master)和一個或多個從屬模塊(Slave)。主控模塊負責初始化通信并控制數據傳輸,而從屬模塊在接收到指令后響應主控模塊的請求。

圖1 單總線硬件接口示意圖

2

常見的單總線協議

在FPGA設計中,常見的單總線協議包括I2C(Inter-Integrated Circuit)、SPI(Serial Peripheral Interface)和1-Wire協議。每種協議都有其特定的應用場景和優缺點。

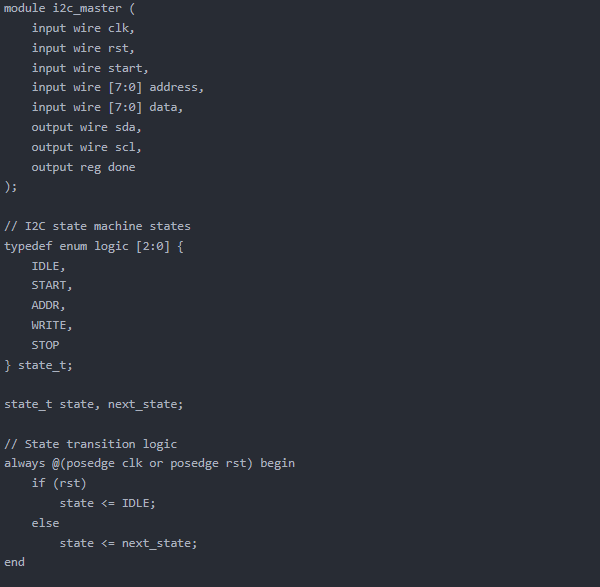

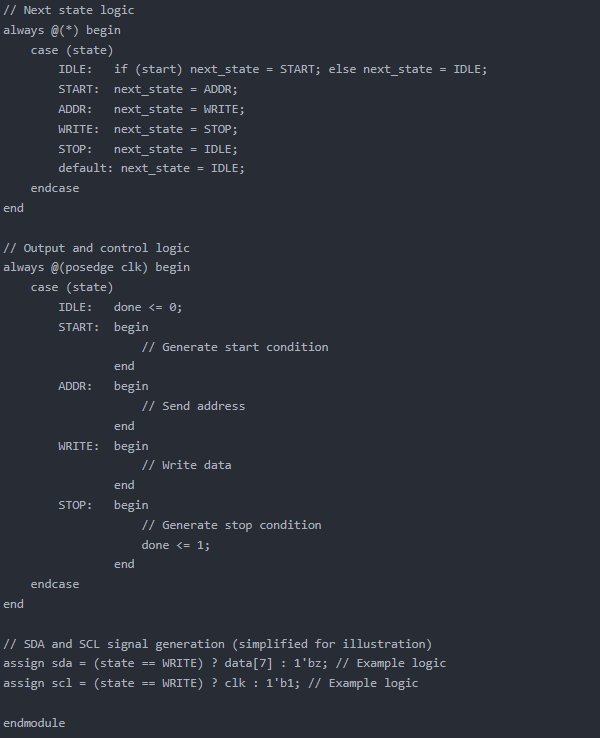

①I2C(Inter-Integrated Circuit)

I2C是一種雙線制的串行通信協議,由飛利浦公司發明。I2C協議使用兩條線進行通信:一條數據線(SDA)和一條時鐘線(SCL)。

優點:

? 簡單的兩線制設計,減少了硬件連接。

? 支持多主控和多從屬設備。

? 廣泛應用于傳感器和低速外圍設備。

實現:I2C協議在FPGA中通常通過Verilog或VHDL實現,包括主控模塊和從屬模塊。主控模塊負責產生時鐘信號并控制數據傳輸,從屬模塊根據主控模塊的時鐘信號同步接收和發送數據。

②SPI(Serial Peripheral Interface)

SPI是一種同步串行通信協議,通常用于高速數據傳輸。SPI使用四條線:數據輸入(MISO)、數據輸出(MOSI)、時鐘(SCLK)和從屬選擇(SS)。

優點:

? 高速數據傳輸。

? 全雙工通信(同時進行數據發送和接收)。

? 硬件實現簡單。

實現:在FPGA中實現SPI協議,需要設計主控模塊和從屬模塊。主控模塊生成時鐘信號并控制從屬選擇線,從屬模塊根據選擇線和時鐘信號同步數據傳輸。

③1-Wire協議

1-Wire協議由Dallas Semiconductor(現Maxim Integrated)開發,是一種單線制的通信協議,主要用于低速設備。

優點:

? 僅需一條數據線,節省了硬件資源。

? 簡單的總線結構,適用于簡單的傳感器和標識設備。

實現:在FPGA中實現1-Wire協議,需要設計一個主控模塊,通過單根數據線進行所有通信。協議的實現涉及總線復用、時序控制和數據幀的發送與接收。

3

設計和實現

在FPGA中實現單總線協議,通常包括以下步驟:

①定義接口信號

定義與協議相關的接口信號,如I2C的SDA和SCL信號,SPI的MISO、MOSI、SCLK和SS信號,1-Wire的單線信號。

②編寫HDL代碼

使用Verilog或VHDL編寫主控模塊和從屬模塊的代碼。需要詳細描述協議的時序、數據幀格式和狀態機。

③總線仲裁和沖突檢測

如果協議支持多主控,需要實現總線仲裁和沖突檢測機制。例如,I2C協議通過檢測總線空閑狀態來實現多主控的仲裁。

④測試與驗證

通過仿真工具和實際硬件測試驗證設計的正確性。需要進行功能測試、時序分析和性能評估,確保協議按照預期工作。

4

示例代碼

以下是一個簡單的I2C主控模塊的Verilog代碼示例:

FPGA中的單總線協議設計涉及定義接口信號、編寫HDL代碼、實現總線仲裁和沖突檢測機制,以及通過仿真與實際硬件測試來驗證設計的正確性。單總線協議在FPGA中的實現提供了一種有效的方式來簡化設計并減少硬件成本,同時也帶來了多種設計挑戰。通過不斷的技術創新和優化,可以更好地利用FPGA的靈活性,滿足日益復雜的應用需求。

-

FPGA

+關注

關注

1643文章

21925瀏覽量

612535 -

總線協議

+關注

關注

0文章

123瀏覽量

15133 -

單總線協議

+關注

關注

1文章

4瀏覽量

1917

發布評論請先 登錄

單總線協議時序對應代碼

單總線測溫系統

DS2438及其在單總線微網中的應用

單總線技術中ROM搜索算法的實現

利用單總線控制器通訊

基于單總線的冷庫溫度監控系統設計

單總線協議詳解

單總線結構

單總線優缺點

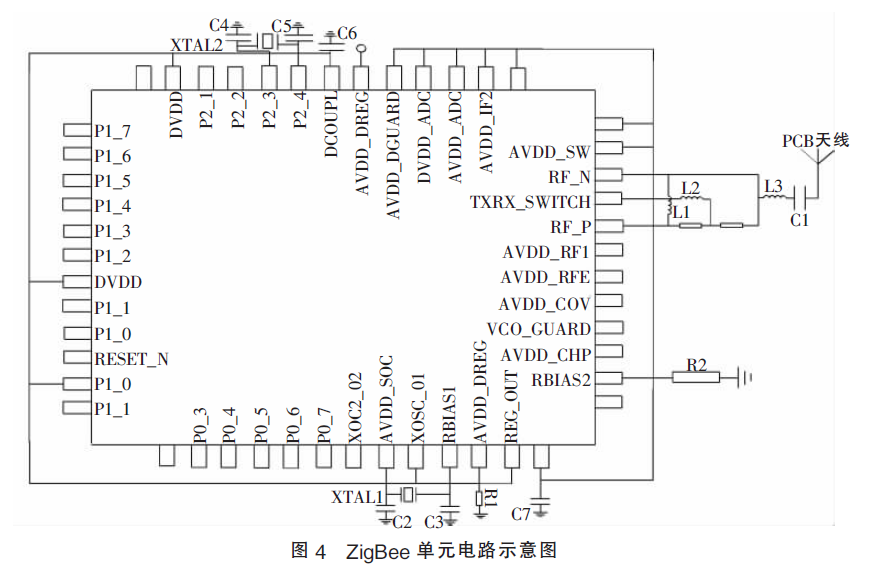

使用ZigBee設計單總線測溫網絡的資料說明

基于ZigBee協議的單總線測溫網絡的設計

FPGA中的單總線協議設計(附示例代碼)

FPGA中的單總線協議設計(附示例代碼)

評論