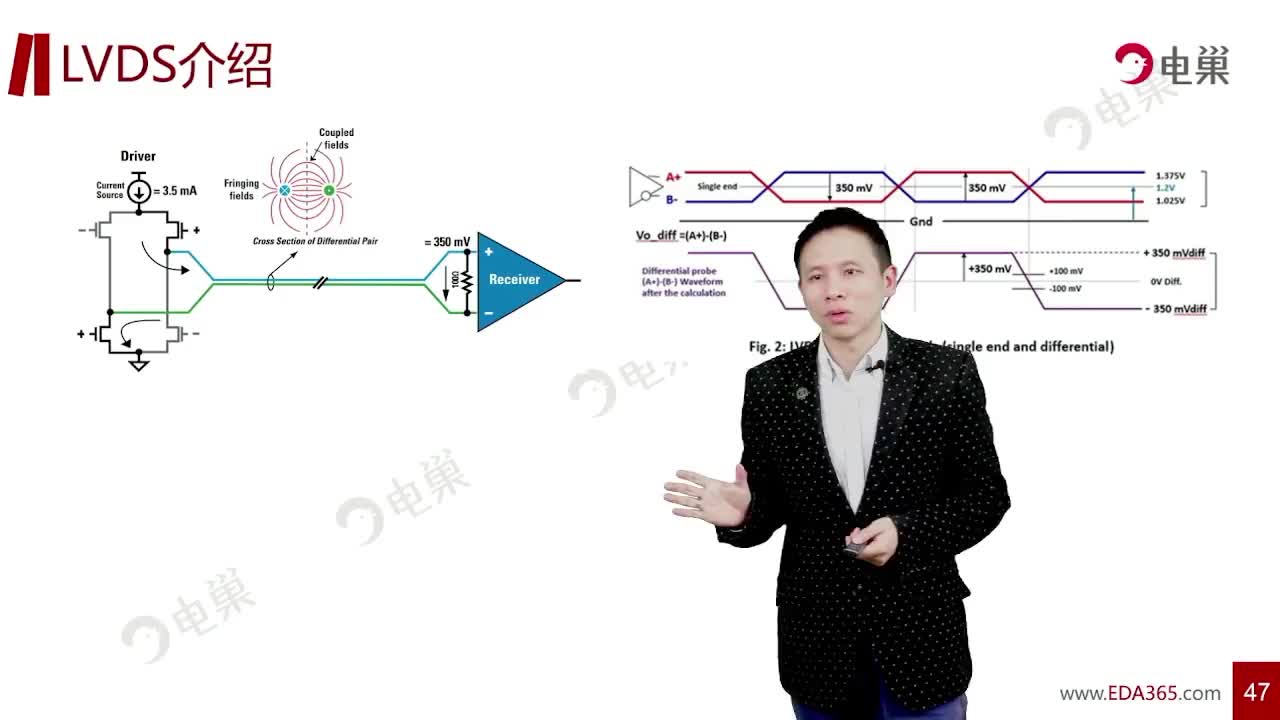

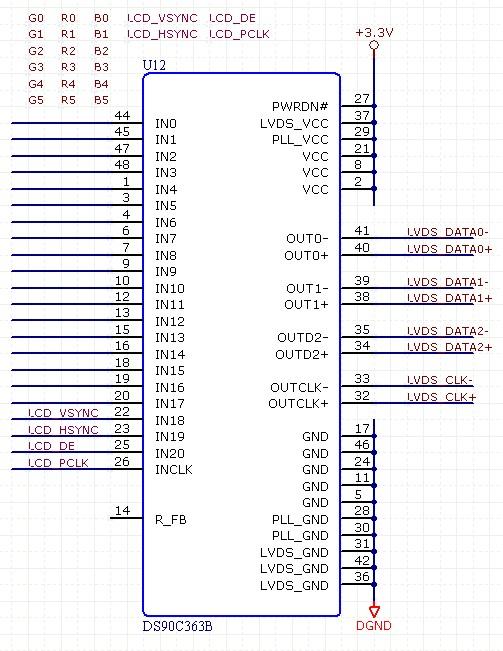

這里以鈦金的LVDS為例。

LVDS RX 時鐘選擇

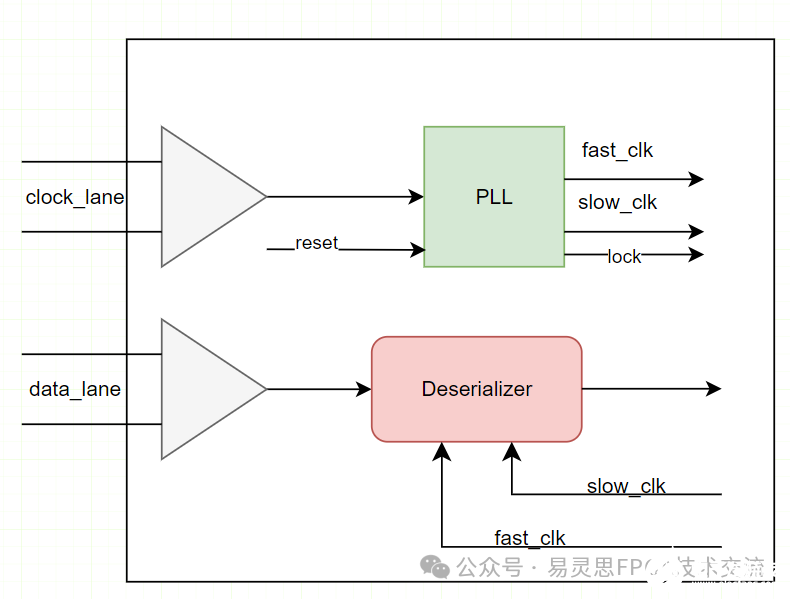

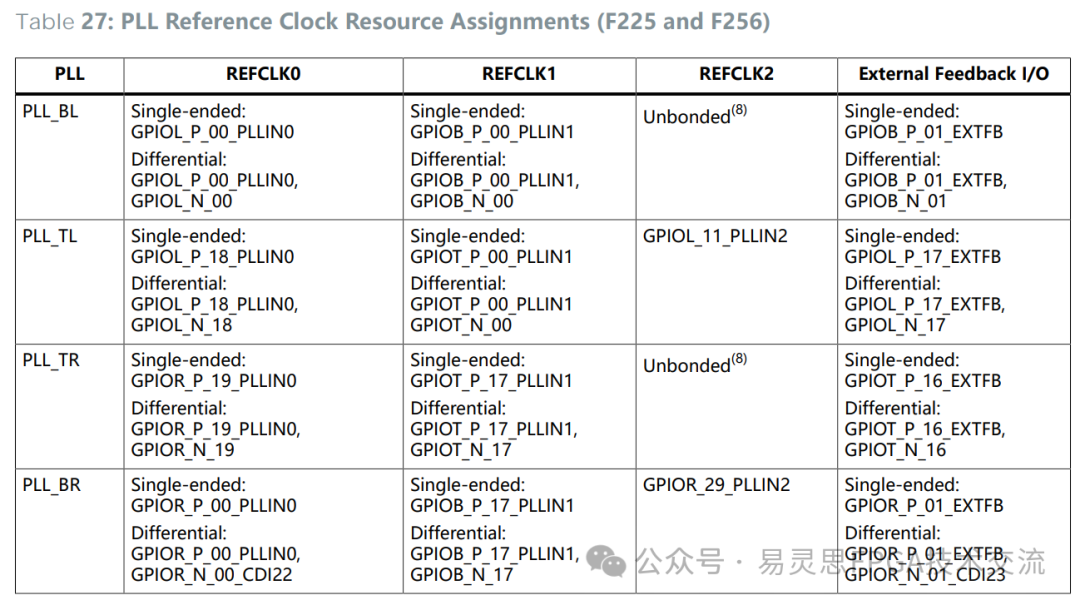

LVDS時鐘的接收要連接名字為GPIOx_P_y_PLLINz名字的差分對,這樣的管腳直接驅動PLL,產(chǎn)生LVDS接收需要的fast_clk和slow_clk,這種主要是用于數(shù)據(jù)和時鐘的速率不是1:1,比如大家常見的1:7,1:8和1:10等,這時就要使用串化/解串器;如果時鐘和數(shù)據(jù)的速率比是1:1并且速率不高,也可以考慮用GCLK走時鐘來采集數(shù)據(jù)。

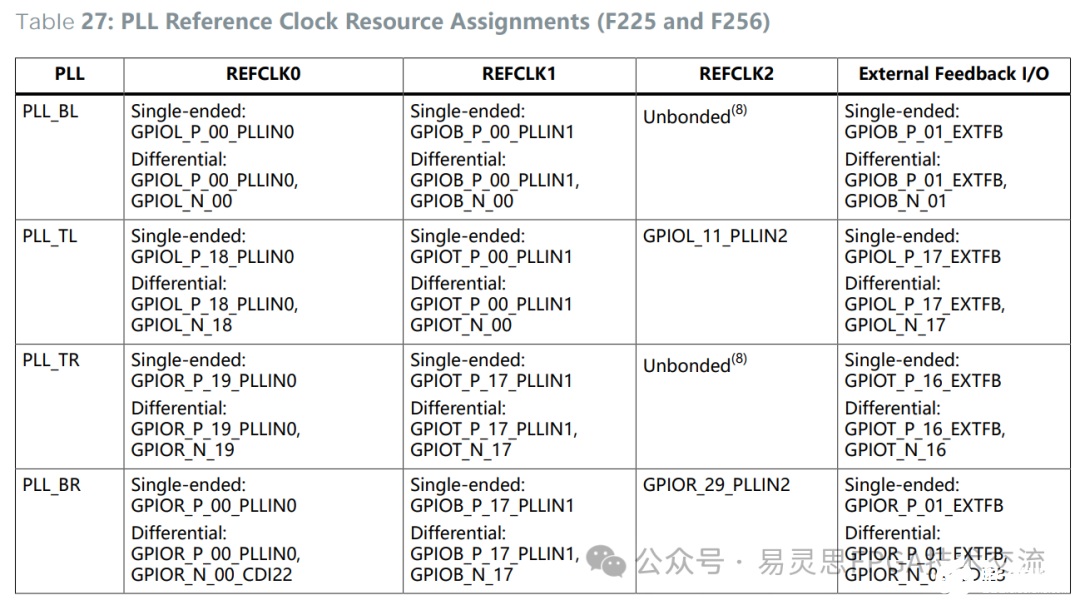

以Ti60F225為例,它共有4個PLL,分別為PLL_BL,PLL_BR,PLL_TR和PLL_TL4個PLL,在要求解串器的情況下,最大只能接收4組LVDS,這是在不考慮PLL作為別的用途的前提下的。

LVDS的PLL的復位信號的處理

有些時候LVDS并不是連續(xù)的,這就要對PLL進行復位處理。在處理方式上我們可以檢測PLL_LOCKED信號是否鎖定,如果隔一段時間沒有鎖定就對PLL進行一次復位。然后再循環(huán)檢測鎖定信號和復位的過程,直到PLL_LOCKED信號為高。目前遇到一些LVDS接收異常的問題很多是通過這樣的方式來解決的。這是為了排除PLL假鎖的情況。

interface設置

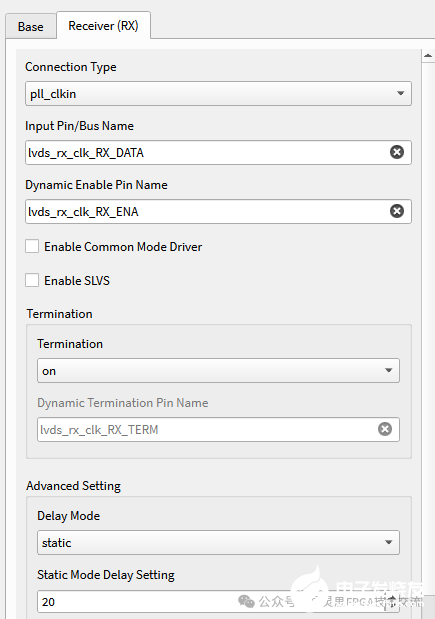

(1)rx clock設置

Enable Common Mode Driver:當使用交流耦合時。要勾選Enable Common Mode Driver。

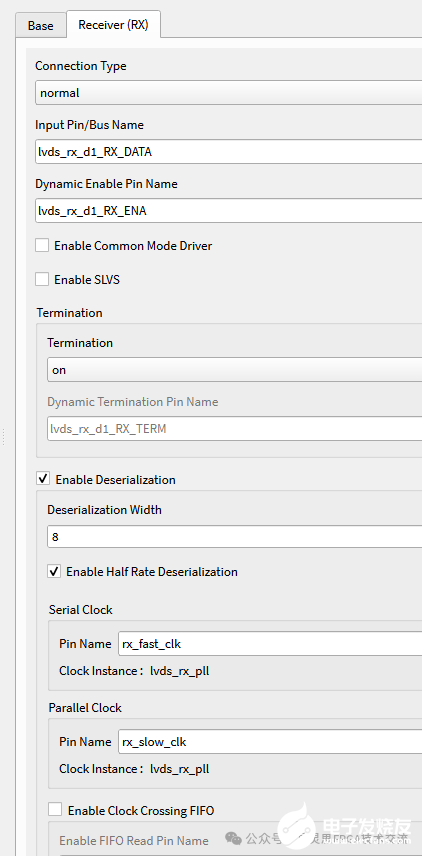

(2) data 設置

Enable Deserialization使能解串因子,Enable Half Rate Deseralization:是指雙沿采樣 。在帶有解串器的設置中要指定解串時鐘和并行的時鐘。對于發(fā)送設置也是大致相同的,只不過要指定的是串化因子。

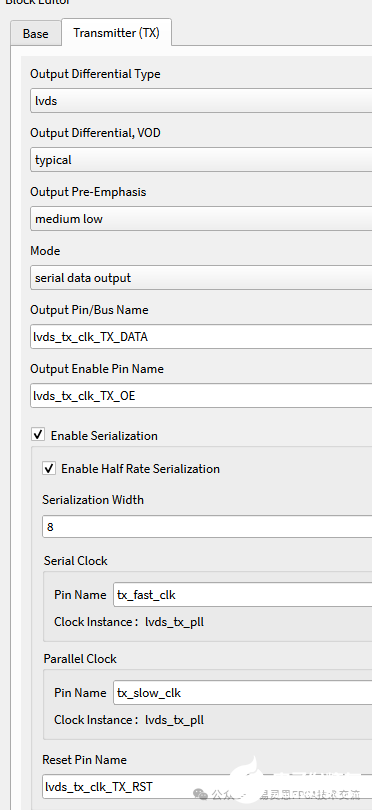

(3)發(fā)送時鐘的設置

發(fā)送時鐘不同于接收時鐘,發(fā)送與數(shù)據(jù)的設置比較相近。把發(fā)送時鐘按如下設置。

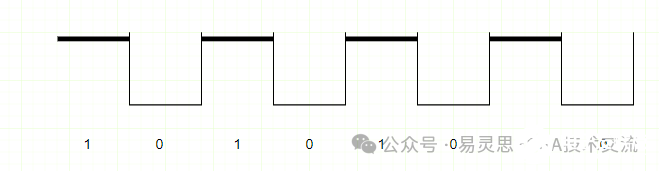

assignlvds_tx_clk_TX_DATA=8'hAA;

經(jīng)過串化之后,時鐘波形就變成了如下的樣子。如果發(fā)送的數(shù)據(jù)是8'hF0時鐘又會是什么樣子呢?大家可以自己思考下。

當然LVDS輸出時鐘選擇serial data output 如果設置為clk輸出,時鐘速率最大為數(shù)據(jù)速率的1/8.具體使用可以先試試。

信號控制

對于數(shù)據(jù)一般不會出錯,大家可能會忘記的是設置使能和復位。注意使能和復位都是高有效。所以正常運行時要把使能設置為高,復位設置為低。

assign lvds_rx_clk_RX_ENA = 1'b1;assign lvds_rx_d0_RX_ENA = 1'b1;assign lvds_rx_d1_RX_ENA = 1'b1; assign lvds_rx_d2_RX_ENA = 1'b1;assign lvds_rx_d3_RX_ENA = 1'b1;assign lvds_rx_d0_RX_RST = 1'b0;assign lvds_rx_d1_RX_RST = 1'b0; assign lvds_rx_d2_RX_RST = 1'b0;assign lvds_rx_d3_RX_RST = 1'b0; assign lvds_tx_d0_TX_RST = 1'b0;assign lvds_tx_d1_TX_RST = 1'b0; assign lvds_tx_d2_TX_RST = 1'b0;assign lvds_tx_d3_TX_RST = 1'b0;assign lvds_tx_d0_TX_OE = 1'b1;assign lvds_tx_d1_TX_OE = 1'b1;assign lvds_tx_d2_TX_OE = 1'b1;assign lvds_tx_d3_TX_OE = 1'b1;

PLL的設置

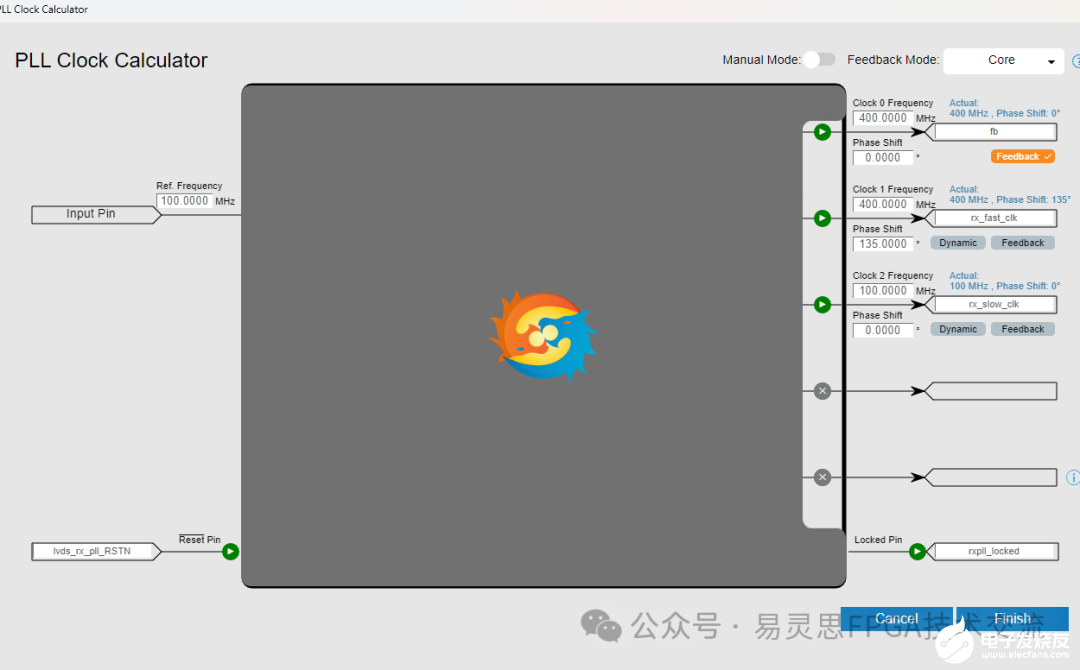

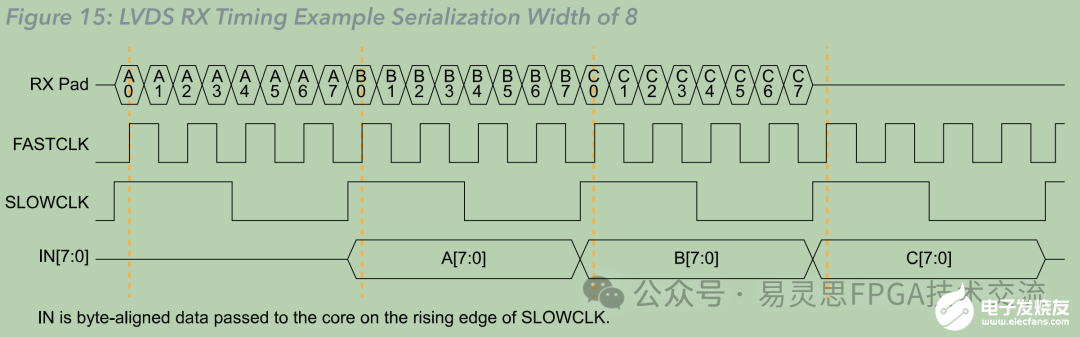

接收的fast_clk是否要移相,由源端時鐘與數(shù)據(jù)的相位關系來決定,如果源是邊沿對應,fast_clk可以移相90或者135;如果是中心對齊,則可以設置相位為0或者為45。

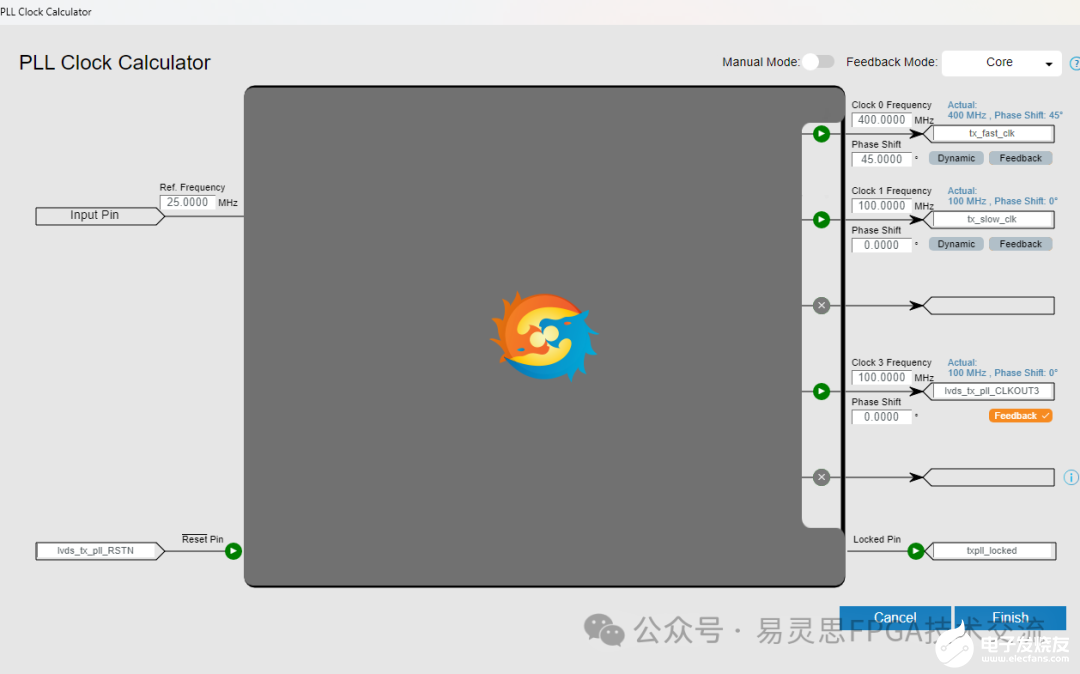

發(fā)送數(shù)據(jù)如果與時鐘有相位差,比如中心,那邊需要產(chǎn)生三個時鐘,fast_tx_clk_c,fast_tx_clk_d及slow_tx_clk.fast_tx_clk_c用于時鐘的fast_clk,為90度,而fast_tx_clk_d為0度,用于數(shù)據(jù)的fast_clk.

當然大家也可以根據(jù)產(chǎn)生的波形或者數(shù)據(jù)的延時進行適當?shù)恼{整。

串化/解串數(shù)據(jù)的排列

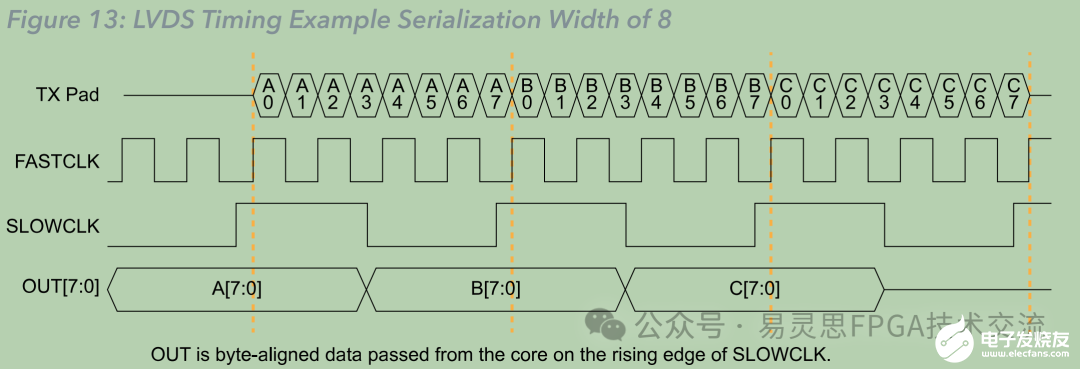

如下圖所示,發(fā)送時LSB先發(fā)送,當然接收也是LVDS先接收。

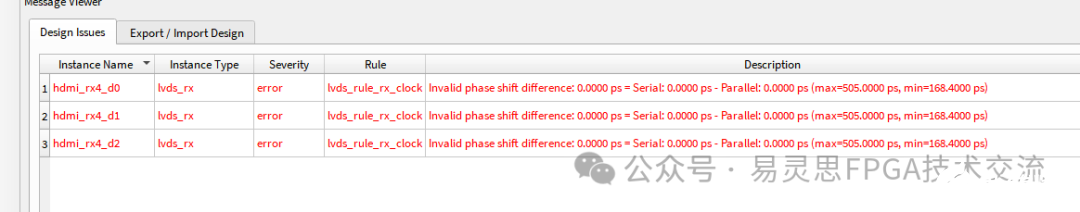

在幫助客戶調試HDMI的時候發(fā)現(xiàn),LVDS不能夠進行動態(tài)調節(jié)相位。解決方案是:

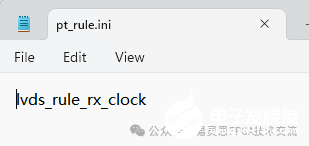

(1)在工程目錄下建議pt_rule.ini文件;

(2)在文件中輸入想要開放權限的rule,以下圖為例,報錯的Rule是lvds_rule_rx_clock。效果如下。

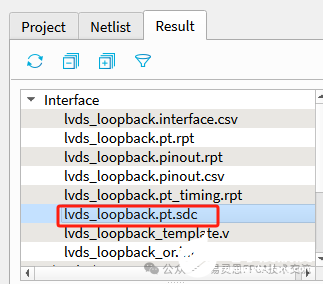

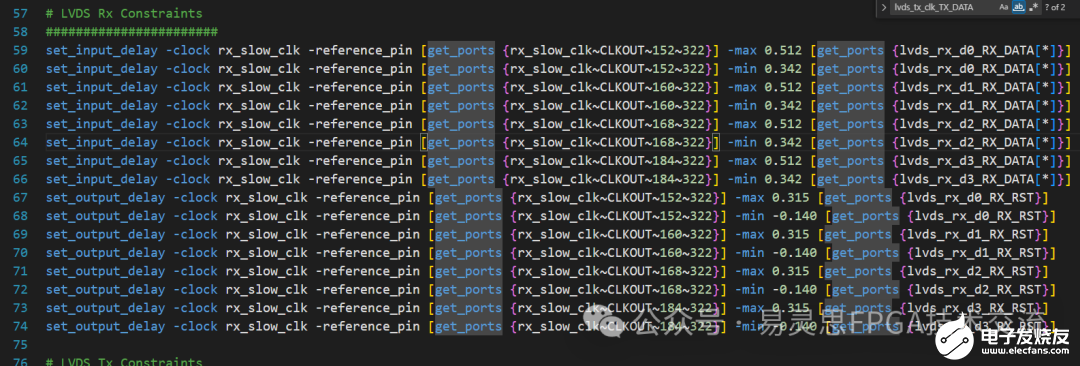

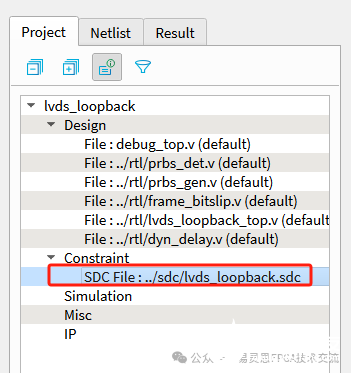

約束添加

需要再次強調的是,Result --> interface --> xx.pt.sdc文件中會有相關的約束模板;我們可以復制該文件到工程目錄下,根據(jù)實際需要進行調整

里面關于LVDS的約束部分如下,大家可以自己打開仔細查看

并添加到Project -->Constraint下。

Trion的LVDS也有相似的操作,這里先只給出一些注意事項,如果需要補充會再次更新。

1. 如果需要在LVDS IO里差分信號同單端信號混用,須最少隔開2對差分IO;例如:使用RXP09/RXN09就不能使用RX07/08/10/11作為差分信號

2. 關于LVDS設備間的互連,要求LVDS RX端的 Vid,Vicm 與LVDS TX端的Vod,Vocm電平標準匹配即可互連

3、LVDS RX源同步時鐘管腳只能通過GPIOx_RXP/Ny_CLKP/Nz經(jīng)對應PLL輸入。

4、每一個LVDS Bank中的IO用作單端輸出,不能超過14個,引起同步開關噪聲(SSN)風險,輸入沒有限制

T20的GPIOB_CLKN0/GPIOB_CLKP0,用做LVDS時只能作為LVDS RX時鐘直接進入鎖相環(huán),不能進入內(nèi)部邏輯

Trion LVDS常用經(jīng)驗

(1)post-divider要修改成2,反饋時鐘用slow_clock.

(2)客戶測試LVDS發(fā)送時鐘lvds輸出改3pf,數(shù)據(jù)改10pf,暫時沒問題。后續(xù)生產(chǎn)小批量看下一致性

(3)添加LVDS約束

現(xiàn)象:(1)pll鎖不定,時鐘路徑由FPGA給出到sensor,再由sensor的LVDS給到FPGA進入pll;

(2)把VCC電壓從1.2V抬到1.25V可以解決一部分問題;

(3)常溫下FPGA PLL不能鎖定,但是如果用風槍加熱一下到40度左右PLL就能鎖定;

(4)客戶第一次做了10多塊板不存在該問題,第二次做了100塊,有10塊左右出現(xiàn)了上面的PLL鎖不定問題。

(5)該現(xiàn)象會跟隨芯片走。

解決思路:

(1)目前已經(jīng)確認客戶都沒有控制LVDS接收PLL的復位,目前要求客戶在PLL參考時鐘穩(wěn)定之后再重新復位一下再重新鎖定。

-

pll

+關注

關注

6文章

884瀏覽量

136092 -

時鐘

+關注

關注

11文章

1886瀏覽量

132878 -

lvds

+關注

關注

2文章

1118瀏覽量

67129 -

RX

+關注

關注

0文章

64瀏覽量

18903 -

復位信號

+關注

關注

0文章

67瀏覽量

6542

發(fā)布評論請先 登錄

FPGA編程LVDS信號圖像處理技術

LVDS詢問

什么是LVDS

什么是lvds信號

LVDS信號電平特性

lvds是什么意思?

LVDS和M-LVDS電路實施指南

LVDS用法:LVDS RX 時鐘選擇 LVDS的PLL的復位信號的處理

LVDS用法:LVDS RX 時鐘選擇 LVDS的PLL的復位信號的處理

評論