晶體和振蕩器印刷電路板設(shè)計(jì)注意事項(xiàng)

在布置印刷電路板以接受組件并為其提供最佳可能性時(shí)在它們的最佳狀態(tài)下執(zhí)行是一項(xiàng)復(fù)雜的任務(wù),例如對(duì)信號(hào)及其路由進(jìn)行計(jì)時(shí)。如果我們遵循一些行業(yè)標(biāo)準(zhǔn)規(guī)則,電磁干擾問題可以最小化,而不需要復(fù)雜的公式和昂貴的模擬工具。

PCB布局變得越來越重要的原因是由于減小板尺寸和增加集成度的趨勢。更小的外形尺寸和更低的功率電子器件都會(huì)導(dǎo)致考慮因素。開關(guān)頻率越高,將產(chǎn)生越多的輻射。與良好布局,許多EMI問題可以最小化以滿足所需的規(guī)范。

水晶印刷電路板(PCB)設(shè)計(jì)指南

?將PCB上的晶體和外部負(fù)載電容器盡可能靠近芯片的振蕩器輸入和輸出引腳。

?振蕩電路中的跡線長度應(yīng)盡可能短,且不得與其他信號(hào)線交叉。

?避免跡線出現(xiàn)直角彎曲

?在使用三次諧波晶體的情況下,確保負(fù)載電容器CX1、CX2和CX3具有公共接地平面。

?環(huán)路必須盡可能小,以最大限度地減少通過PCB耦合的噪聲,并盡可能減少任何寄生現(xiàn)象。

?請勿在水晶單元下方布置接地(GND)圖案。

?請勿在多層PCB的晶體單元下運(yùn)行數(shù)字/RF信號(hào)線或電源。

振蕩器印刷電路板(PCB)設(shè)計(jì)指南

?將振蕩器封裝布局在PCB上,盡可能靠近負(fù)載或芯片的輸入引腳。

?跡線的長度應(yīng)盡可能短,不得與其他信號(hào)線交叉。

?避免跡線出現(xiàn)直角彎曲。45°角區(qū)域的電容增加改變了跡線的特性阻抗,導(dǎo)致反射。這可以通過使直角變圓來減輕。

?使用串聯(lián)端接來減少源和端接之間的駐波。這是

通過將電阻器串聯(lián)插入盡可能靠近振蕩器的輸出引腳來構(gòu)造。為了進(jìn)行適當(dāng)?shù)淖杩蛊ヅ洌?a href="http://m.xsypw.cn/tags/時(shí)鐘/" target="_blank">時(shí)鐘驅(qū)動(dòng)器的輸出阻抗加上串聯(lián)端接電阻器應(yīng)等于跡線阻抗。

?保持差分輸出軌跡盡可能接近相同的長度和盡可能接近。這

增加了跡線之間的耦合因子,將噪聲帶入共模,這對(duì)于差分輸入級(jí)來說問題較小。

?一個(gè)好的做法是將振蕩器連接到公共接地平面。

?不要在晶體單元下布置接地(GND)圖案,這會(huì)增加寄生電容。

?不要在多層PCB的振蕩器下運(yùn)行數(shù)字/RF信號(hào)線或電源,因?yàn)檫@會(huì)增加噪音。

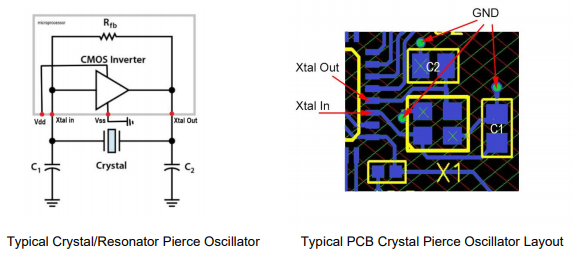

皮爾斯振蕩器布局

以上幾點(diǎn)對(duì)于微處理器使用的皮爾斯振蕩器的應(yīng)用是重要的。看見

下面的電路和使用4片晶體的皮爾斯振蕩器的典型布局。

晶體振蕩器環(huán)路在振蕩器頻率下具有低輸入阻抗,但具有高輸入諧振頻率范圍之外的阻抗特性。

當(dāng)在其附近施加電場時(shí),這種高阻抗特性容易受到EMI的影響。

較新的技術(shù)已經(jīng)將振蕩器信號(hào)電平限制在<1V,使其更容易受到影響。為了強(qiáng)調(diào)保持低雜散PCB電容的重要性,突出顯示了中的Cs,計(jì)算晶體的CL越低,雜散PCB電容對(duì)設(shè)計(jì)

負(fù)載電容器C1/C2的接地連接應(yīng)盡可能短,以避免與其他電路的接地電流。XTAL IN和XTAL OUT引腳通常在加工機(jī)寄生電容可能是一個(gè)問題,因此跡線的布線應(yīng)盡可能遠(yuǎn),同時(shí)保持它們盡可能短。

可以看到的典型電容可能是:

–XTAL IN接地:1pF

–XTAL OUT接地:2pF

–XTAL IN到XTAL OUT:0.5pF

大多數(shù)常見的水晶類型都有接縫密封的外殼,其中外殼蓋與接地引腳。對(duì)于這種類型的封裝,建議將引腳接地,以減少蓋子的EMI電位。需要注意的是,接縫密封包裝提供了更好的性能。這個(gè)另一種密封方法是玻璃密封晶體,由于這個(gè)過程,蓋子與接地引腳。對(duì)于這種類型的封裝,不建議將晶體上的接地引腳接地。

電磁兼容性是指電氣部件、設(shè)備和系統(tǒng)的功能

正如在他們的環(huán)境中設(shè)計(jì)的那樣。這是通過限制無意的生成、傳播和接收電磁能量。這些不需要的噪聲源被稱為電磁

干擾(EMI)。EMC的目標(biāo)是在一個(gè)通用的電磁環(huán)境。

地平面當(dāng)與模擬或數(shù)字電路以及混合組件一起使用時(shí),接地平面是有效的。

接地連接是根據(jù)需要進(jìn)行的,而不是在整個(gè)布局中統(tǒng)一進(jìn)行。

接地平面不是通過簡單地用銅填充所有空白空間并將其連接到地其功能是允許回流流動(dòng),理想的布局應(yīng)具有最小值,因此,使用多層板。整個(gè)均勻?qū)涌梢杂糜诮拥兀粋€(gè)接電源,另一個(gè)接信號(hào)。這增強(qiáng)了層間電容的分布。

它還具有在高頻下電源和地之間的低阻抗的額外優(yōu)點(diǎn)。

單個(gè)孔對(duì)地平面沒有影響,但大槽有影響被其他軌道或孔中斷,正常的低電感電流被轉(zhuǎn)移到障礙物周圍

并且有效地增加了電感。只有當(dāng)它們沒有穿過高di/dt流量的線路時(shí),才應(yīng)允許中斷。下面的軌道

攜帶高開關(guān)電流或快速邏輯邊沿的部件將引起感應(yīng)電容。甚至一個(gè)將地平面的兩段連接起來的非常窄的軌道總比沒有好。在高頻下,這包括數(shù)字邏輯邊緣轉(zhuǎn)換,電流傾向于遵循包圍最小的路徑磁通量。這意味著地平面回流更傾向于集中在相應(yīng)的信號(hào)軌道。

一些電路板制造商不建議留下大面積的銅,因?yàn)檫@可能會(huì)導(dǎo)致阻焊劑的板翹曲或龜裂。如果這可能是一個(gè)問題,您可以更換堅(jiān)實(shí)的地面在不降低其有效性的情況下,通過交叉影線圖案將其平面化。焊接連接到

接地平面,或板表面的任何其他大面積銅,你應(yīng)該“突破”從接地區(qū)域移除焊盤,并使用短長度的軌道進(jìn)行連接。這樣可以防止接地平面在焊接過程中不會(huì)充當(dāng)散熱器,以實(shí)現(xiàn)可靠的連接。

電磁干擾(EMI)

輻射-EMI

什么是輻射發(fā)射(或EMI)測試?

輻射發(fā)射測試包括測量發(fā)射的電磁場強(qiáng)度,是您的產(chǎn)品無意中生成的。發(fā)射是開關(guān)電壓固有的,并且任何數(shù)字電路內(nèi)的電流。這將讓你知道排放水平,然后你可以確定它們是否會(huì)影響系統(tǒng)或周圍系統(tǒng)的性能。

傳導(dǎo)-EMI

每個(gè)電子設(shè)備都會(huì)產(chǎn)生電磁能,其中的某一部分會(huì)傳導(dǎo)到所述電源并且潛在地耦合到所述外部電源。

為了限制干擾量,您的設(shè)備可以重新耦合到電源上;測試實(shí)驗(yàn)室測量這些排放。通常,他們對(duì)的帶寬中的發(fā)射感興趣,150千赫~30兆赫。他們檢查輻射并驗(yàn)證其是否符合規(guī)定的限值。

EMI測試程序和水平由CISPR管理:國際無線電特別委員會(huì)干擾欲了解更多信息,請?jiān)L問國際電工委員會(huì)

排放測試.

根據(jù)ANSI C63.4,LISN(或LISN)位于地面上,而您的產(chǎn)品位于桌子上(或如果設(shè)備很大,則保持落地)。LISN的RF端口直接連接到頻譜分析儀(或通過瞬態(tài)限制器防止電壓尖峰造成的損壞)。

傳導(dǎo)發(fā)射適用性

傳導(dǎo)發(fā)射測試通常在連接到交流電源的設(shè)備上進(jìn)行。那是無論您是否使用經(jīng)過預(yù)認(rèn)證的AC-DC電源適配器。對(duì)于一些標(biāo)準(zhǔn),對(duì)從DC電源操作的設(shè)備也存在限制。

傳導(dǎo)發(fā)射建議

在不詳細(xì)介紹傳導(dǎo)排放合規(guī)性電路設(shè)計(jì)的情況下,有幾個(gè)可以將未通過排放測試的風(fēng)險(xiǎn)降至最低的簡單方法:

?始終為您需要通過的限制提供額定電源

?如果您的設(shè)備是“B類”設(shè)備,請確保提供B類適配器。一個(gè)適配器只通過了A類限制,不太可能導(dǎo)致系統(tǒng)通過。B類適配器沒有保證B級(jí)傳導(dǎo)排放通過,但這肯定會(huì)有所幫助。

?同樣,對(duì)于更嚴(yán)格的醫(yī)療、汽車或航空航天限制,始終尋求供應(yīng)世衛(wèi)組織的規(guī)范聲稱符合相關(guān)限制。

?將至少3種不同的電源帶到測試實(shí)驗(yàn)室

?如果您的設(shè)備使用外部AC-DC電源適配器,請從制造商以防萬一。如果你失敗了,你可以把它換掉,看看其他用品是否會(huì)導(dǎo)致通過

?檢查電源導(dǎo)軌是否有波紋。

?如果你有很好的清潔電源,你的PDN和去耦很可能很好形狀如果你看到開關(guān)電源產(chǎn)生過多的紋波或尖峰,這種噪音很可能出現(xiàn)在電源的交流側(cè)。

?如果有必要拆分接地平面,例如分離模擬和數(shù)字接地以避免噪聲耦合,要小心,因?yàn)榉至训慕拥仄矫婵梢猿洚?dāng)縫隙天線和輻射。在這些情況下,僅在單個(gè)點(diǎn)連接拆分的地平面。這個(gè)公共接地連接越多,創(chuàng)建的環(huán)路越多,EMI也就越多設(shè)計(jì)將輻射。

?許多設(shè)計(jì)將具有旁路和去耦電容器;可以減少回流路徑通過將它們連接到地。這減小了接地回路的尺寸,因此輻射只是要確保不要在電源平面和不相關(guān)的接地平面,這可能導(dǎo)致電容耦合。

-

印刷電路板

+關(guān)注

關(guān)注

4文章

833瀏覽量

35903 -

振蕩器

+關(guān)注

關(guān)注

28文章

3970瀏覽量

140491 -

晶體

+關(guān)注

關(guān)注

2文章

1386瀏覽量

36162

發(fā)布評(píng)論請先 登錄

晶體和振蕩器印刷電路板設(shè)計(jì)注意事項(xiàng)

晶體和振蕩器印刷電路板設(shè)計(jì)注意事項(xiàng)

評(píng)論