工藝周期時間

晶圓實際被加工的時間可以以天為單位來衡量。但由于在工藝站點的排隊以及由于工藝問題導致的臨時減速,晶圓通常在制造區(qū)域停留數(shù)周。晶圓等待的時間越長,增加了污染的機會,這會降低晶圓分選良率。向準時制制造的轉(zhuǎn)變(見后面章節(jié))是提高良率和降低與增加的在線庫存相關(guān)的制造成本的一次嘗試。

晶圓分選良率公式

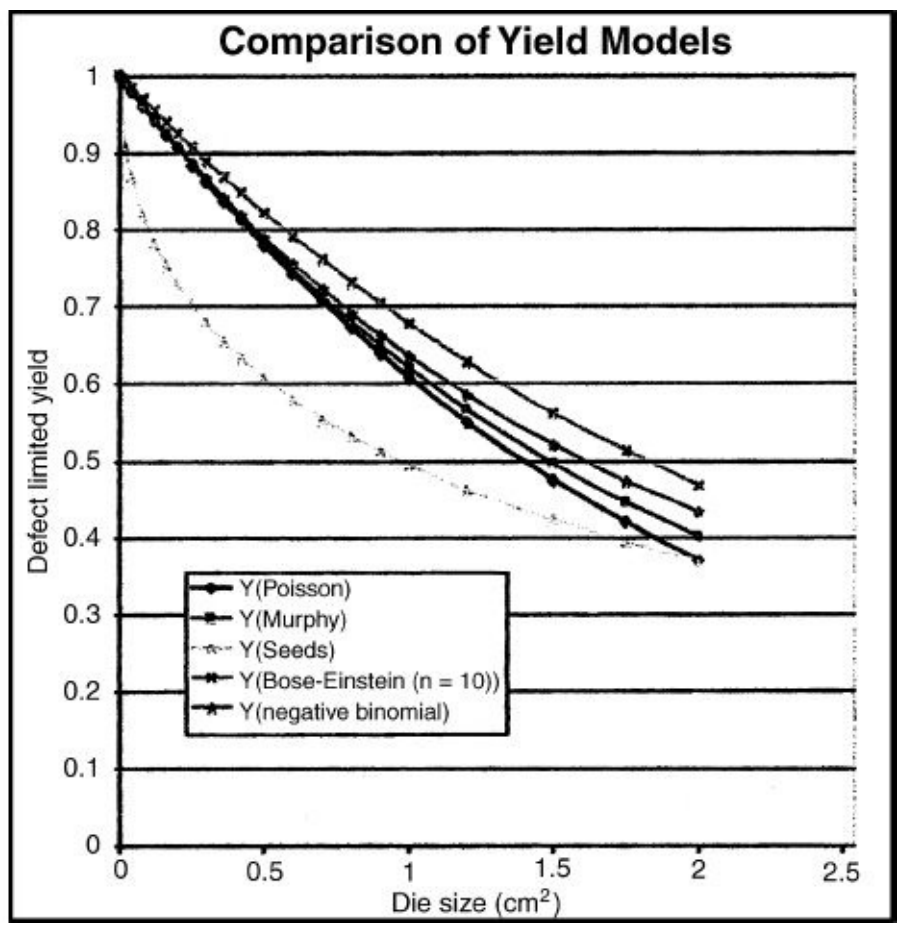

能夠準確理解和預測晶圓分選良率對于一個盈利且可靠的芯片供應商的運營至關(guān)重要。多年來,已經(jīng)開發(fā)了許多模型,這些模型將工藝、缺陷密度和芯片尺寸參數(shù)與晶圓分選良率聯(lián)系起來。

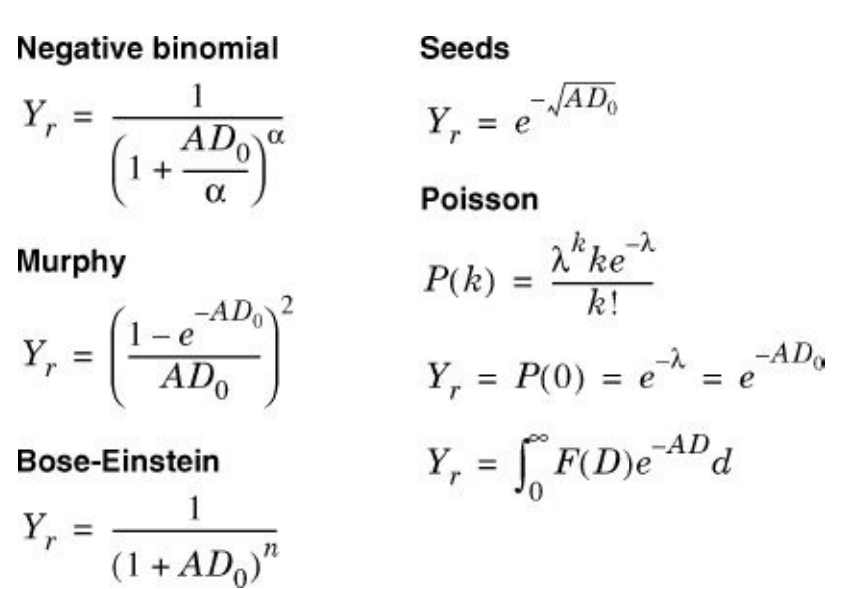

下圖展示了五種良率模型公式。每一種都將不同的參數(shù)與晶圓分選良率聯(lián)系起來。隨著芯片尺寸的增大,工藝步驟數(shù)量的增加,特征尺寸的減小,對更小缺陷尺寸的敏感性增加,更多的背景缺陷變成了致命缺陷。

指數(shù)模型

指數(shù)關(guān)系(下圖所示)或泊松模型是最簡單且最早開發(fā)的良率模型之一。它適用于單個工藝步驟,并假設(shè)晶圓上的缺陷(D0)隨機分布。對于多步驟分析,使用等于工藝步驟數(shù)量的因子(n)(見下圖)。這個模型通常用于包含超過300個裸片和低密度MSI電路的產(chǎn)品。更小的裸片尺寸由西德斯模型預測。

指數(shù)、泊松和西德斯模型都展示了裸片面積、缺陷密度和晶圓分選良率之間的主要關(guān)系。在這些模型中,e是一個常數(shù),值為2.718。

B.T.墨菲提出了一個使用更復雜缺陷分布的模型。玻色-愛因斯坦模型增加了工藝步驟數(shù)量(n),而在負二項式模型中,有一個簇因子。它考慮了傾向于在晶圓表面上“聚集”的缺陷分布,而不僅僅是表現(xiàn)出隨機分布。被SIA在ITRS中采納,簇因子被賦予值為2。

在大多數(shù)良率模型中,處理步驟的因子(n)實際上是圖案化步驟的數(shù)量。經(jīng)驗證明,圖案化步驟產(chǎn)生最多的點缺陷,因此直接關(guān)系到分選良率。

沒有兩個復雜電路具有可比的設(shè)計或工藝。工藝在公司與公司之間不同,基本背景缺陷密度也是如此。這些因素使得開發(fā)一個準確的通用良率模型變得困難。大多數(shù)芯片公司都開發(fā)了自己的模型,這些模型反映了他們的特定制造工藝和產(chǎn)品設(shè)計。所有模型都是基于缺陷驅(qū)動的。也就是說,它們假設(shè)所有的制造工藝都在控制之下,缺陷水平是內(nèi)置于工藝中的。它們不包括主要的工藝問題,例如污染的工藝氣體罐。

在所有模型中使用的缺陷密度與通過光學檢查晶圓表面確定的缺陷密度不同。在良率模型中顯示的缺陷密度是全面的;它包括污染物和表面以及晶體缺陷。此外,它只預測那些破壞裸片的缺陷:“致命缺陷”。落在芯片非關(guān)鍵區(qū)域的缺陷不包括在模型中,兩個或更多的缺陷落在同一個敏感區(qū)域的情況也不包括。

-

半導體

+關(guān)注

關(guān)注

335文章

28669瀏覽量

233394 -

晶圓

+關(guān)注

關(guān)注

52文章

5129瀏覽量

129237 -

模型

+關(guān)注

關(guān)注

1文章

3499瀏覽量

50072

原文標題:半導體工藝之生產(chǎn)力和工藝良率(六)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

半導體工藝講座

常見的射頻半導體工藝,你知道幾種?

SPC在半導體在半導體晶圓廠的實際應用

半導體工藝幾種工藝制程介紹

如何保證半導體良率

單片機芯片生產(chǎn)工藝對單片機芯片良率的影響

半導體工藝開發(fā):利用虛擬晶圓制造的統(tǒng)計數(shù)據(jù)來提高良率

半導體工藝之生產(chǎn)力和工藝良率

半導體工藝之生產(chǎn)力和工藝良率

評論