■前篇回顧

信號(hào)之間的時(shí)間關(guān)系對(duì)數(shù)字設(shè)計(jì)的可靠運(yùn)行至關(guān)重要。對(duì)于同步設(shè)計(jì),時(shí)鐘信號(hào)相對(duì)于數(shù)據(jù)信號(hào)的時(shí)間尤為重要。在上篇中,我們?yōu)槟敿?xì)介紹了混合信號(hào)示波器(MSO)的基礎(chǔ)設(shè)置以及解釋在泰克混合示波器上的混合信號(hào)顯示。本期,將帶您繼續(xù)了解如何輕松確定多個(gè)邏輯輸入和時(shí)鐘信號(hào)之間的時(shí)間關(guān)系,并了解如何自動(dòng)確定時(shí)鐘與數(shù)據(jù)時(shí)間關(guān)系。

消除通道之間的時(shí)間偏移

每臺(tái)Tektronix MDO或MSO系列示波器都有兼容的邏輯探頭。為了簡(jiǎn)化數(shù)字測(cè)量,示波器會(huì)補(bǔ)償邏輯探頭的傳播延遲。因此,不需要進(jìn)行數(shù)字通道探頭的相差校正。

然而,為了更好地進(jìn)行模擬和數(shù)字波形之間的時(shí)間關(guān)聯(lián)測(cè)量,重要的是消除模擬到數(shù)字的時(shí)間偏移。在圖5所示的示例中,為了將模擬通道與數(shù)字通道對(duì)齊,模擬波形的2V(50%幅度)位置與在2V閾值處發(fā)生的數(shù)字信號(hào)過(guò)渡時(shí)間對(duì)齊。手動(dòng)調(diào)整相差值以將模擬通道對(duì)齊到數(shù)字通道。此相差校正過(guò)程需要對(duì)任何其他模擬通道重復(fù)進(jìn)行。

當(dāng)更換模擬探頭時(shí),應(yīng)檢查模擬通道的偏移;當(dāng)測(cè)量不同的邏輯系列時(shí),應(yīng)檢查數(shù)字閾值。配置好閾值和偏移后,示波器便可以用于驗(yàn)證和調(diào)試數(shù)字電路。

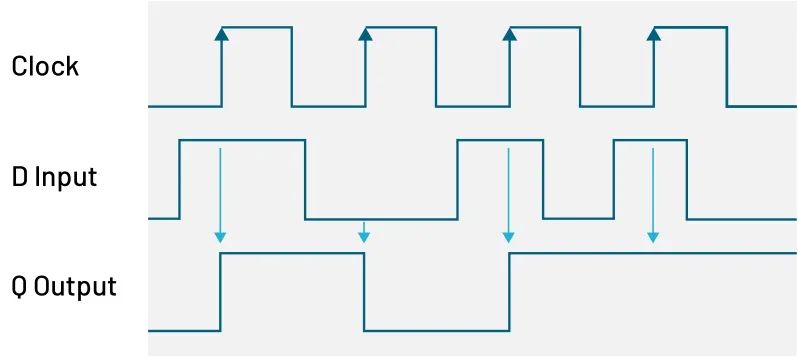

圖6. 觸發(fā)器行為示例

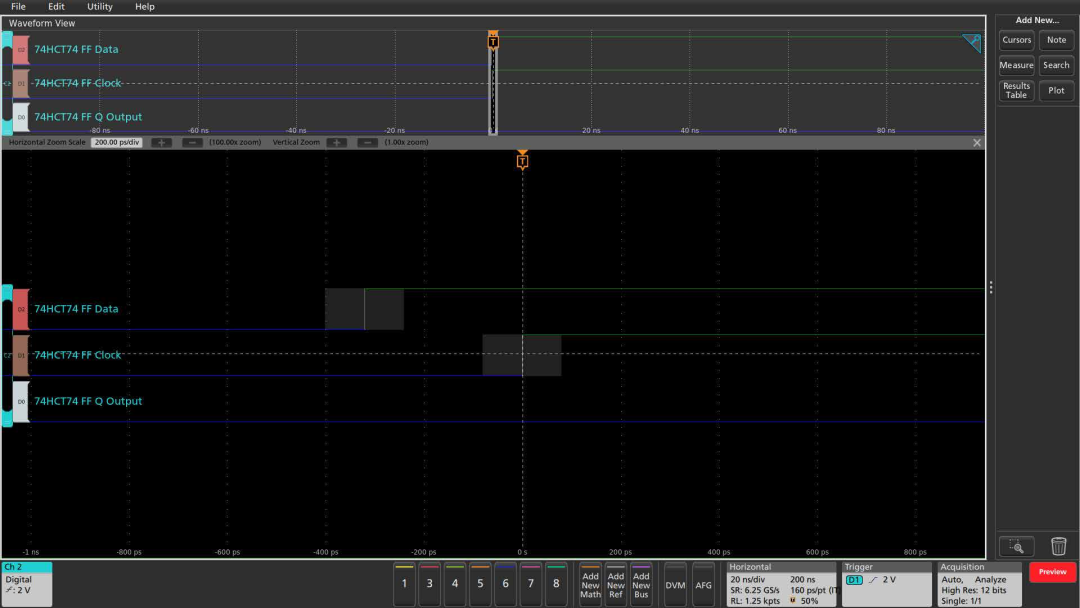

圖7. 這個(gè)74HCT74觸發(fā)器看起來(lái)按預(yù)期工作

觸發(fā)器時(shí)間測(cè)量

最簡(jiǎn)單的同步邏輯器件是觸發(fā)器。D輸入的邏輯狀態(tài)只有在時(shí)鐘上升沿之后(經(jīng)過(guò)D觸發(fā)器傳播延遲后)才會(huì)出現(xiàn)在Q輸出上。MSO是驗(yàn)證觸發(fā)器工作狀態(tài)和調(diào)試數(shù)字電路的理想工具。

乍一看,如圖7所示,觸發(fā)器似乎按預(yù)期工作。數(shù)據(jù)信號(hào)在時(shí)鐘上升沿之前已經(jīng)穩(wěn)定了幾納秒,并且在時(shí)鐘邊沿之后保持穩(wěn)定了幾納秒。從時(shí)鐘邊沿到Q輸出的傳播延遲大約是6納秒。

圖8. 74HCT74觸發(fā)器上的建立時(shí)間違規(guī)導(dǎo)致Q輸出未改變

在圖8中,數(shù)據(jù)信號(hào)在時(shí)鐘邊沿之前僅300ps發(fā)生變化,遠(yuǎn)低于15ns 的建立時(shí)間規(guī)范——這是一個(gè)建立時(shí)間違規(guī)。注意,Q輸出沒(méi)有如預(yù)期那樣改變狀態(tài)。

注意圖8中信號(hào)過(guò)渡周圍的灰色區(qū)域。MSO顯示這些區(qū)域以指示與數(shù)字采樣率相關(guān)的時(shí)間不確定性。

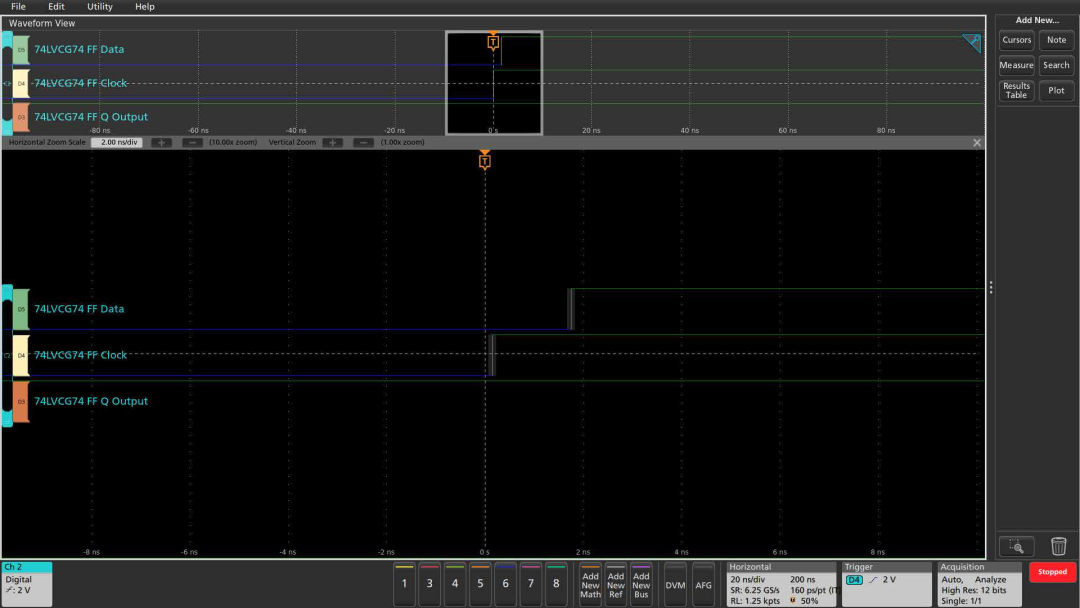

圖9. 74HCT74觸發(fā)器上的保持時(shí)間違規(guī)導(dǎo)致Q輸出未改變

圖9顯示了一個(gè)數(shù)據(jù)信號(hào)在時(shí)鐘邊沿后大約300ps發(fā)生變化的實(shí)例。這遠(yuǎn)低于3ns的保持時(shí)間規(guī)范——這是一個(gè)保持時(shí)間違規(guī)。再次注意,Q輸出沒(méi)有如預(yù)期那樣改變狀態(tài)。

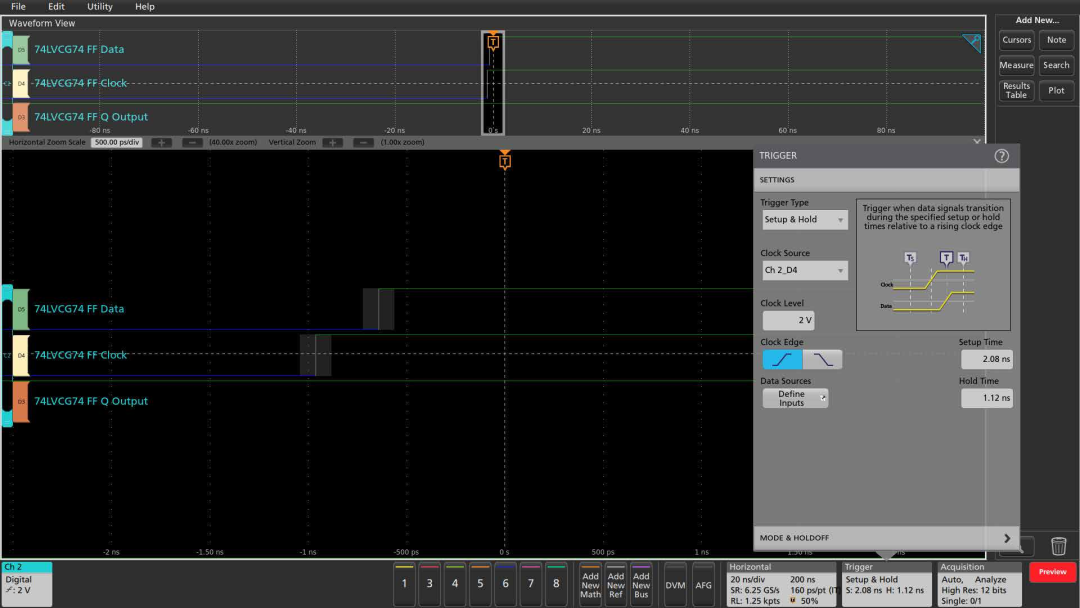

圖10. 在 74LVCG74觸發(fā)器上的自動(dòng)建立和保持時(shí)間違規(guī)觸發(fā)捕獲了許多錯(cuò)誤

捕獲建立和保持時(shí)間違規(guī)

MSO具有一種專門的觸發(fā)模式,旨在自動(dòng)捕獲每個(gè)建立和/或保持時(shí)間違規(guī)。建立和保持時(shí)間觸發(fā)器測(cè)量時(shí)鐘信號(hào)與數(shù)據(jù)信號(hào)(或某些MSO上的數(shù)據(jù)信號(hào))之間的時(shí)間關(guān)系,并在建立時(shí)間或保持時(shí)間低于規(guī)范時(shí)捕獲信號(hào)。這種功能簡(jiǎn)化了調(diào)試工作,還可以用于設(shè)計(jì)的無(wú)人值守監(jiān)控。

在查閱74LVCG74組件數(shù)據(jù)表后,將建立和保持時(shí)間觸發(fā)參數(shù)分別設(shè)置為2納秒和1納秒,以捕獲任何違規(guī)情況,如圖10所示。MSO會(huì)自動(dòng)觸發(fā)在第一個(gè)違反指定參數(shù)的輸入條件上。

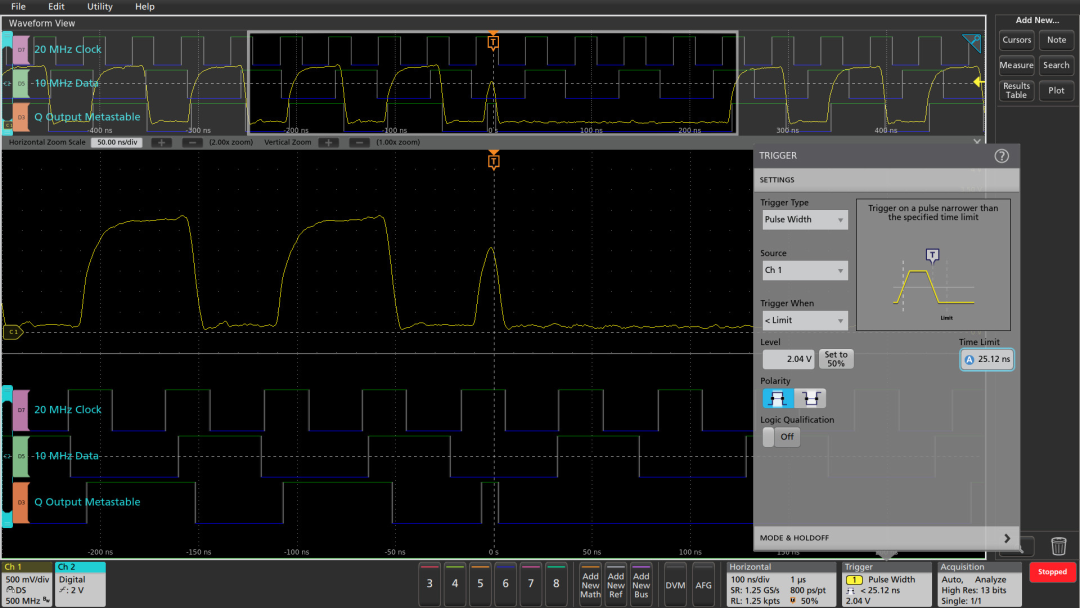

圖11. 脈沖寬度觸發(fā)器在74LS74觸發(fā)器的輸出上捕獲到一個(gè)窄脈沖故障

在上一個(gè)例子中,建立和保持觸發(fā)器用于觸發(fā)觸發(fā)器的輸入。另一種方法是觸發(fā)設(shè)備輸出的信號(hào)錯(cuò)誤,并捕獲輸入信號(hào)進(jìn)行分析。

在下一個(gè)例子中,一個(gè)基于74LS74低功耗肖特基TTL 技術(shù)的舊設(shè)計(jì)出現(xiàn)了間歇性錯(cuò)誤。高電平的最低輸出電壓為2.4V,因此所有高電平輸出信號(hào)應(yīng)至少達(dá)到該電壓。該設(shè)計(jì)基于20MHz時(shí)鐘(周期50ns),因此所有輸出脈沖的寬度應(yīng)至少達(dá)到這個(gè)周期的一半。

掌握這些信息后,示波器可以快速確定輸出信號(hào)是否按預(yù)期工作,并在不正常時(shí)捕獲輸入和輸出信號(hào)。圖11顯示了脈沖寬度觸發(fā)器捕獲到的一個(gè)窄脈沖故障,即脈沖寬度小于該設(shè)計(jì)預(yù)期的最小脈沖寬度的一半。

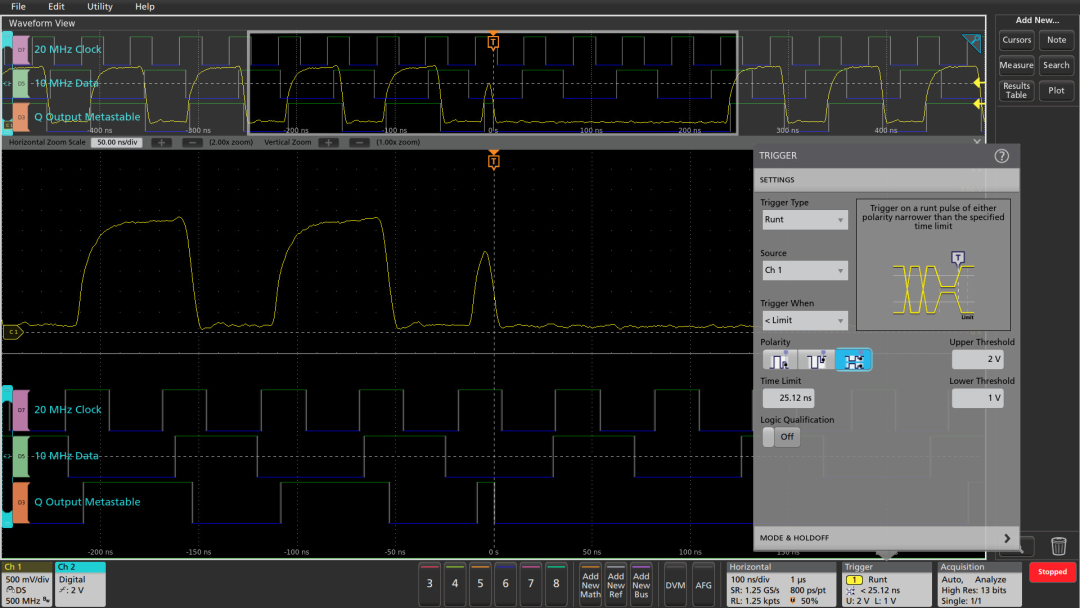

圖12. 窄脈沖觸發(fā)器輕松捕獲了74LS74觸發(fā)器輸出上的低幅度窄脈沖

不僅僅是在觸發(fā)器的輸出上出現(xiàn)了間歇性故障

一些故障還表現(xiàn)出低幅度。圖12顯示了一個(gè)窄脈沖觸發(fā)器捕獲到的低幅度脈沖,這些脈沖不符合組件的規(guī)范。

圖13. 在74LVCG74觸發(fā)器上的建立時(shí)間違規(guī)觸發(fā)的光標(biāo)測(cè)量

使用這些觸發(fā)設(shè)置中的任何一個(gè)

使用這些觸發(fā)設(shè)置中的任何一個(gè),您都可以捕獲輸入和輸出信號(hào)。圖13顯示了使用光標(biāo)進(jìn)行的建立時(shí)間測(cè)量,清晰地指示了建立時(shí)間違規(guī)(大約6ns,遠(yuǎn)低于20ns的最小值)。

混合信號(hào)示波器結(jié)合了基本的邏輯分析儀功能和示波器的模擬信號(hào)分析功能。Tektronix MSO和MDO系列包括建立和保持時(shí)間觸發(fā)、脈沖觸發(fā)以及高分辨率數(shù)字采樣,以便于快速數(shù)字調(diào)試。

-

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2033瀏覽量

61923 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

466瀏覽量

29108 -

混合信號(hào)示波器

+關(guān)注

關(guān)注

0文章

57瀏覽量

11860 -

泰克科技

+關(guān)注

關(guān)注

2文章

199瀏覽量

19876

原文標(biāo)題:用混合信號(hào)示波器識(shí)別建立和保持時(shí)間違規(guī)(下)

文章出處:【微信號(hào):泰克科技,微信公眾號(hào):泰克科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

靜態(tài)時(shí)序之建立時(shí)間和保持時(shí)間分析

混合信號(hào)示波器的原理和應(yīng)用

建立時(shí)間和保持時(shí)間討論

FPGA實(shí)戰(zhàn)演練邏輯篇51:建立時(shí)間和保持時(shí)間

混合信號(hào)示波器解決方案

用混合信號(hào)示波器調(diào)試嵌入式混合信號(hào)設(shè)計(jì)

如何選擇混合信號(hào)示波器

阻礙示波器捕獲異常信號(hào),如何計(jì)算示波器的死區(qū)時(shí)間?

是德科技使用混合信號(hào)示波器調(diào)試嵌入式混合信號(hào)設(shè)計(jì)

怎樣調(diào)試混合信號(hào)示波器

為什么要選擇混合信號(hào)示波器

混合信號(hào)示波器 用途

SOC設(shè)計(jì)中的建立時(shí)間和保持時(shí)間

PCB傳輸線建立時(shí)間、保持時(shí)間、建立時(shí)間裕量和保持時(shí)間裕量

用混合信號(hào)示波器識(shí)別建立和保持時(shí)間違規(guī)

用混合信號(hào)示波器識(shí)別建立和保持時(shí)間違規(guī)

評(píng)論