在數字電路設計中,觸發器是一種非常重要的基本邏輯元件,用于存儲一位二進制信息。觸發器的種類繁多,但主要分為兩大類:主從觸發器(Master-Slave Flip-Flop)和邊沿觸發器(Edge-Triggered Flip-Flop)。

1. 觸發器的基本概念

觸發器是一種具有記憶功能的邏輯元件,它可以存儲一位二進制信息,即0或1。觸發器的基本功能是將輸入信號的某個狀態保存下來,并在需要時輸出。觸發器的工作原理是通過內部的邏輯電路實現對輸入信號的采樣、存儲和輸出。

2. 主從觸發器(Master-Slave Flip-Flop)

2.1 工作原理

主從觸發器由兩個部分組成:主觸發器(Master)和從觸發器(Slave)。主觸發器負責接收輸入信號,從觸發器負責存儲和輸出數據。在主從觸發器中,主觸發器和從觸發器的時鐘信號是相反的,即當主觸發器的時鐘信號為高電平時,從觸發器的時鐘信號為低電平,反之亦然。

當輸入信號發生變化時,主觸發器首先接收并存儲這個變化,然后在下一個時鐘周期,從觸發器將主觸發器存儲的數據復制到自己的存儲單元中,從而實現數據的穩定輸出。

2.2 特性

- 同步性 :主從觸發器具有同步特性,即數據的存儲和輸出與時鐘信號同步。

- 抗干擾性 :由于主從觸發器的數據存儲和輸出是分時進行的,因此具有較好的抗干擾性能。

- 速度 :主從觸發器的數據存儲和輸出需要兩個時鐘周期,因此速度相對較慢。

2.3 優缺點

- 優點 :抗干擾性能好,適用于高速電路設計。

- 缺點 :速度較慢,不適合用于對速度要求極高的場合。

2.4 應用場景

主從觸發器廣泛應用于高速數字電路設計中,如CPU、內存控制器等。

3. 邊沿觸發器(Edge-Triggered Flip-Flop)

3.1 工作原理

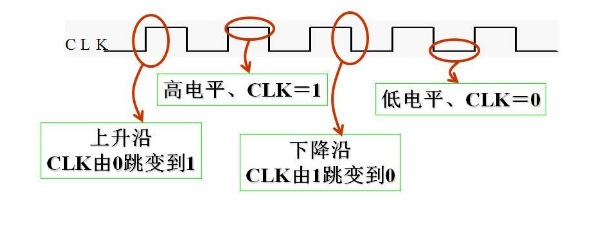

邊沿觸發器的工作原理與主從觸發器不同。邊沿觸發器的數據存儲和輸出是在時鐘信號的上升沿或下降沿觸發的。當輸入信號在時鐘信號的上升沿或下降沿發生變化時,邊沿觸發器會立即存儲這個變化,并在下一個時鐘周期輸出。

3.2 特性

- 異步性 :邊沿觸發器的數據存儲和輸出與時鐘信號異步,即數據存儲和輸出不受時鐘信號的控制。

- 速度 :邊沿觸發器的數據存儲和輸出只需要一個時鐘周期,因此速度較快。

- 敏感性 :由于邊沿觸發器的數據存儲和輸出是立即進行的,因此對輸入信號的變化非常敏感。

3.3 優缺點

- 優點 :速度快,適用于對速度要求極高的場合。

- 缺點 :抗干擾性能相對較差,不適合用于高速電路設計。

3.4 應用場景

邊沿觸發器廣泛應用于對速度要求極高的數字電路設計中,如高速數據通信、高速計數器等。

4. 主從觸發器與邊沿觸發器的比較

4.1 工作原理的比較

主從觸發器和邊沿觸發器的工作原理有明顯的區別。主從觸發器通過兩個觸發器的配合實現數據的存儲和輸出,而邊沿觸發器則是在時鐘信號的上升沿或下降沿觸發數據的存儲和輸出。

4.2 特性的比較

主從觸發器具有同步特性和較好的抗干擾性能,但速度相對較慢;而邊沿觸發器具有異步特性和較快的速度,但抗干擾性能相對較差。

4.3 優缺點的比較

主從觸發器的優點是抗干擾性能好,適用于高速電路設計;缺點是速度較慢。邊沿觸發器的優點是速度快,適用于對速度要求極高的場合;缺點是抗干擾性能相對較差。

4.4 應用場景的比較

主從觸發器廣泛應用于高速數字電路設計中,如CPU、內存控制器等;而邊沿觸發器廣泛應用于對速度要求極高的數字電路設計中,如高速數據通信、高速計數器等。

5. 結論

主從觸發器和邊沿觸發器各有優缺點,適用于不同的應用場景。在實際的數字電路設計中,需要根據具體的設計要求和應用場景,選擇合適的觸發器類型。

-

主從觸發器

+關注

關注

0文章

13瀏覽量

6521 -

輸入信號

+關注

關注

0文章

472瀏覽量

12874 -

邏輯元件

+關注

關注

0文章

9瀏覽量

6085 -

邊沿觸發器

+關注

關注

0文章

34瀏覽量

4155

發布評論請先 登錄

主從觸發器,主從觸發器的原理和特點有哪些?

什么是邊沿觸發器_邊沿D觸發器介紹

邊沿觸發器波形圖

主從觸發器和邊沿觸發器的特點及應用

主從觸發器和邊沿觸發器的特點及應用

評論