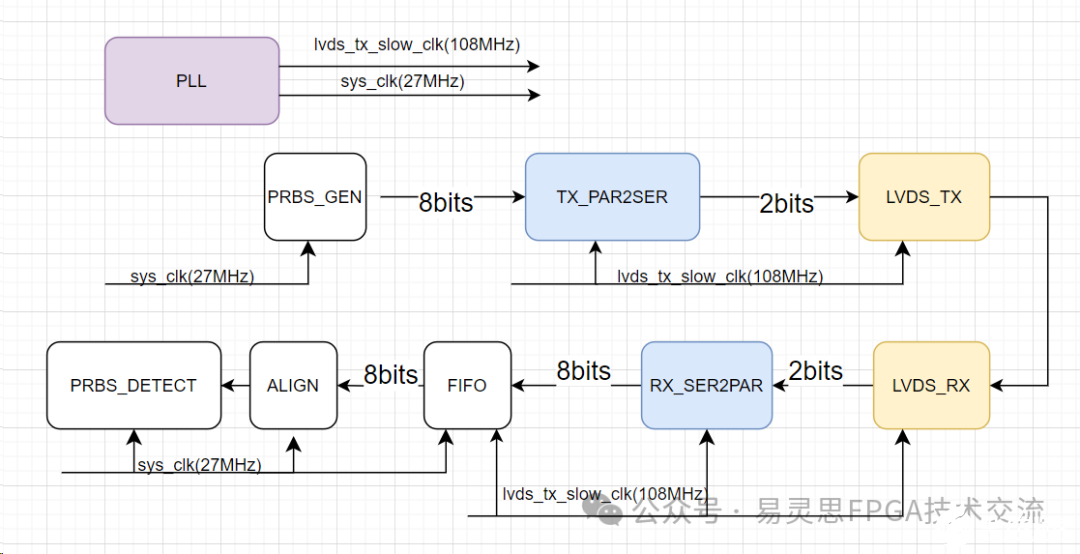

在易靈思的器件上接收LVDS一般采用PLL接收,通過PLL產生兩個時鐘,一個是fast_clk,一個是slow_clk,分別用于處理串行數據和并行數據。

但是如果LVDS的速率比較低時,另外想通過去掉PLL來節省功耗時,也可以直接用lvds_rx_clk直接走GCLK的方式來處理。下面我們來說明一下:

硬件環境如下:

打開interface在里面設置LVDS

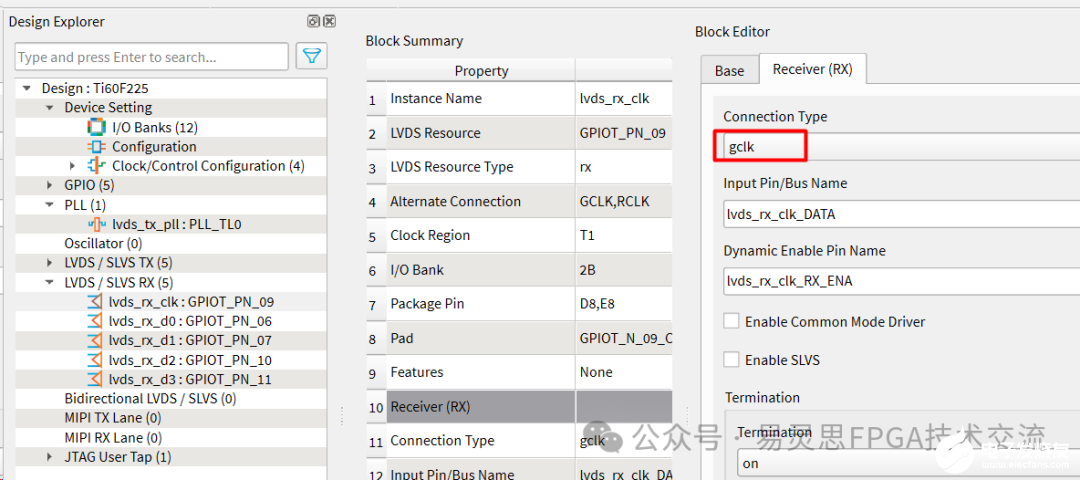

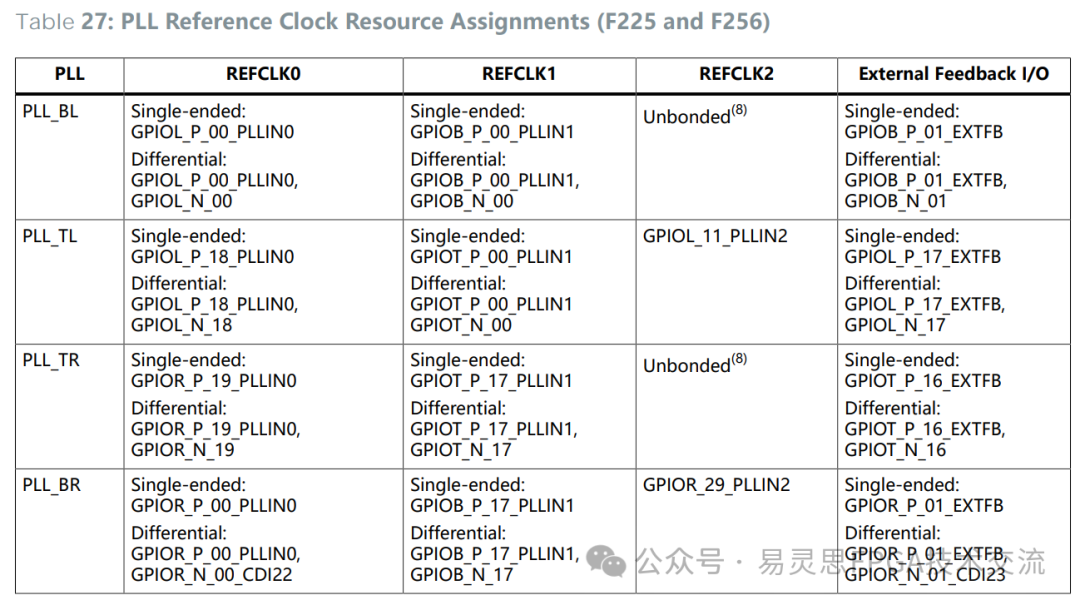

LVDS的時鐘接收Connection Type選擇gclk。

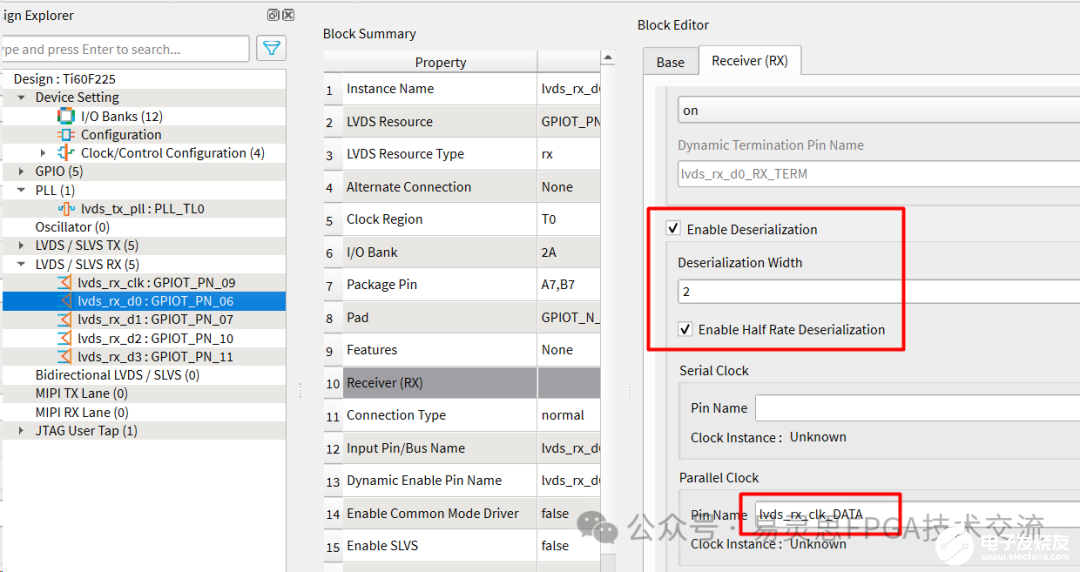

對于數據設置串化因子為2,并輸入Parallel Clock名字為上面定義的時鐘。

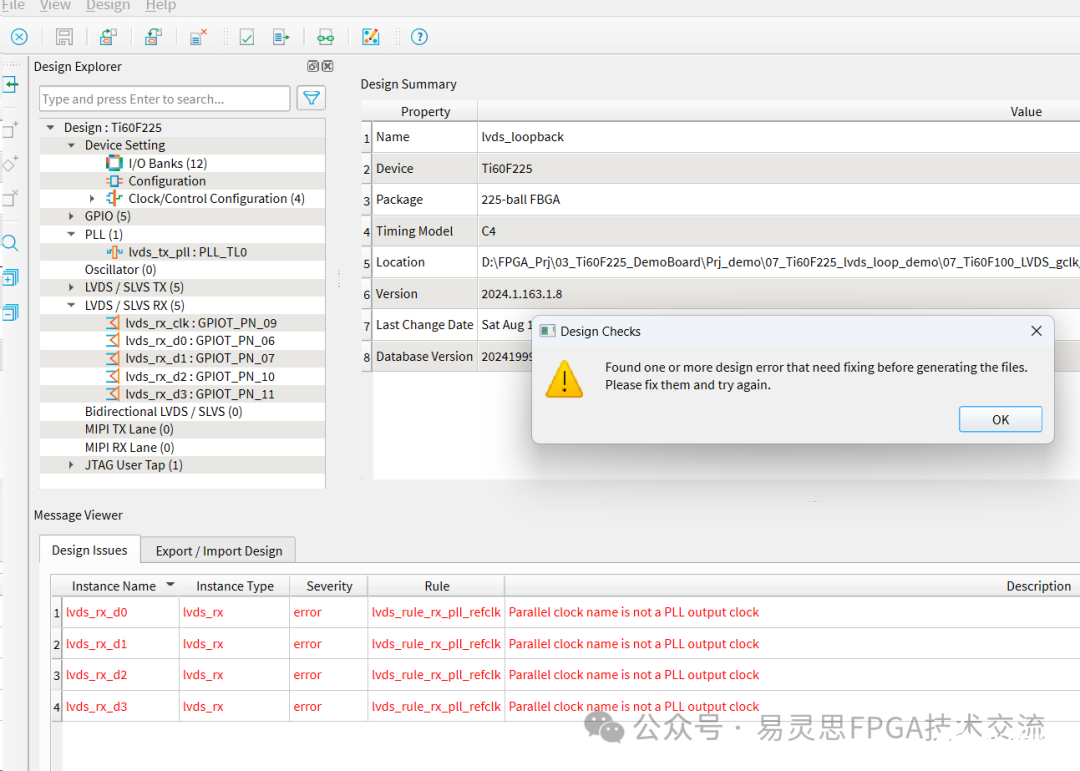

在一切都設置好之后需要生成約束。但是會報以下錯誤。

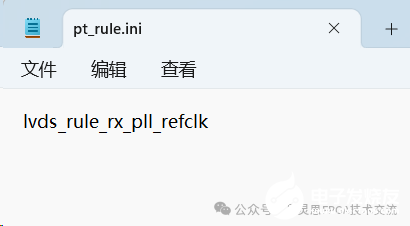

但是解決辦法是有的。在工程目錄下新建pt_rule.ini文件,輸入lvds_rule_rx_pll_refclk,再次生成結束可以正常。

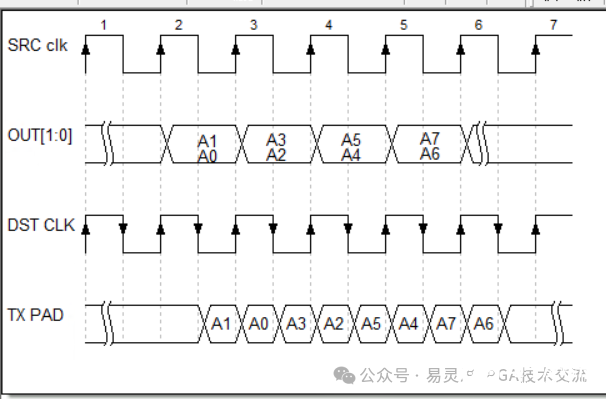

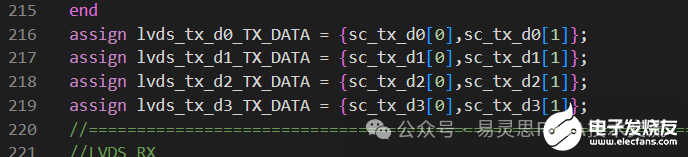

另外注意在發送過程中發送的數據存在高低位需要順序取反的問題。

程序框圖如下:

-

FPGA

+關注

關注

1644文章

21993瀏覽量

615491 -

lvds

+關注

關注

2文章

1120瀏覽量

67222 -

易靈思

+關注

關注

5文章

55瀏覽量

5174

發布評論請先 登錄

Freescale V1 ColdFire處理器

LVDS的GCLK接收方案-v1

LVDS的GCLK接收方案-v1

評論