在當今高速發展的通信技術中,時鐘恢復已成為實現高速串行數據傳輸的關鍵。這項技術廣泛應用于以太網、PCI Express、Aurora等通信協議中,成為這些系統達到高帶寬傳輸不可或缺的一部分。本文將深入探討時鐘恢復的原理、其在SERDES系統中的應用。

時鐘恢復的核心目的是從一個高速串行數據流中提取出嵌入的時鐘信號,以便數據接收端能夠正確地采樣和解析接收到的數據。這一過程的關鍵在于僅通過數據信道本身來傳遞信息,而不單獨傳輸一個時鐘信號。這種方法大幅簡化了傳輸介質的復雜度,并提升了傳輸效率。

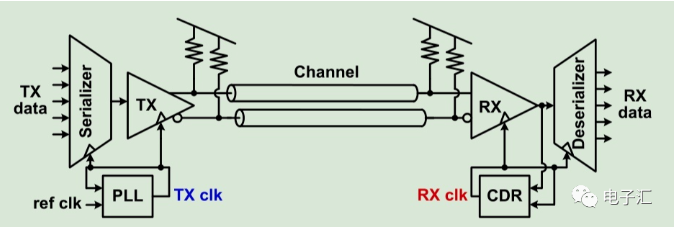

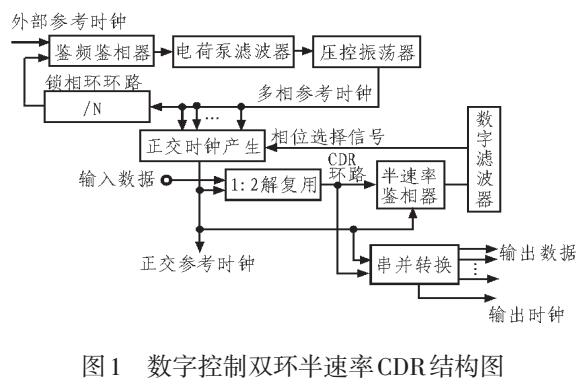

SERDES是一種在發送端將并行數據轉換為串行數據,并在接收端進行相反操作的設備。在這一過程中,時鐘恢復發揮著至關重要的作用。在發送端,CDR(時鐘數據恢復)技術首先被用來將數據進行8b/10b編碼,然后以特定的速率發送出去。這一編碼方法確保了數據線上0和1的數量平衡,減少了碼間干擾,同時提供了豐富的數據邊沿,這對于接收端鎖定相位至關重要。接收端的CDR模塊則負責從接收到的串行數據流中鎖定相位,并按照恢復出的時鐘對數據進行正確的位對齊和字對齊。

在高速數據傳輸和長距離傳送的場景下,CDR協議面臨著極大的設計挑戰。為了適應不同的數據傳輸速率和距離,CDR系統必須擁有高度的靈活性和穩定性。這要求發送器和接收器能夠在不同的工作條件下,快速準確地鎖定和恢復時鐘。解決這一問題的關鍵在于優化8b/10b編碼方案和接收器的相位鎖定算法,以提高系統的適應性和魯棒性。

與傳統的并行傳輸方式相比,采用時鐘恢復的串行傳輸方式在高速數據傳輸領域具有明顯優勢。傳統的并行傳輸由于信號線較多,易受線路間的串擾影響,且隨著傳輸速率的提高,信號完整性問題變得更加突出。而基于時鐘恢復的串行傳輸方式,通過減少信號線的使用,降低了信號衰減和干擾,使得傳輸更加穩定可靠,同時能夠支持更高的數據傳輸速率,滿足現代高速通信需求。

-

數據傳輸

+關注

關注

9文章

2015瀏覽量

66038 -

信號

+關注

關注

11文章

2851瀏覽量

78229 -

時鐘恢復

+關注

關注

0文章

8瀏覽量

8741

發布評論請先 登錄

基于PLL的測試測量時鐘恢復方案

如何用CyPress做USB音頻的時鐘恢復?

DS26504 pdf datasheet(時鐘恢復器件芯片

使用LMK03000C來清除恢復時鐘的抖動

高速非歸零碼數據的全光時鐘恢復研究

時鐘恢復及波形整理器件TRU-050

10Gb/s時鐘數據恢復電路行為級模型研究

基于FPGA的高速時鐘數據恢復電路的實現

時鐘是怎么恢復的?

基于高速CMOS時鐘的數據恢復電路設計與仿真

一文看懂時鐘是怎么恢復的?

一文看懂時鐘是怎么恢復的?

時鐘恢復的原理及設計挑戰

時鐘恢復的原理及設計挑戰

評論