一、Bit Bang

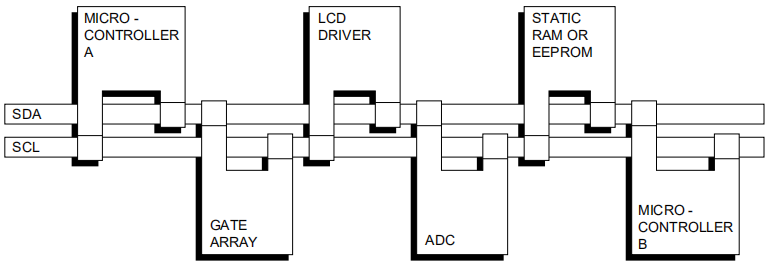

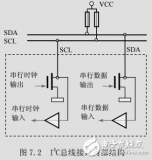

關于 Bit Bang 的解釋:Use software to control serial communication at general-purpose I/O pins,簡單來講就是使用軟件通過 IO 腳去實現 I2C 的時序從而使用 I2C 協議進行通信。

這樣做的好處是可以突破硬件上的限制,例如芯片不具有硬件 I2C 模塊,或者硬件 I2C 模塊損壞,又或者使用硬件 I2C 模塊時布線非常麻煩。壞處是需要寫代碼模擬時序,根據不同的硬件平臺和不同的時鐘頻率,代碼中的部分參數是不一樣的。

二、代碼分析

使用軟件模擬 I2C 的步驟如下:

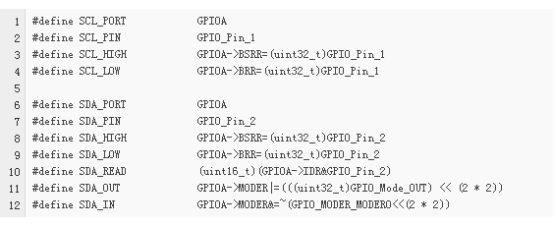

1、設置 GPIO 管腳

設置兩個管腳作為 SCL 和 SDA,例如 GPIOA1 和 GPIOA2

2、SCL時鐘周期

3、附加設置

這里主要是使用宏定義模擬函數

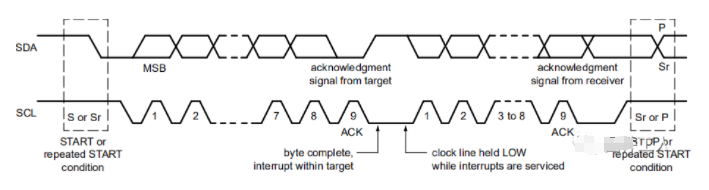

4、I2C 啟動

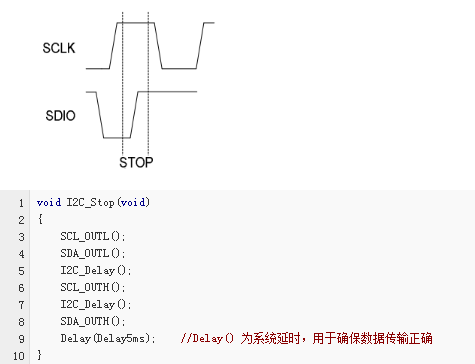

5、I2C停止

6、發送 8 位數據,返回值為從響應 ACK 標志

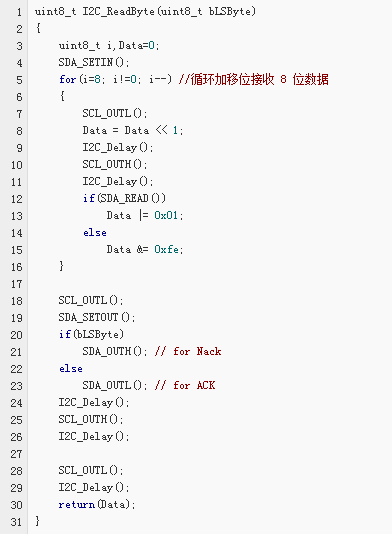

7、接收 8 位數據

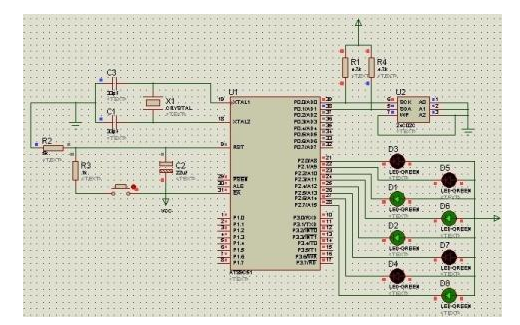

三、操作實例

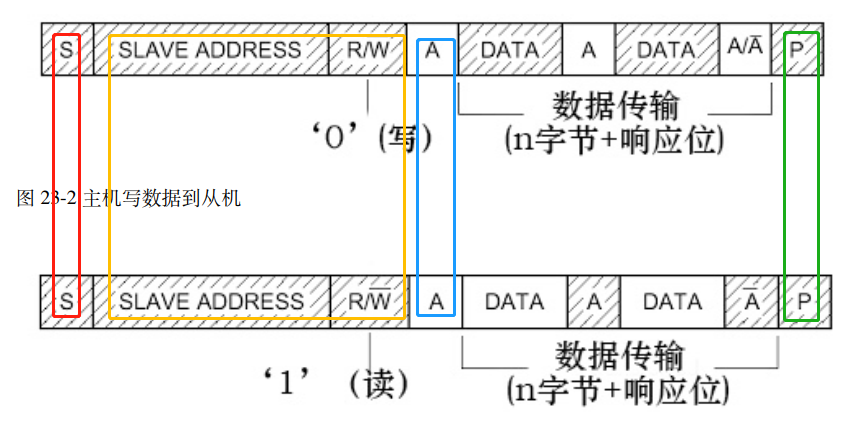

以下代碼為通過調用上面的基本代碼來實現 I2C 通信

三個參數分比為從機地址,寄存器地址,8 位數據

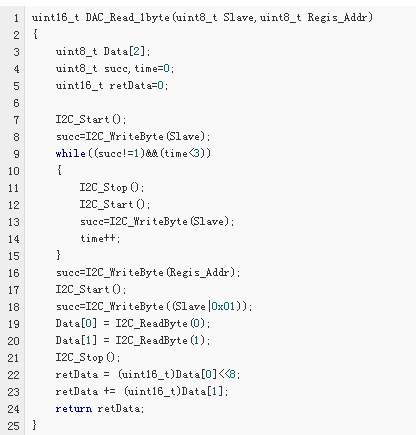

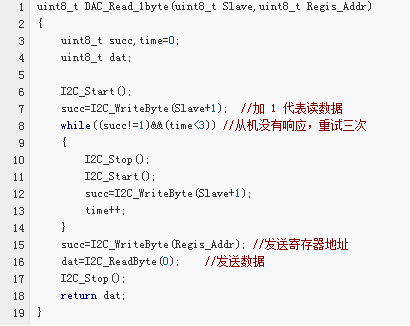

2、讀取 DAC 寄存器的值

兩個參數分別為從機地址,寄存器地址,返回數據為 16 位。這是由于某些器件的硬件設計,采用 7 位表示寄存器地址,而每個寄存器包含 9 位數據。更常見的方式為 8 位寄存器地址,一個寄存器 8 位數據,這種方式的代碼僅返回 8 位數據,見代碼 2。

代碼 1,返回 16 位數據,不常見

代碼 2,返回 8 位數據

-

IO腳

+關注

關注

0文章

3瀏覽量

6656

原文標題:學會這個技術,再也不怕芯片不具有硬件I2C模塊了!

文章出處:【微信號:weixin21ic,微信公眾號:21ic電子網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

GPIO模擬I2C總線的驅動設計與實現

I2C讀寫時序分析和實現思路

DSP配置I2C通訊(非IO口軟件模擬時序)

嵌入式內核及驅動開發-09IIC子系統框架使用(I2C協議和時序,I2C驅動框架,I2C從設備驅動開發,MPU6050硬件連接

經過驗證的GPIO模擬I2C時序代碼

軟件模擬i2c實現io腳時序電路的技巧

軟件模擬i2c實現io腳時序電路的技巧

評論