SPI由于接口相對簡單(只需要4根線),用途算是比較廣泛,主要應用在 EEPROM,FLASH,實時時鐘,AD轉換器,還有數字信號處理器和數字信號解碼器之間。即一個SPI的Master通過SPI與一個從設備,即上述的那些Flash,ADC等,進行通訊。而主從設備之間通過SPI進行通訊,首先要保證兩者之間時鐘SCLK要一致,互相要商量好了,要匹配,否則,就沒法正常通訊了,即保證時序上的一致才可正常訊。而這里的SPI中的時鐘和相位,指的就是SCLk時鐘的特性,即保證主從設備兩者的時鐘的特性一致了,以保證兩者可以正常實現SPI通訊。SPI的極性Polarity和相位Phase,最常見的寫法是CPOL和CPHA,不過也有一些其他寫法,簡單總結如下:(1) CKPOL (Clock Polarity) = CPOL = POL = Polarity = (時鐘)極性(2) CKPHA (Clock Phase) = CPHA = PHA = Phase = (時鐘)相位(3) SCK=SCLK=SPI的時鐘(4) Edge=邊沿,即時鐘電平變化的時刻,即上升沿(rising edge)或者下降沿(falling edge)對于一個時鐘周期內,有兩個edge,分別稱為:(1)Leading edge=前一個邊沿=第一個邊沿,對于開始電壓是1,那么就是1變成0的時候,對于開始電壓是0,那么就是0變成1的時候;(2)Trailing edge=后一個邊沿=第二個邊沿,對于開始電壓是1,那么就是0變成1的時候(即在第一次1變成0之后,才可能有后面的0變成1),對于開始電壓是0,那么就是1變成0的時候;

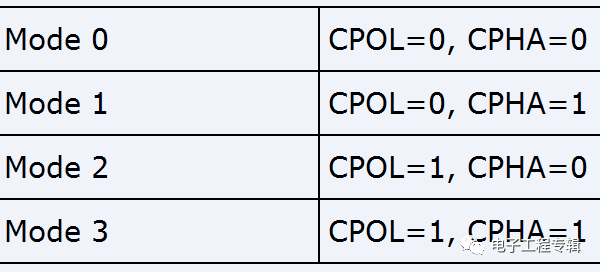

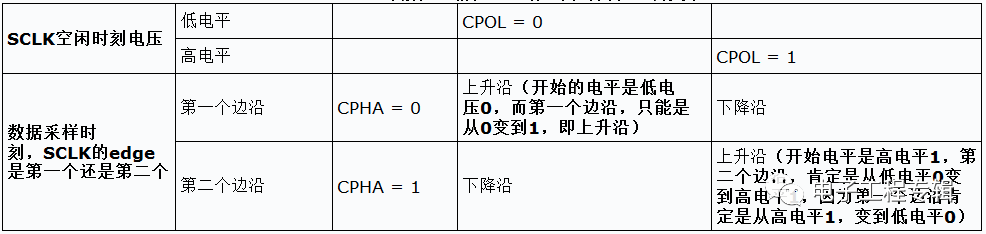

本文采用如下用法:極性=CPOL相位=CPHASCLK=時鐘第一個邊沿和第二個邊沿CPOL和CPHA,分別都可以是0或時1,對應的四種組合就是:

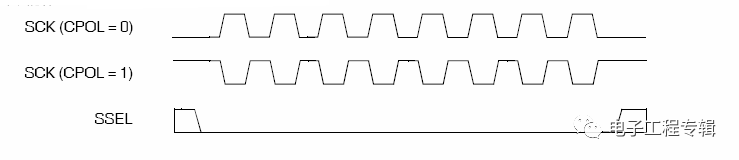

下面詳細介紹。CPOL極性先說什么是SCLK時鐘的空閑時刻,其就是當SCLK在發送8個bit比特數據之前和之后的狀態,于此對應的,SCLK在發送數據的時候,就是正常的工作的時候,有效active的時刻了。其英文精簡解釋為:Clock Polarity = IDLE state of SCK。SPI的CPOL,表示當SCLK空閑idle的時候,其電平的值是低電平0還是高電平1:CPOL=0,時鐘空閑idle時候的電平是低電平,所以當SCLK有效的時候,就是高電平,就是所謂的active-high;CPOL=1,時鐘空閑idle時候的電平是高電平,所以當SCLK有效的時候,就是低電平,就是所謂的active-low;

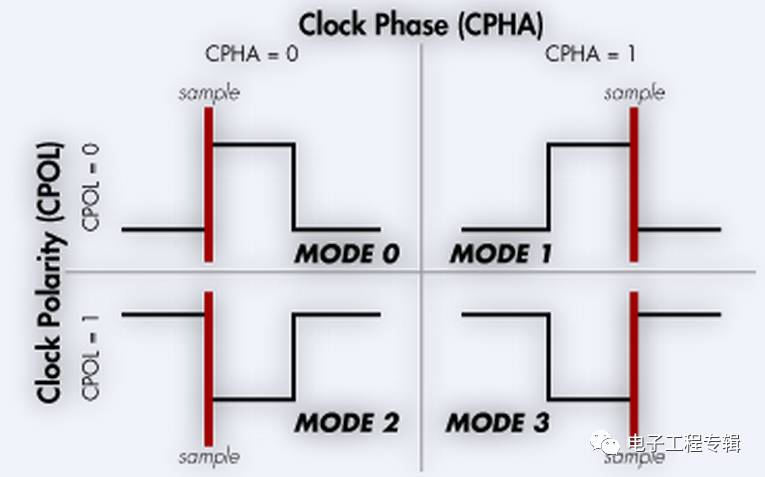

從上圖中可以看出,(CPOL=0)的SCK 波形,它有(傳輸)8 個脈沖,而在脈沖傳輸前和完成后都保持在【低電平狀態】。此時的狀態就是時鐘的空閑狀態或無效狀態,因為此時沒有脈沖,也就不會有數據傳輸。同理得出,(CPOL=)1 的圖,時鐘的空閑狀態或無效狀態時SCK 是保持【高電平的】。CPHA相位首先說明一點,capture strobe = latch = read = sample,都是表示數據采樣,數據有效的時刻。相位,對應著數據采樣是在第幾個邊沿(edge),是第一個邊沿還是第二個邊沿,0對應著第一個邊沿,1對應著第二個邊沿。

對于:CPHA=0,表示第一個邊沿:對于CPOL=0,idle時候的是低電平,第一個邊沿就是從低變到高,所以是上升沿;對于CPOL=1,idle時候的是高電平,第一個邊沿就是從高變到低,所以是下降沿;CPHA=1,表示第二個邊沿:對于CPOL=0,idle時候的是低電平,第二個邊沿就是從高變到低,所以是下降沿;對于CPOL=1,idle時候的是高電平,第一個邊沿就是從低變到高,所以是上升沿;

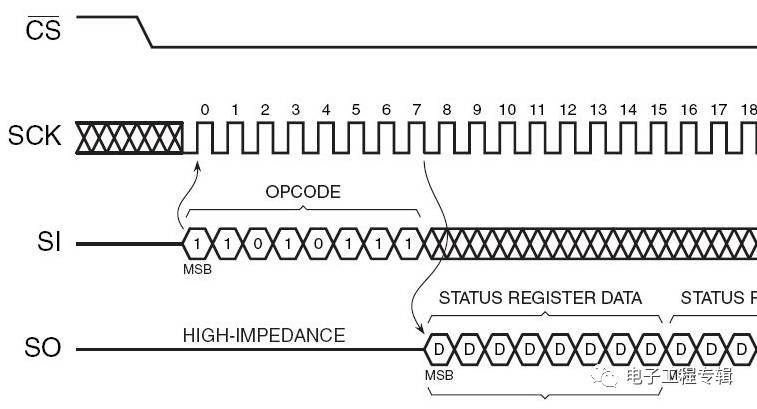

我們看上面的圖,發現數據 SI 是對應 SCK 的第一個時鐘沿,再仔細看,數據是在SCK的第一個時鐘邊沿保持穩定【數據被采樣捕獲】,在下一個邊沿改變【SCK 的下降沿數據改變】因此我們得出結論:該系列FLASH 是【數據在第一個時鐘沿被采樣捕獲】或【數據在SPCK 起始邊沿捕獲,在SPCK 下一個邊沿改變】如何判斷CPOL和CPHA如果起始的SCLK的電平是0,那么CPOL=0,如果是1,那么CPOL=1,然后看數據采樣時刻,即時序圖數據線上的數據那個矩形區域的中間所對應的位置,對應到上面SCLK時鐘的位置,對應著是第一個邊沿或是第二個邊沿,即CPHA是0或1。(對應的是上升沿還是還是下降沿,要根據對應的CPOL的值,才能確定)。(1)如何判斷CPOL:SCLK的空閑時候的電壓,是0還是1,決定了CPOL是0還是1;(2)如何判斷CPHA:而數據采樣時刻對應著的SCLK的電平,是第一個邊沿還是第二個邊沿,對應著CPHA為0還是1。

SCLK的極性,相位,邊沿之間的內在邏輯

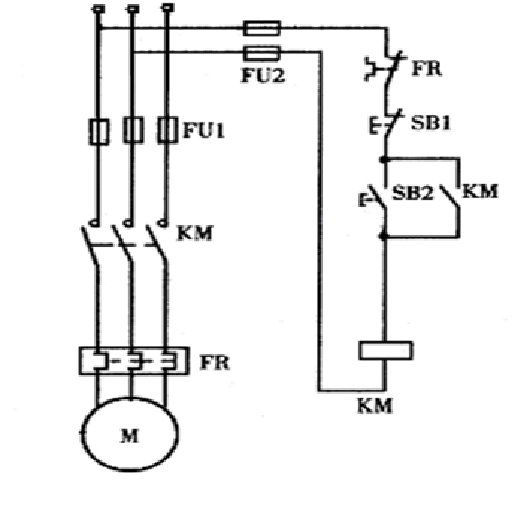

最后來看一下S3C2440的SPI的CPOL和CPHA,結合前面講的理論知識,下面的圖就很好理解啦!

-

AD轉換器

+關注

關注

4文章

250瀏覽量

42091 -

CPOL

+關注

關注

0文章

9瀏覽量

10210 -

相位coha

+關注

關注

0文章

1瀏覽量

1900

原文標題:詳解SPI中的極性CPOL和相位CPHA

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

多年私藏的電源電路圖錦集

《電子懶人的基礎硬件電路圖講解》

超全電源電路圖詳解!

電源電路圖深度講解

電路小知識 | 電源選型要點、電路圖的解讀方法、LED及其應用示例

談談有哪些電路圖

PCBA加工全流程解析:電子制造的關鍵環節

原理圖和電路圖區別在哪 電氣控制電路圖介紹

cpol和相位coha電路圖全解析

cpol和相位coha電路圖全解析

評論