一、引言

微處理器,作為現(xiàn)代計(jì)算機(jī)的核心部件,負(fù)責(zé)執(zhí)行存儲(chǔ)在內(nèi)存中的指令,完成各種計(jì)算和控制任務(wù)。指令的執(zhí)行過程不僅體現(xiàn)了微處理器的設(shè)計(jì)思想和架構(gòu)特點(diǎn),還直接影響到計(jì)算機(jī)的性能和效率。

二、微處理器執(zhí)行指令的基本過程

微處理器執(zhí)行指令的過程大致可以分為以下幾個(gè)階段:取指令、譯碼、執(zhí)行和寫回。這四個(gè)階段相互配合,共同完成指令的執(zhí)行任務(wù)。

1. 取指令階段

取指令階段是微處理器執(zhí)行指令的第一步,其主要任務(wù)是從內(nèi)存中讀取指令。在這一階段,微處理器會(huì)根據(jù)程序計(jì)數(shù)器(PC)中存儲(chǔ)的地址,從內(nèi)存中取出下一條將要執(zhí)行的指令,并將該指令存儲(chǔ)到指令寄存器(IR)中。程序計(jì)數(shù)器是一個(gè)特殊的寄存器,用于保存當(dāng)前指令的地址,它指向內(nèi)存中存儲(chǔ)的下一條指令的位置。當(dāng)一條指令被執(zhí)行后,程序計(jì)數(shù)器的值會(huì)自動(dòng)更新為下一條指令的地址,以確保指令的連續(xù)執(zhí)行。

2. 譯碼階段

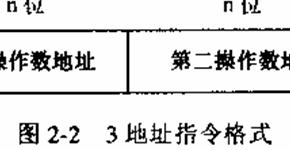

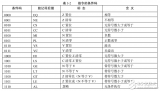

譯碼階段是微處理器執(zhí)行指令的第二步,其主要任務(wù)是對(duì)指令進(jìn)行解析。在這一階段,微處理器會(huì)根據(jù)指令寄存器中存儲(chǔ)的指令,確定指令的操作碼和操作數(shù)。操作碼是指令中用于指示操作類型的部分,它告訴微處理器需要執(zhí)行什么類型的操作;而操作數(shù)則是指令中用于指示操作對(duì)象的部分,它告訴微處理器操作的具體對(duì)象是什么。通過解析操作碼和操作數(shù),微處理器可以明確指令的具體要求,并為后續(xù)的執(zhí)行階段做好準(zhǔn)備。

3. 執(zhí)行階段

執(zhí)行階段是微處理器執(zhí)行指令的核心階段,其主要任務(wù)是執(zhí)行指令中指定的操作。在這一階段,微處理器會(huì)根據(jù)操作碼和操作數(shù)的信息,調(diào)用相應(yīng)的功能部件(如算術(shù)邏輯單元ALU、浮點(diǎn)運(yùn)算單元FPU等)來執(zhí)行具體的操作。例如,如果指令是加法指令,微處理器就會(huì)將操作數(shù)相加,并將結(jié)果存儲(chǔ)到指定的寄存器或內(nèi)存中。執(zhí)行階段的速度和效率直接影響到整個(gè)計(jì)算機(jī)的性能和響應(yīng)速度。

4. 寫回階段

寫回階段是微處理器執(zhí)行指令的最后一步,其主要任務(wù)是將執(zhí)行結(jié)果寫回到內(nèi)存或寄存器中。在這一階段,微處理器會(huì)將執(zhí)行階段得到的結(jié)果存儲(chǔ)到指定的寄存器或內(nèi)存地址中。如果指令需要讀取內(nèi)存中的數(shù)據(jù),微處理器也會(huì)在這一階段將數(shù)據(jù)讀取到寄存器中以便后續(xù)使用。寫回階段的完成標(biāo)志著一條指令的執(zhí)行結(jié)束,此時(shí)程序計(jì)數(shù)器會(huì)更新為下一條指令的地址,微處理器將開始下一個(gè)指令周期的執(zhí)行。

三、微處理器執(zhí)行指令過程中的關(guān)鍵要素

在微處理器執(zhí)行指令的過程中,有幾個(gè)關(guān)鍵要素起著至關(guān)重要的作用:

1. 寄存器

寄存器是微處理器內(nèi)部的高速存儲(chǔ)單元,用于存儲(chǔ)指令執(zhí)行過程中的數(shù)據(jù)和地址。指令寄存器(IR)、程序計(jì)數(shù)器(PC)、數(shù)據(jù)寄存器(DR)等不同類型的寄存器在指令執(zhí)行過程中發(fā)揮著不同的作用。它們不僅提高了數(shù)據(jù)的存取速度,還簡化了指令的執(zhí)行流程。

2. 總線

總線是微處理器內(nèi)部各部件之間以及微處理器與外部設(shè)備之間傳輸數(shù)據(jù)的通道。在指令執(zhí)行過程中,數(shù)據(jù)和指令需要通過總線在微處理器的各個(gè)部件之間進(jìn)行傳輸。總線的性能和帶寬直接影響到指令的執(zhí)行速度和系統(tǒng)的整體性能。

3. 控制單元

控制單元是微處理器的核心部件之一,它負(fù)責(zé)協(xié)調(diào)各個(gè)部件的工作并控制指令的執(zhí)行流程。在指令執(zhí)行過程中,控制單元會(huì)根據(jù)指令的要求發(fā)出相應(yīng)的控制信號(hào)來調(diào)用不同的功能部件執(zhí)行相應(yīng)的操作。控制單元的設(shè)計(jì)和性能直接影響到微處理器的整體性能和效率。

四、微處理器執(zhí)行指令的優(yōu)化策略

為了提高微處理器執(zhí)行指令的速度和效率,人們采用了多種優(yōu)化策略來改進(jìn)指令的執(zhí)行過程。這些策略包括:

1. 流水線技術(shù)

流水線技術(shù)是一種將指令的執(zhí)行過程分解為多個(gè)階段并并行執(zhí)行的技術(shù)。通過將指令的執(zhí)行過程劃分為取指令、譯碼、執(zhí)行和寫回等多個(gè)階段,并允許這些階段在不同的時(shí)間點(diǎn)上并行執(zhí)行不同的指令,可以顯著提高指令的執(zhí)行速度和系統(tǒng)的吞吐量。

2. 分支預(yù)測技術(shù)

分支預(yù)測技術(shù)是一種用于預(yù)測程序分支執(zhí)行路徑的技術(shù)。在程序執(zhí)行過程中,分支指令的執(zhí)行結(jié)果會(huì)影響到后續(xù)指令的執(zhí)行路徑。通過預(yù)測分支指令的執(zhí)行結(jié)果并提前準(zhǔn)備好相應(yīng)的指令和數(shù)據(jù),可以減少因分支預(yù)測錯(cuò)誤而導(dǎo)致的指令延遲和性能損失。

3. 緩存技術(shù)

緩存技術(shù)是一種用于提高數(shù)據(jù)存取速度的技術(shù)。通過將常用的數(shù)據(jù)和指令存儲(chǔ)在高速緩存中并減少對(duì)主存的訪問次數(shù)來降低存取延遲并提高系統(tǒng)的整體性能。現(xiàn)代微處理器通常采用多級(jí)緩存結(jié)構(gòu)來進(jìn)一步提高緩存的命中率和存取速度。

五、總結(jié)

微處理器執(zhí)行指令的過程是計(jì)算機(jī)操作的核心環(huán)節(jié)之一。通過取指令、譯碼、執(zhí)行和寫回等階段的相互配合和協(xié)作,微處理器能夠完成各種復(fù)雜的計(jì)算和控制任務(wù)。同時(shí),為了提高指令的執(zhí)行速度和效率,人們采用了多種優(yōu)化策略來改進(jìn)指令的執(zhí)行過程。這些策略不僅提高了微處理器的性能和效率還推動(dòng)了計(jì)算機(jī)技術(shù)的不斷發(fā)展和進(jìn)步。

-

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7636瀏覽量

90269 -

微處理器

+關(guān)注

關(guān)注

11文章

2372瀏覽量

83895 -

指令

+關(guān)注

關(guān)注

1文章

615瀏覽量

36268

發(fā)布評(píng)論請先 登錄

微處理器指令集設(shè)計(jì)

微處理器執(zhí)行指令的基本過程

微處理器執(zhí)行指令的基本過程

評(píng)論