剛好在知乎上看到這個(gè)問題如何用FPGA加速卷積神經(jīng)網(wǎng)絡(luò)CNN,恰巧我的碩士畢業(yè)設(shè)計(jì)做的就是在FPGA上實(shí)現(xiàn)CNN的架構(gòu),在此和大家分享。

先說一下背景,這個(gè)項(xiàng)目的目標(biāo)硬件是Xilinx的PYNQ。該開發(fā)板加載了Linux Ubuntu操作系統(tǒng),可以在CPU上運(yùn)行現(xiàn)有的Python CNN架構(gòu)如Caffe和Theano。本設(shè)計(jì)旨在用PYNQ加載的ZYNQ FPGA對(duì)于CNN核心計(jì)算進(jìn)行硬件加速,以達(dá)到對(duì)于大規(guī)模信息流進(jìn)行大吞吐量CNN處理。

該設(shè)計(jì)結(jié)構(gòu)可以分為CPU端(前端)和FPGA端(后端)兩部分。前端使用的是Python,用來與其他軟件項(xiàng)目進(jìn)行交互。前端將數(shù)據(jù)以數(shù)據(jù)流的形式由DDR傳輸?shù)紽PGA kernel。后端的FPGA硬件設(shè)計(jì)使用的是Synchronous Dataflow Paradigm。在這個(gè)結(jié)構(gòu)之下,數(shù)據(jù)流以AXI-Stream的協(xié)議穿梭于每一個(gè)CNN層。每一個(gè)層都使用并行結(jié)構(gòu)加上高性能流水線,使整體吞吐量效率達(dá)到一個(gè)非常可觀的水平。

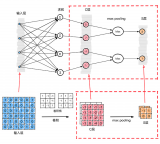

上圖為實(shí)現(xiàn)LeNet-5的硬件結(jié)構(gòu)示意圖。對(duì)于LeNet-5,該設(shè)計(jì)達(dá)到了1.88GOP/S的吞吐量,與PYNQ上的DUAL CORE ARM CPU相比加速約32倍。目前該架構(gòu)可運(yùn)行LeNet和CIFAR10,有教程。

這個(gè)項(xiàng)目結(jié)構(gòu)比較簡(jiǎn)單,適合FPGA初學(xué)者作為研究起點(diǎn)使用。感興趣的話,可以以這個(gè)架構(gòu)為基礎(chǔ)設(shè)計(jì)幾個(gè)CNN的應(yīng)用,或者在它的基礎(chǔ)上進(jìn)行優(yōu)化和再創(chuàng)造。

-

FPGA

+關(guān)注

關(guān)注

1642文章

21918瀏覽量

611966 -

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4797瀏覽量

102308

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【PYNQ-Z2申請(qǐng)】基于PYNQ的卷積神經(jīng)網(wǎng)絡(luò)加速

基于賽靈思FPGA的卷積神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)設(shè)計(jì)

卷積神經(jīng)網(wǎng)絡(luò)如何使用

卷積神經(jīng)網(wǎng)絡(luò)簡(jiǎn)介:什么是機(jī)器學(xué)習(xí)?

卷積神經(jīng)網(wǎng)絡(luò)CNN圖解

卷積神經(jīng)網(wǎng)絡(luò)CNN架構(gòu)分析-LeNet

簡(jiǎn)單快捷地用小型Xiliinx FPGA加速卷積神經(jīng)網(wǎng)絡(luò)CNN

簡(jiǎn)單快捷地用小型Xiliinx FPGA加速卷積神經(jīng)網(wǎng)絡(luò)CNN

評(píng)論