在FPGA中實現在應用編程(In Application Pro—gramming,IAP)有兩種方法:一種是,在電路板上加外電路。例如用MCU或CPLD來接收配置數據,在被動串行(PS)模式下由外電路編程FPGA或是編程Flash器件(包括EPCS和Flash),然后控制FPGA的配置復位引腳來復位整個FPGA,最后FPGA采用主串方式進行自我配置。另一種是,通過FPGA中的Nios CPU或是專用IP來接收編程數據,并編程Flash芯片,然后通過外部簡單電路將FPGA復位啟動,以主動串行(AS)模式進行配置。

為了減小電路板面積,節約成本,提高可靠性,本設計采用第二種方法。本設計的要求是:硬件電路須配置為主動串行模式,即選擇MSEL[1:O]為l:O;具備EPCS,或同時具備EPCS和Flash;具有與PC機通信的功能。FPGA接收更新數據,并將其存入Flash器件,然后復位Nios或FPGA對軟硬件進行更新。

1 系統的硬件設計

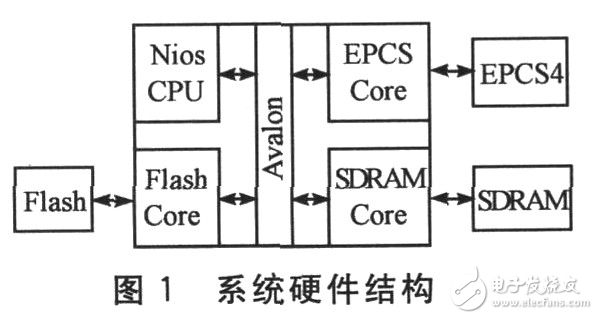

系統主要由Cyclone FPGA、EPCS、Flash和串行通信等組成,硬件結構如圖1所示。

點擊看原圖

EPCS采用Altera公司的EPCS4,容量達到4 Mb,引腳較少,成本低,支持3.3 V低電壓操作。Flash芯片采用AMD公司的Am29LV640MH/L,支持3.O V低電壓操作,具有低功耗特性,芯片容量為64 Mb,滿足大容量數據的存儲;并口操作,與Cyclone FPGA完全兼容,而且在SOPC中有與之對應的CFI_FLASH核,便于硬件電路的設計。

2 工作原理

2.1 幾個概念

FPGA配置數據:是sof文件,將sof文件編程到Flash中,上電后FPGA可以從Flash中配置。sof文件是其他配置文件的基礎,其他文件均可由sof文件轉換得到。

軟件數據:通過NiosII IDE創建elf文件,將用戶程序編程到Flash中,允許復位后從F1ash中加載軟件程序,從而啟動NiosII CPU。

2.2 編程文件

編程文件為Flash格式的文件,即S—reeorld(簡稱“SREC”)格式。SREC格式是Motorola公司制定的一種燒寫格式標準。SREC格式文件是由一組ASCII碼組成,所有的十六進制數據均為大寫形式,結構說明如下:

①起始代碼。以S作為一個數據行的開始。

②記錄類型。1個十進制數字(O~9),定義數據域的類型。

③字節數。1個字節,定義字節數之后除地址字節、校驗字節之外其他字節的個數。

④地址。由4(或6、8)個字節組成,定義了第一個數據字節存儲的位置。

⑤數據字節。由n個字節組成,數據字節為實際有效的編程信息。

⑥校驗字節。1個字節,作校驗使用,所有十六進制字節相加后取8位,為0xFF。

2.3 AS配置模式

FPGA的配置數據存儲在內部SRAM單元中。由于SRAM掉電后數據會丟失,因此每次上電時必須重新將配置數據寫入SRAM中。這個過程稱為“FPGA的配置”。由此可見,FPGA的配置信息是存儲在FPGA內部RAM當中的。可知在主動串行模式下,FPGA將配置數據從EPGS中讀取,然后存入內部RAM中。

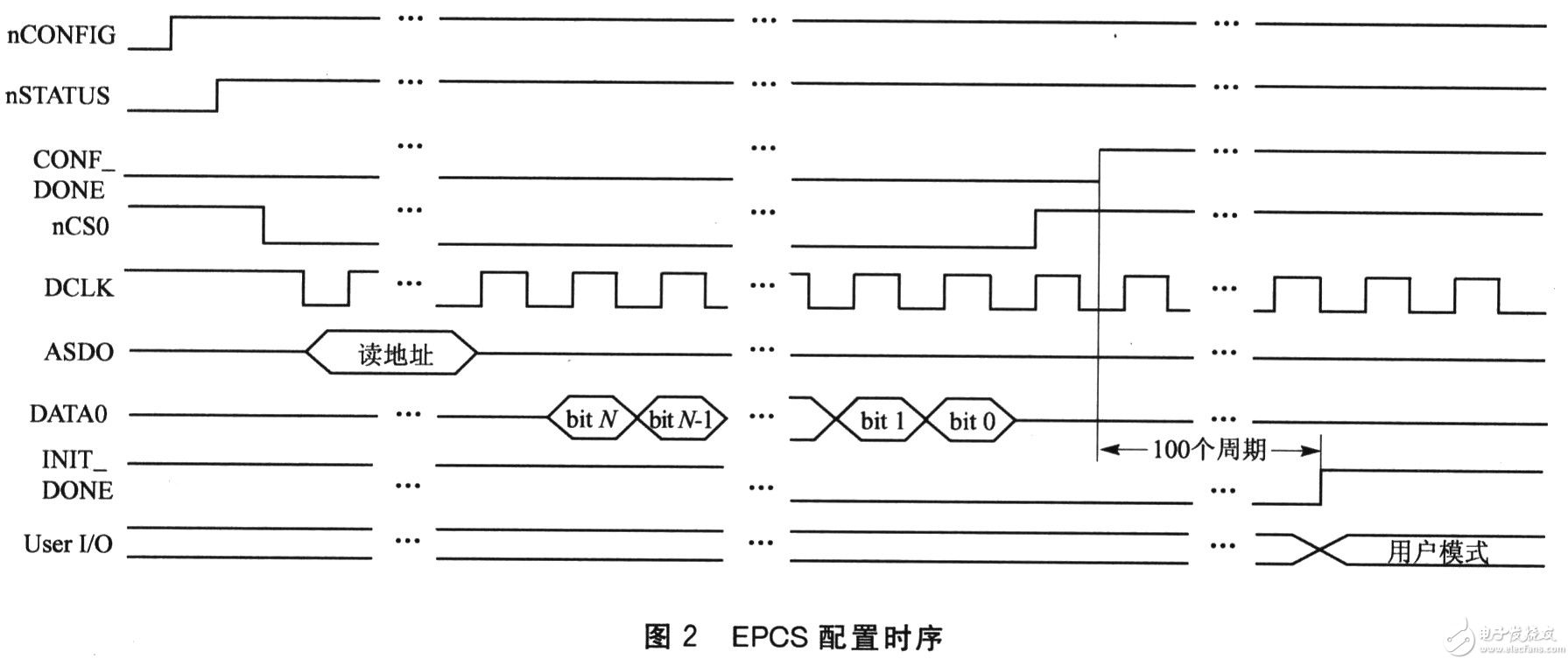

AS配置模式支持StratixII和Cyclone系列的FPGA,通過配置MSEL[1:O]為1:0,選擇主動配置模式(除JTAG模式不受MSEL控制外,其他配置方式均由MSEL決定)。AS配置模式使用串行配置器件(EPCS1/EPCS4/EPCSl6/EPCS64)。在AS配置過程中,StratixlI和Cy—clone系列的FPGA是主設備,串行配置器件為從設備。如圖2所示,在AS配置模式下,FPGA通過DATA0接收配置數據,配置數據和DCLK是同步的。每個時鐘周期傳輸1位配置數據。通過控制nCONFIG、nSTATUS、CONF_DONE來表示配置過程。串行配置芯片在DCLK上升沿時鎖存輸入信號和控制信號,在下降沿時輸出配置數據。Cyclone芯片在DCLK下降沿時輸出控制信號,并鎖存配置數據。

點擊看原圖

3 工作流程

3.1 硬件配置的更新

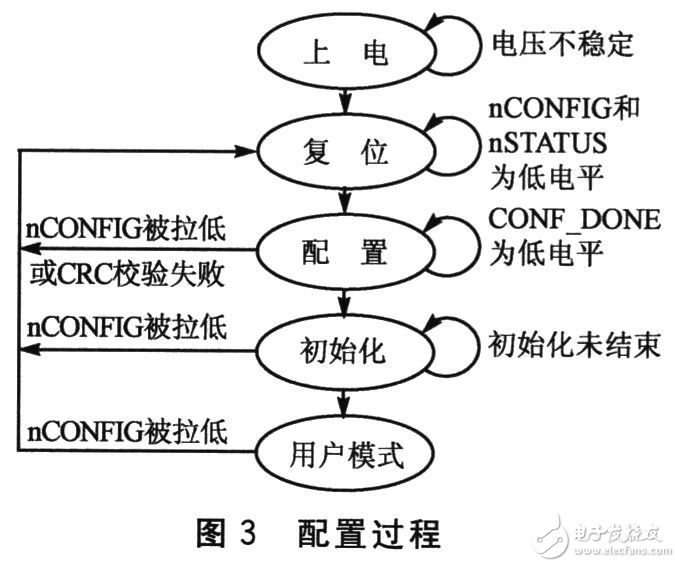

如圖3所示,FPGA的配置過程分為:復位、配置和初始化。

點擊看原圖

(1)復位FPGA

上電復位:在用戶模式下,當nCONFIG引腳持續低電平40μs時,FPGA將進入復位狀態。復位時,FP—GA采樣MSEL引腳的電平值,以確定采用的配置方式;同時,nSTATUS和CONF_DONE引腳由FPGA置為低電平,所有I/0引腳為三態且FPGA內部配置寄存器被清空。

FPGA復位的2種方法:

①外加RC復位電路或者復位芯片,自動產生上電復位脈沖。

②參考芯片手冊。如果芯片提供了上電復位脈沖(一般是全局復位信號),則使用它作為復位信號;若沒有提供,則查找芯片是否給出了寄存單元上電默認值(一般是O),利用該特性復位或者產生復位脈沖。

(2)配置FPGA

復位后,nCONFIG被外部上拉電阻拉高,進入配置階段。此時,nSTATUS被FPGA釋放并由外部上拉電阻拉為高電平后進入配置狀態。Cyclone芯片通過將nCSO輸出的信號置低來使能串行配置芯片,nCS0引腳連接配置芯片的片選段(nCS),用串行時鐘(DCLK)和串行數據輸出(ASDO)引腳來發送操作指令,及/或將地址信號讀到串行配置芯片中。接著配置芯片將數據送到串行數據輸出(DATA)引腳,DATA引腳連接Cyclone芯片的DATA0輸入腳。配置數據在DCLK時鐘的上升沿載入FPGA。當接收完所有的配置位后(CRC校驗無誤),Cyclone芯片懸空CONF_DONE引腳,該引腳由外部10 kΩ電阻拉高;同時,停止驅動DCLK信號。只有當CONF_DONE到達一定的邏輯高電平后,初始化才開始。

(3)初始化階段

在Cyclone芯片中,初始時鐘源是Cyclone芯片的lOMHz(典型的)內部晶振,或者是可供選擇的CLKUSR引腳。內部晶振是默認的初始化時鐘源。如果用了內部時鐘,則Cyclone芯片為正確的初始化提供足夠的時鐘。使用內部時鐘的好處在于,初始化時不需要從外部發送其他的時鐘到CLKUSR引腳,而且可以把CLKUSR引腳當作I/O引腳。

(4)用戶模式

初始化結束后,FPGA進入用戶模式。在用戶模式下,用戶I/O引腳不再有弱上拉電阻,而是執行設計中分配的功能。Cyclone芯片可以通過將nCONFIG拉低而開始重新配置。nCONFIG低信號應該至少持續40μs。當nCONFIG被拉低時,Cyclone芯片被復位并進入復位階段。Cyclone芯片也會把nSTATUS和CONF_DONE拉低,所有的I/O引腳處于三態。一旦nCONFIG回到邏輯高電平,Cyclone芯片將釋放nSTATUS,重新開始配置。

(5)配置時出現的錯誤

如果在配置時出現錯誤,則Cyclone芯片將nSTA—TUS信號置低來表明一個數據幀錯誤,CONF_DONE信號為低。如果在Quartus軟件的Device&Pin Options窗口的General項中,選中Auto—restart configuration aftererror選項,則Cyclone芯片通過激活nCSO來實現復位,在復位失效時間(40μs)后釋放nSTATUS,并再次嘗試配置。如果該選項未被選中,則外部系統必須監視nSTA—TUS信號以防出錯,然后將nCONFIG信號拉低并持續至少40μs來重新配置。

計算機與目標板上的Nios程序建立連接,通過通信接口將Flash文件傳輸給FPGA;Nios程序判斷出傳輸文件的針對目標后,將編程數據存放在EPCS或Flash中。接收到的數據首先暫存入SDRAM,而不是直接對EPCS和Flash進行操作。這樣做的好處是,一旦傳輸失敗或中止,不會破壞原有EPCS和Flash中的數據。

通過sof2Flash命令來生成Flash文件時,可以通過SOPC Builder打開NioslI command shell,使用“sof2 Flash—epcs-input=<輸入文件名.sof>一output=<輸出文件名.Flash>”命令,生成的Flash文件存在于工程目錄下。也可以將sof文件復制到“〈quartus安裝目錄〉\kits\nios2_60\examples”下,直接打開NiosII command shell,使用“sof2Flash-epcs—input=<輸入文件名.sof>一output=<輸出文件名.Flash>”,生成的Flash文件存在于“〈quartus安裝目錄〉\kits\nios2_60\examples”下。

-

FPGA

+關注

關注

1646文章

22069瀏覽量

619646

發布評論請先 登錄

基于SPI FLASH的FPGA多重配置

FPGA中SPI復用配置的編程方法

采用Flash和JTAG接口實現FPGA多配置系統設計

使用高速SPI Nor Flash的FPGA配置

使用CPLD和Flash實現FPGA的配置

FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法

關于fpga編程flash芯片和配置數據技巧

關于fpga編程flash芯片和配置數據技巧

評論