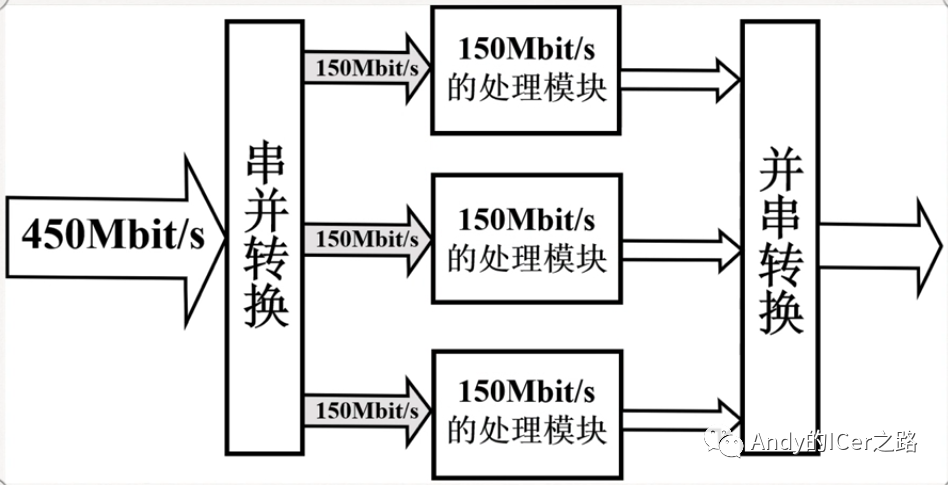

速度和面積互換原則。以面積換速度可以實現很高的數據吞吐率,其實串/并轉換、就是一種以面積換速度的思想

2.乒乓操作。

3.串/并轉換的思想。

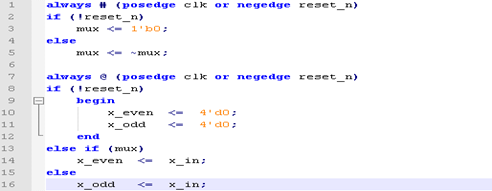

高速數據處理的重要技巧之一。這里我來舉一個多相濾波器抽取的例子:

抽取之后,兩路數據以二分頻的速度進行處理即可

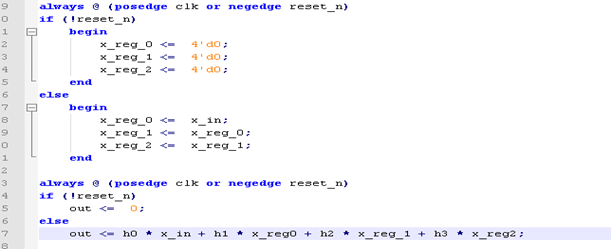

4.流水線設計(在fir濾波器中表現很突出,一個時鐘輸出一個數據)

流水線設計可以從某種程度上提高系統頻率。。前提是:設計可以分為若干步驟進行處理,而且整個數據處理的過程是單向的,即沒有反饋或者逆運算、前一個步驟的輸出是下一個步驟的輸入。。。

5.邏輯復制與模塊復用。

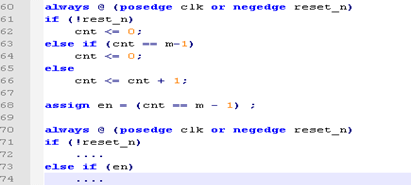

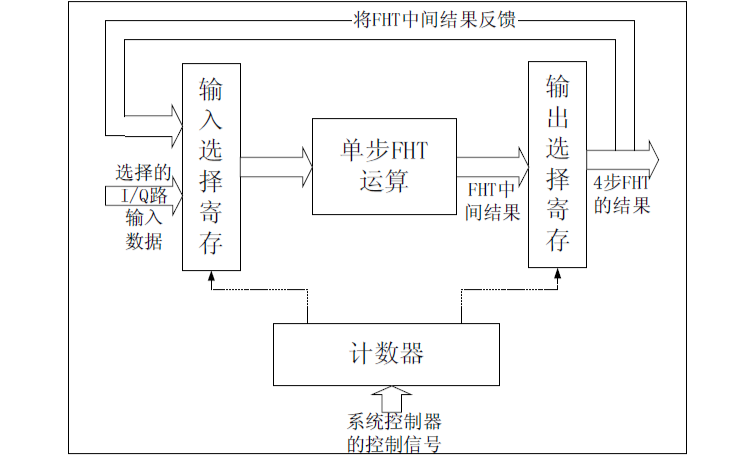

模塊復用在節省邏輯資源方面使用非常廣泛(舉個例子吧)

對比一下,不多說了,一例勝千言!

至于邏輯復制呢,以后再說,目前還沒碰到。把概念先抄上來:邏輯復制是一種通過增加面積來改善時序條件的優化手段,其最重要的應用是調整信號的扇出。換句話說,也就是其扇出非常大,那么為了增加這個信號的驅動能力,就必須插入很多級的Buffer,這樣就在一定程度上增加了這個信號的路徑延時。這種情況下就可以賦值生成這個信號的邏輯,用多路同頻同相的信號驅動后續電路,是平均到每路德扇出變低,這樣就不需要插入Buffer就能滿足驅動能力增加的需求,從而節約該信號的路徑延時。

總之。模塊復用節省面積,犧牲速度,而邏輯復制正好相反。。

6.模塊化設計

就是自頂向下的設計方法。。不討論了、很簡單有很難得東西。

7.時鐘設計技巧

盡量避免使用FPGA內部邏輯產生的時鐘,因為它很容易導致功能或時序出現問題。內部組合邏輯產生的時鐘容易出現毛刺,影響設計的功能實現;組合邏輯固有的延時也容易導致時序問題。

如果采用內部組合邏輯產生的輸出作為時鐘信號或者異步復位信號,可能會不可避免的出現毛刺。如果此時信號正處于變換過程,那么它將違反建立時間和保持時間的要求,從而影響后續電路的輸出狀態,甚至導致整個系統運行失敗。

如果要減少毛刺,最好用時鐘打一下。。達到同步處理的效果。

對于設計中需要用到的分頻時鐘,應該盡量使用使能時鐘,讓分頻信號作為使能信號來使用。

-

FPGA

+關注

關注

1644文章

22004瀏覽量

616258 -

FPGA設計

+關注

關注

9文章

428瀏覽量

27238 -

可編程邏輯

+關注

關注

7文章

524瀏覽量

44651 -

智能硬件

+關注

關注

205文章

2383瀏覽量

109082

原文標題:FPGA重要設計思想

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

速度面積互換設計原則簡析

FPGA設計思想與技巧之串并轉換和流水線操作

【設計技巧】FPGA設計思想與技巧匯總

大神常用的四種FPGA/CPLD設計思想與技巧

學FPGA必備,FPGA設計的8大重要知識點。

FPGA設計的十五條原則詳細解析

FPGA的指導性原則詳細資料說明

FPGA設計思想,速度和面積互換原則不可忽視

FPGA設計思想,速度和面積互換原則不可忽視

評論