這期文章,作者君想從模擬電路的角度,給大家講講一個對于模擬工程師來說,既熟悉又有點陌生的內(nèi)容:ESD Electrostatic discharge, 也就是所謂的“靜電保護”。

Wikipedia里面是這樣定義的:Electrostatic discharge (ESD) is the sudden flow of electricity between two electrically charged objects caused by contact。翻譯過來呢,就是指兩個儲存有電荷的物體相互接觸時候產(chǎn)生的瞬時電流。

最近作者君做的項目呢,對于ESD的要求比較嚴(yán)格,就經(jīng)常和一個ESD部門的哥們討論學(xué)習(xí)一下。他告訴我說,ESD可以在任何地方發(fā)生,無論是制造,生產(chǎn),裝配,測試,甚至運輸及現(xiàn)場應(yīng)用。當(dāng)時我就有一種想放棄治療的想法。。。。

那么,問題來了,我們怎么在電路中對其進行模擬并仿真呢?一般我們熟悉并且在電路仿真里面需要用到的模型有兩種:CDM和HBM.

CDM就是所謂的Charge Device Model,HBM就是所謂的Human Body Model。

兩者對比可以看出,一般來說CDM的電流比HBM的電流大一些、也快一些,因為并無較大的電阻在放電通路上面限制放電的過程。

因此,在ESD的仿真中,需要在supply上添加這樣一個pulse電壓。例如在某個工藝情況里:CDM情況下,supply上面需要加入一個高達15V的pulse,上升沿和下降沿都是200ps,持續(xù)4ns。而在HBM的情況下,這個pulse的peak電壓僅僅只是6V,上升沿和下降沿是2ns,持續(xù)時間400ns。

這里插入一句那個哥們的話:“我們就是計算這種 secondary 的ESD的相關(guān)數(shù)值給你們用的啦。”說罷,事了拂衣去,深藏身與名。。。(說白了就是不告訴你怎么算,氣死你……)

等等,為什么上來就說到了secondary ESD protection呢?既然有secondary ESDprotection,那primary ESD protection在哪里呢?

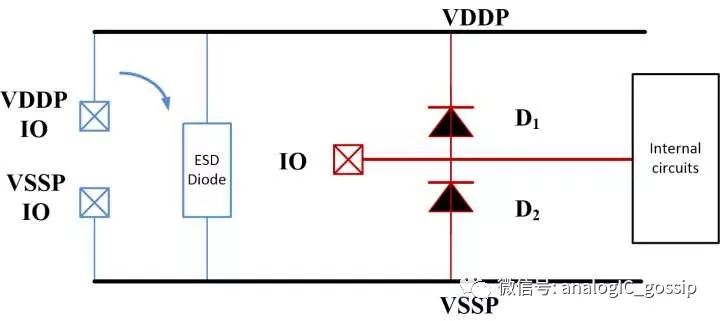

我們熟悉的IO結(jié)構(gòu),那種上下各有一個diode的pad,就是primary esd protection:

通用型的帶ESD保護的IO

比如HBM模型里面,IO被加上一個+2000V的高壓,則上面的diode D1就自然導(dǎo)通了,外界的高壓順著VDDP被迅速導(dǎo)走。同理,若是加上一個-2000V的高壓,D2就導(dǎo)通了,大電流從VSSP快速流向IO,也未傷及內(nèi)部的電路。

在這里,作者君想問大家一個問題:VDDP和VSSP都是給IO的diode們提供偏置的supply。那么VDDP和VSSP的IO 又當(dāng)是怎么樣的呢?還能上下各放一個diode嗎?

快速思考一秒后……

肯定不能是這樣的嘛!感覺就是不能這樣……

那沒有了上下兩個diode,要如何保護VDDP和VSSP的IO呢?

嘿嘿,不如去看看VDDP和VSSP的IO電路好了!

包括了IO的ESD protection的pad模型

因此,此處應(yīng)當(dāng)有另外的ESD保護電路在VDDP的IO和VSSP的IO之間。比如VDDP被加上+2000V的高壓時,通過這個ESD diode快速導(dǎo)走高壓電流。而當(dāng)VDDP是0,而VSSP被加上+2000V的高壓時,這個……

等等,容在下先想想,這里有兩個方向相反的diode嗎?

……

一秒后。

如果VSSP被加上了+2000V,那么豈不是所有的IO都挺熱鬧了?

為什么這么說?

嘿嘿,所有的nwell都是被VDDP給biased成為0V,而substrate因為VSSP變成了2000V,那么,豈不是所有的nwell和sub之間的寄生diode都被打開了?

哇!想想看,聽起來好歡樂的場景啊!

然后,作者君聽說,還有一個所謂的“1 Ohm”原則,據(jù)說是從IO到那些esd diode之間的導(dǎo)通電阻必須要小于1 Ohm,以免寄生電阻太大,影響了快速放電的效果,避免有些“漏網(wǎng)之魚”流到內(nèi)部電路里面去了。所以大家若是仔細看看IO的版圖,會發(fā)現(xiàn)那里metal真是密密麻麻的,“無所不用其極”。

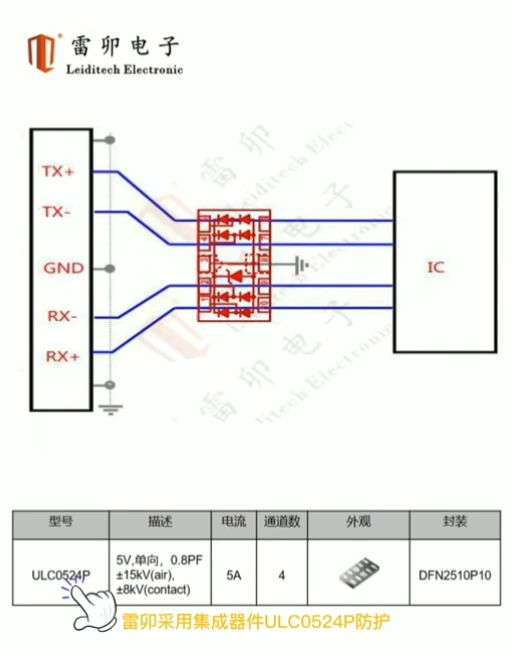

最后,再多說一個小的電路(懶得畫圖,所以拿來借用一下):

這也是一個ESD的保護電路。為什么要說這個呢?因為作者君昨天剛剛被要求在自己內(nèi)部的電路上面加一個nmos的switch,這個nmos的gate就是圖中A點。而且被人告知,這也是secondary ESD protection。(請大家注意,這個fig.1是io的一部分,那個大的nmos Mclamp并不是內(nèi)部電路。這里是在說內(nèi)部電路可以使用io的內(nèi)部節(jié)點進行控制)

我們簡單分析一下:如果VDD上面有高壓pulse的時候,因為電容的電壓滯后作用,電容上面的電壓并沒有跟著VDD迅速提高。因此此時Mp的gate電壓值比source小了不少,導(dǎo)致Mp導(dǎo)通,A點也被連到了VDD上面,巨大size的Mclamp被打開,VDD和VSS通過Mclamp連在了一起。這樣一來,VDD上面的pulse就這樣被巨大的Mclamp給導(dǎo)走了,因此,我們脆弱的內(nèi)部電路也就被保護了起來。

再回到作者君被要求加switch的地方。那個nmos的switch其實類似于一個power down的功能,只是被圖中的A點控制著。當(dāng)出現(xiàn)很嚴(yán)峻的ESD event的時候,內(nèi)部電路能關(guān)斷的趕緊關(guān)斷,千萬不能給ESD的大電流有可乘之機。

最后推薦大家一篇博士論文:http://www-tcad.stanford.edu/tcad/pubs/theses/ShuqingCao.pdftp://http://www-tcad.stanford.edu/tcad/pubs/theses/ShuqingCao.pdf

這篇論文里面還很詳細的講了隨著工藝的縮小,所謂的ESD Design Window是如何越來越小的。因為gate oxide的尺寸越來越小,gate的擊穿電壓也會變小,ESD protection的可以使用的范圍也越來越小。聽起來真是很可憐!

據(jù)作者君的比較,0.18um的IO和28nm的IO大小并無很大區(qū)別(甚至28nm的似乎看起來更大一些)。花了那么多力氣減小工藝尺寸,即使內(nèi)部電路變小,卻被IO的面積給瓶頸了。這真是個悲傷的故事啊!

最后多說一句:ESD經(jīng)常跟leakage之間需要tradeoff。esd diode太大,protection變好,leakage卻會變得比較惡劣,影響正常工作時的性能。需要使用的時候權(quán)衡利弊。

-

ESD

+關(guān)注

關(guān)注

50文章

2269瀏覽量

175298 -

CDM

+關(guān)注

關(guān)注

0文章

30瀏覽量

12403 -

HBM

+關(guān)注

關(guān)注

1文章

409瀏覽量

15138

原文標(biāo)題:集成電路基礎(chǔ):ESD雜談

文章出處:【微信號:analogIC_gossip,微信公眾號:通向模擬集成電路設(shè)計師之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

快速觸發(fā)的靜電保護電路及方法

mosfet有內(nèi)部靜電保護嗎?

ESD靜電保護器的選型及應(yīng)用

ESD靜電保護器件的特點

選擇ESD靜電保護元件的參考因素

HDMI接口靜電保護解決方案

一種常見的ESD靜電保護器件

物聯(lián)網(wǎng)中常見的靜電保護電路設(shè)計方案_ESD靜電保護管

從模擬電路的角度談?wù)勳o電保護

從模擬電路的角度談?wù)勳o電保護

評論