在現代電子系統中,數字電路扮演著至關重要的角色。這些電路處理的是二進制信號,即由邏輯“1”和邏輯“0”組成的信號。這些邏輯狀態通常通過電壓水平來表示,其中高電平代表邏輯“1”,低電平代表邏輯“0”。

1. 數字信號基礎

數字信號是電子系統中用來表示信息的電壓或電流的變化。在最簡單的形式中,數字信號只有兩種狀態:高電平和低電平。這些狀態對應于二進制數字系統中的“1”和“0”。

1.1 高電平輸入

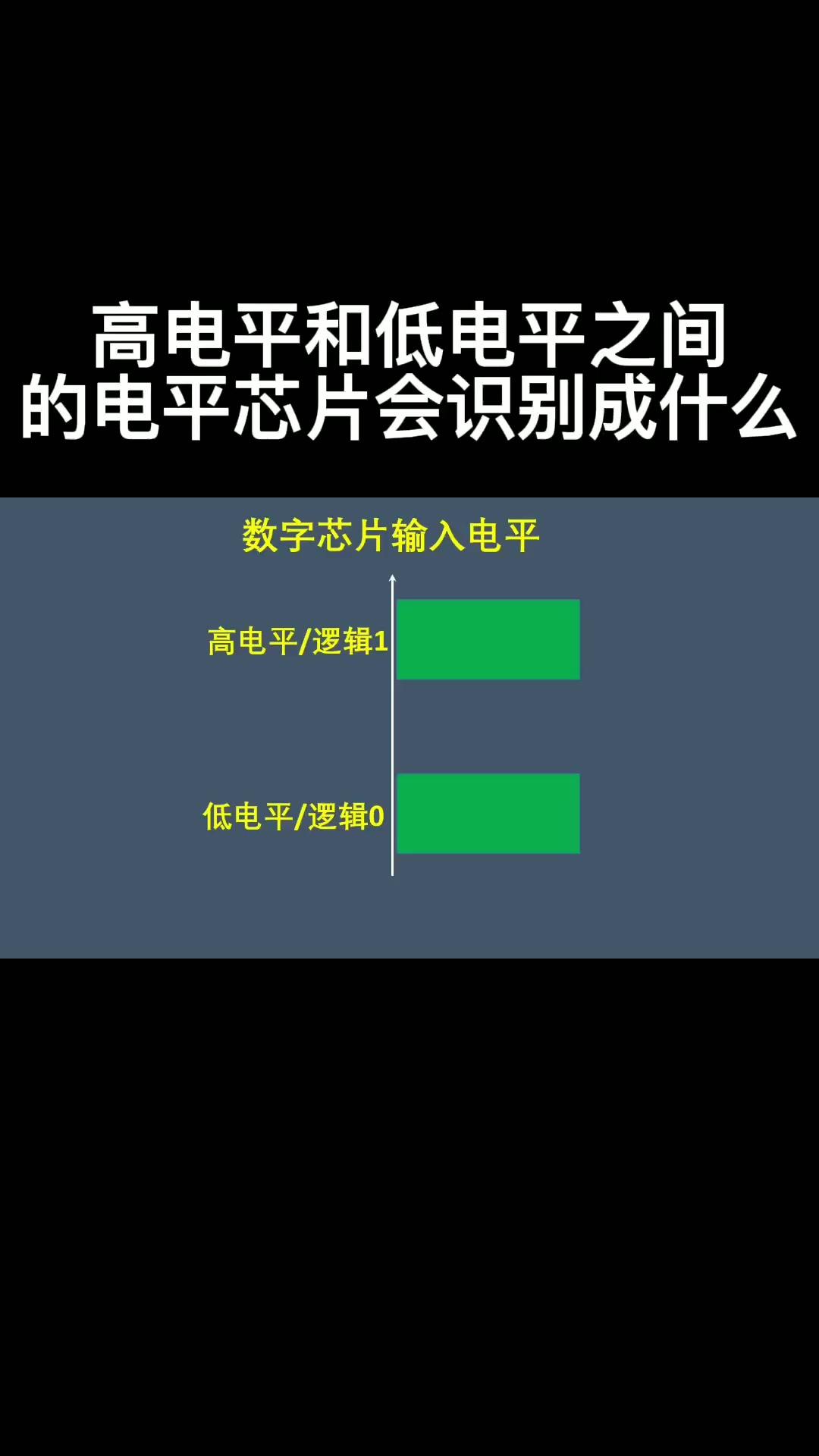

高電平輸入是指電路接收到的電壓水平高于某個預設的閾值。在數字電路中,高電平通常用來表示邏輯“1”。這個閾值電壓通常由電路的設計決定,但常見的標準是5伏特(V)或3.3伏特(V)。

高電平輸入在電路中的作用是激活或使能某些功能。例如,在微控制器中,一個高電平輸入可能意味著一個特定的引腳被設置為輸出高電平,從而驅動一個外部設備。

1.2 低電平輸入

與高電平輸入相對的是低電平輸入,它指的是電路接收到的電壓水平低于預設的閾值。在數字電路中,低電平通常用來表示邏輯“0”。這個閾值電壓同樣由電路的設計決定,但常見的標準是接近0伏特(V)或0.8伏特(V)。

低電平輸入在電路中的作用是關閉或禁用某些功能。例如,在一個簡單的開關電路中,低電平輸入可能意味著電路中的晶體管被關閉,從而切斷電流的流動。

2. 電平觸發和邊沿觸發

數字電路可以根據輸入信號的變化來響應,這通常涉及到電平觸發和邊沿觸發兩種機制。

2.1 電平觸發

電平觸發是指電路對輸入信號的電平變化做出響應。在電平觸發的電路中,只要輸入信號保持在高電平或低電平狀態,輸出就會相應地保持在高電平或低電平狀態。

電平觸發電路的一個常見例子是基本的邏輯門,如與門(AND)和或門(OR)。這些邏輯門的輸出狀態完全取決于輸入信號的電平狀態。

2.2 邊沿觸發

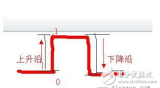

與電平觸發不同,邊沿觸發是指電路對輸入信號的電平變化(即從低電平到高電平或從高電平到低電平的躍變)做出響應。在邊沿觸發的電路中,輸出只在輸入信號的電平發生變化時改變狀態。

邊沿觸發電路的一個典型例子是觸發器,如D觸發器和JK觸發器。這些觸發器的輸出狀態取決于輸入信號的邊沿變化,而不是電平的持續狀態。

3. 噪聲和信號完整性

在實際的電子系統中,信號的完整性可能會受到噪聲的影響。噪聲可以是電源電壓的波動、溫度變化、電磁干擾(EMI)或電路本身的不完美。

3.1 噪聲對信號的影響

噪聲可能會導致信號的電平變化,從而影響電路的邏輯判斷。例如,如果噪聲導致一個本應為低電平的信號短暫地上升到高電平閾值,電路可能會錯誤地將這個信號識別為高電平輸入。

3.2 信號完整性

為了確保信號的完整性,設計者通常會采取一些措施來減少噪聲的影響。這些措施包括使用去耦電容來穩定電源電壓、使用屏蔽和接地技術來減少EMI、以及設計具有足夠噪聲容限的電路。

-

電流

+關注

關注

40文章

7118瀏覽量

134343 -

二進制

+關注

關注

2文章

804瀏覽量

42177 -

低電平

+關注

關注

1文章

175瀏覽量

13615 -

高電平

+關注

關注

6文章

198瀏覽量

21925

發布評論請先 登錄

高電平和低電平是什么意思?區別是什么?

PWM的輸入是高電平有效還是低電平有效的?

低電平和高電平的區別

邏輯芯片輸入的低電平有效和高電平有效

電子設計(4)高電平、低電平復位電路

單片機檢測IO口高電平、低電平、懸空三種狀態。

高電平、低電平復位電路

高電平輸入和低電平輸入是什么意思

高電平輸入和低電平輸入是什么意思

評論