射頻收發機早已融入現代人的生活,每天都有海量的數據通過無線方式傳輸到用戶端。您是否對其架構產生過好奇?射頻發射機是怎么將龐大的數字信息發射到空氣中?射頻接收機又是怎么將接收到的信息進行處理?射頻收發機里面蘊藏什么關鍵性技術?本文將隨著信號流動的方向帶領您領略人類科技的結晶。同時在文章最后,作者將拋磚引玉的分享自己對于射頻收發機發展的一些愚見供大家思考。

1. 射頻收發機的構成

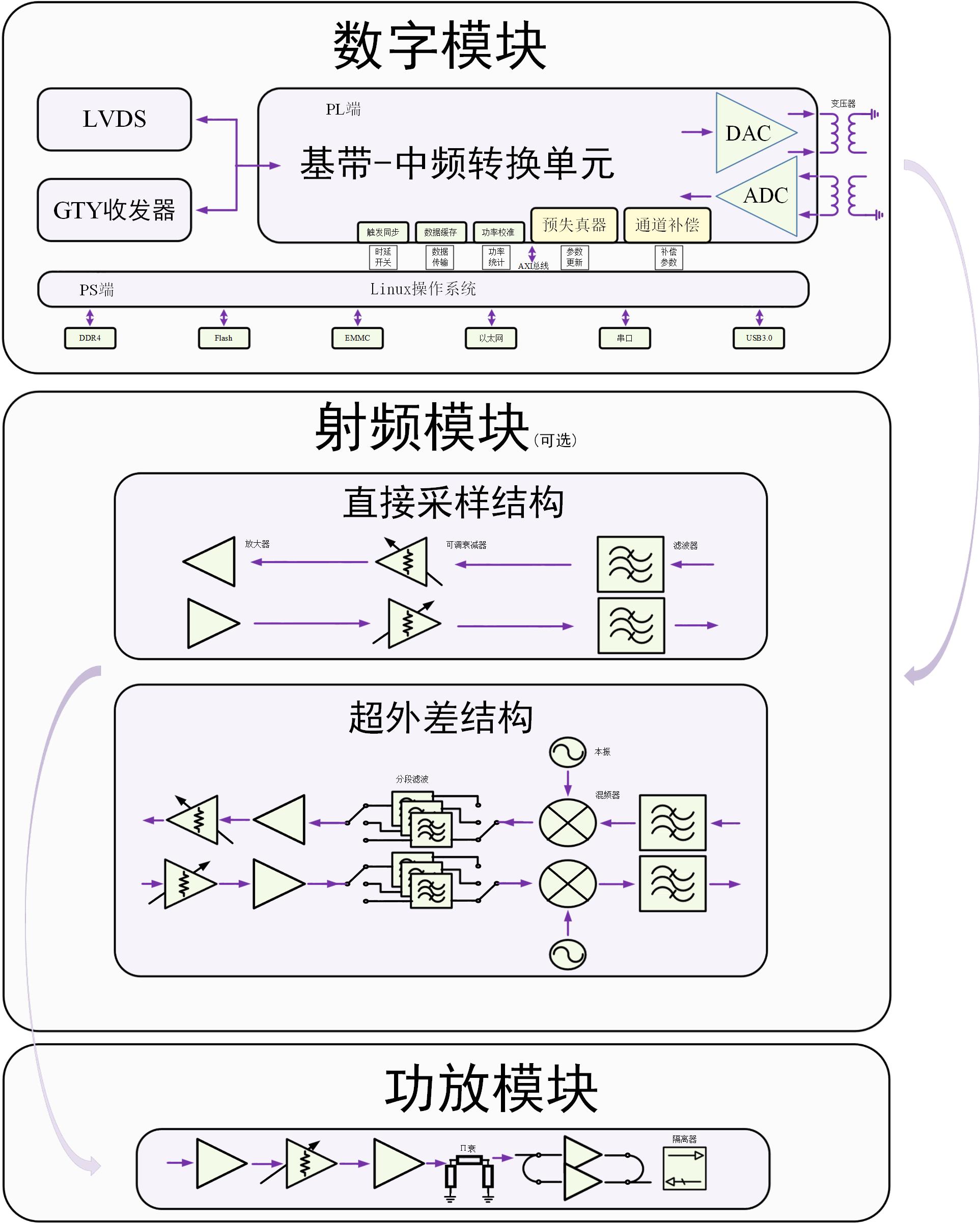

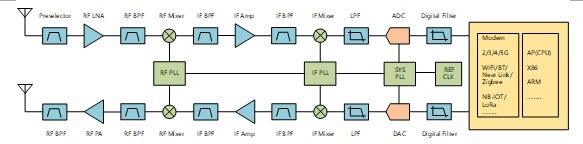

射頻收發機是一個很復雜的系統,包含了數據處理、數模轉換、頻率變換、放大濾波、隔離發射眾多步驟。其主要的目的便是將通信專業同學研究的原本只能存在電子設備中的編碼波形,變成脫韁的電磁波發射出去;并在其他的地方進行接收并提取信息。射頻收發機有源系統部分框圖如下圖所示

這篇文章將從信號的流動開始,講述承載信號的硬件模塊。為了不讓整篇文章顯得冗雜且晦澀難懂,筆者會忽略掉每個模塊的技術細節,在以后的文章中單獨講解。

2. 信號的流動方式

信號如水流,她不會憑空出現,亦不會突然消失,不論她是什么樣的形態都需要一個載體。比如我們發出的聲音需要振動的介質,看的文字需要顯示的介質,數字世界中的信號傳輸需要電路。

信號的本質是攜帶著0或1編碼的水流,但水流的大小卻受限于接納她的入口,入口越大,水流越快,大就是好。然而水能載舟,亦能覆舟,大意味著施工難度大,材料需求高,人員成本高,維護難度大,故在不同需求中采用的方案也有所區別。

信號的流動有兩種方式,一種是緩存式信號流,另一種是實時式信號流。顧名思義,緩存式信號流是將信號先緩存到存儲設備中,如DDR中,再進入信號處理模塊;實時信號流則是直接通過GTY收發器、LVDS等接口實時的將外部信號流導入信號處理模塊。

為什么會出現兩種不同的處理方式呢?對于FPGA本身,內部在不考慮資源消耗的情況下,進行信號流動處理時幾乎沒有速度限制,他就如一片汪洋的大海。然而信號流的傳入接口卻需要和外部進行的連接,這樣的連接好比汪洋大海的入口只有一個水渠,大大限制了水流大小。下表給出了不同連接協議之間信號傳輸的速率

| 序號 | 設備 | 速率 |

| 1 | 串口 | 10Mbps |

| 2 | USB2.0/USB3.0 | 480Mbps/5Gbps |

| 3 | 百兆網/千兆網/萬兆網 | 100Mbps/1Gbps/10Gbps |

| 4 | SFP+/QSFP+/QSFP28光模塊 | 10Gbps/40Gbps/100Gbps |

可以看出,若想要實時傳輸40Gbps及以上的信號時,只能采用QSFP+和QSFP28光模塊;但若想要在未搭載這些接口的硬件設備中,實現更高點數信號的處理,則可以用緩存的方式,以打包的方式來進行傳輸。就好比點點滴滴匯入星辰大海,理論上串口也可以傳輸包含千萬個數據點的信號,當然其缺點也很明顯,需要等待億點點時間。

3. 信號的處理過程

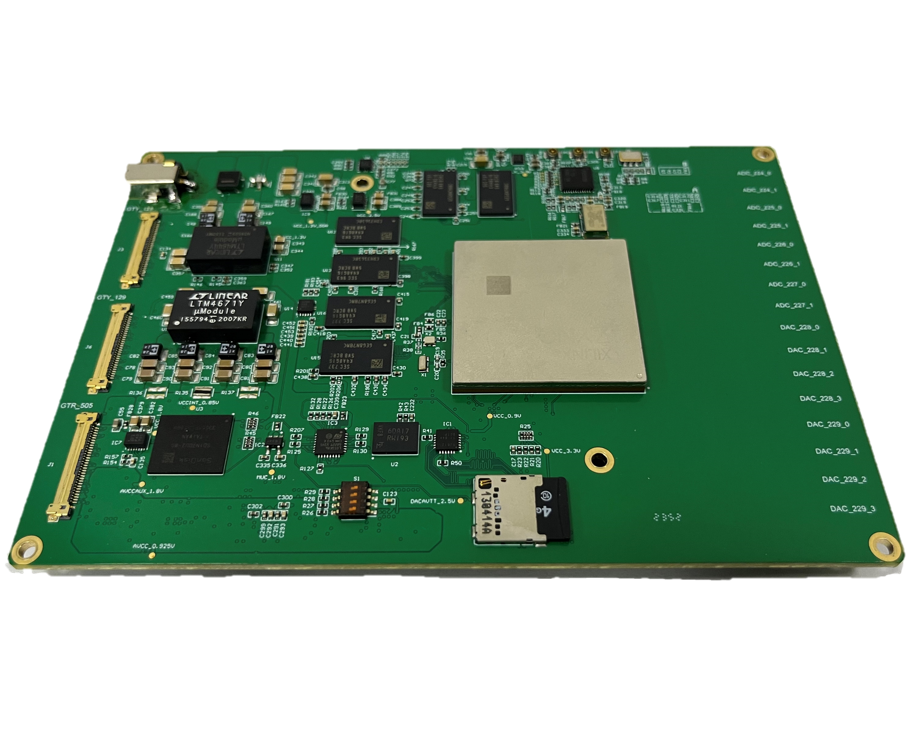

數字模塊中數字部分主要由兩個部分構成,一個是信號實時流動的路徑,另一個則是針對信號流動的參數計算,即FPGA+處理器架構。而處理器架構又分為單片機、ARM、DSP、CPU等等,我們這篇文章不講很細節的區別。因為本質上,數字模塊也都是由一個個邏輯門構成,都和FPGA沒有本質區別,而不同的架構本質上可以理解為根據需求不同,其承載不同開發者的社區文化,所分享的軟件不同而已。目前國際上一種趨勢是將FPGA+處理器同時在同一個芯片中進行實現,如Zynq結構,這樣可以將它們之間的數據互通問題更簡單的解決掉。

信號在主干道上是不停流動的,其數據處理模塊都是并行處理,只能由FPGA來擔任。如觸發同步、功率校準、預失真器、通道補償、諧波抑制等模塊都是需要例化出實際的電路,信號需要在物理上真實的“流”過這些模塊。主干道的模塊中有大大小小的開關,這些開關需要在不同的情況下進行切換,將信號導向不同的路段進行傳輸。

這些開關的控制則需要處理器來實現,而處理器中的指令是逐條實現的,因此速率會相較信號流低很多,其勝在靈活性和統一性。不同算法可以在同樣的架構上進行不同的嘗試,同時有很多現成的協議。處理器運行操作系統,需要一些外設,包括存儲設備Flash、EMMC、SD卡,主要將系統和應用文件放在里面,多種存儲設備共存可以互為備份提高整個系統的穩定性;內存設備DDR,開機后的系統文件緩存在其中運行,提高系統穩定性和運行速率;指令傳輸設備串口/JTAG,可方便開發者進行指令傳輸和調試;數據傳輸設備以太網/USB,進行大數據量的交互。

數字模塊中數模轉換部分主要是DAC和ADC。為什么要進行數模轉換呢?這是因為我們需要建立電路到世界的橋梁,電路是人為制造的產物,0和1無法在茫茫空間中傳播。除非將人造線纜連接到世界的各個角落,終端,空間站,信號才能進行傳輸。想要在廣袤的空間乃至星海中進行傳播,那就必須回歸世界本身的規則,產生模擬信號進行傳輸。事實上,在人類出現前,空間就彌漫著各種電磁波,人類從來都沒有發明電磁波,只是發現并利用了它。

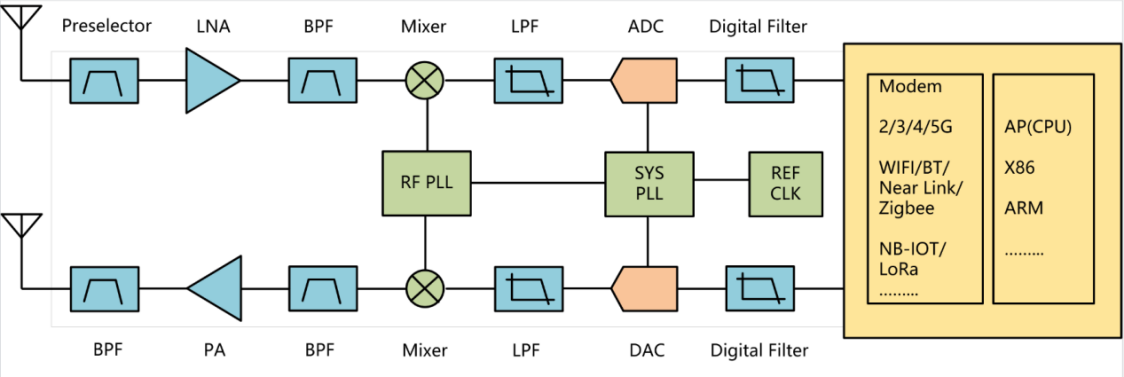

射頻模塊根據結構主要分為直接采樣結構和變頻結構。直接采樣即不通過變頻方式直接處理射頻信號,該結構主要是對于技術和工藝的突破,使得DAC和ADC的采樣率能超過實際射頻頻率。如賽靈思的RFSoC ZU47DR芯片中便集成了數字模塊和采樣率5.0 GSPS的ADC和9.85GSPS的DAC,使得直接發射一個射頻頻率3.5 GHz,帶寬1.2 GHz的寬帶信號也綽綽有余。變頻結構,不管是零中頻架構還是超外差架構,本質都是一種成本和技術上的妥協。如果說直接采樣結構是硬骨頭扛鼎,那么變頻結構則是四兩撥千斤。混頻器作為杠桿,本振作為支點,將原本低頻的信號通過該杠桿變為高頻信號方便傳播。

功放模塊功能則更加簡單,信號在空間中傳播是存在衰減的,介質會不停的汲取傳播過程中的能量。如何將信號傳播的更遠,那需要將功率增加,一級不夠就兩級,兩級不夠就三級,直到功率夠格為止,最終放大后的信號便可通過天線發送到空氣中進行傳播,等待遠方同胞進行接收。

4. 射頻收發機的關鍵性技術

前面梳理了射頻收發機的構成和運行原理,本節希望對射頻收發機中的一些筆者認為的關鍵技術進行分享。我們目前的研究水平如何?和國際水平存在差異嗎?差異要怎么進行彌補?

基礎層級下,是射頻收發機中各個關鍵性芯片的突破。從處理高速數據流的FPGA芯片,到高分辨率高采樣率的AD/DA;從低相噪低雜散的寬帶鎖相環,到高頻寬帶的混頻器芯片;從高線性的GaAs射頻芯片,到高功率的GaN芯片等等都是需要進行突破的,但這個層面對于普通設計者來說太過遙遠。筆者愚見,除了芯片本身的突破之外,目前核心在于觀念的突破,系統化的思維的培養。

射頻收發機的模塊看似不多,但實際上涉及到了許多學科之間的壁壘,每一科進行深入研究都能支撐大大小小獨立企業的發展。就如木桶效應中所述的,一個系統的整體效能不是由其最強部分決定,而是最弱部分決定的。筆者主要是研究大功率大帶寬矢量收發器這一方向,在這方面,國際頂尖儀器供應商基本都是國外廠商,如羅德與施瓦茨,是德科技,恩艾科技等等。這幾年國內儀器廠商如雨后春筍冒出,但在金字塔尖的高端儀器領域還有不少的路需要走。

筆者愚見,其中一個問題在于國內的研究聚焦于獨立的專業領域。設計數字模塊的僅關注數字編碼、采樣率、中頻頻率、DA/AD;設計變頻模塊的僅關注頻段、雜散、相噪、動態;設計功放模塊的僅關注增益、功率、線性度;設計射頻算法的人才更是寥寥無幾,大部分也僅關注IQ不平衡、校準等。雖然也有研究系統的團隊,但對于系統間關鍵性技術還需要進一步探索。最后會陷入一個怪圈,將各個模塊進行極致性能打磨后,卻最終實現了一個相對平庸的性能。

個人覺得,真正的系統設計理念不應該是這樣的。其一,這個世界是公平的,而高端射頻收發機中幾乎所有指標都是相互制衡的,無法同時達到最佳,無法既要又要;其二,不能讓各個模塊僅各司其職,而是相互扶持,真正實現數字增強射頻,射頻創造系統的理念。這里闡述一些筆者認為的關鍵性技術,相對成熟的方法便不再本文討論,本文主要是我們射頻系統專欄的一個架構性總覽文章。工程實現、技術細節、前沿研究等將在以后文章獨立分享,敬請期待。

從數字模塊開始,FPGA和Linux操作系統可以實現射頻算法,其中可形成通道補償、數字預失真、諧波抑制等IP。通道補償針對所有射頻電路進行補償,一般采用帶記憶項的濾波器組進行補償,在不同的條件下需要更新補償條件。數字預失真針對系統非線性進行補償,諧波抑制針對系統諧波特性進行改善。數字改善確定性,射頻改善隨機性。比如增益/相位波動、部分雜散、功放基波/諧波非線性特性等屬于確定性特性,發揮數字端高精度的特點可事半功倍;而射頻則需要解決隨機性和提高可改善性,隨機性如噪聲系數、相噪、部分雜散等。提高可改善性便需要進行比較深入的研究了,需要探索數字電路和射頻電路的磨合極限與其平衡點。

射頻模塊也有很多新的研究點,細心的朋友已經發現我這里使用的是射頻模塊而不是變頻模塊。因為變頻并不是必須的,DA/AD性能如此強大的如今,混合結構是未來發展的前景,針對不同射頻頻率采用不同的架構。通過數字模塊強大的精確度引入本振對消、雜散對消、時鐘對消等技術;通過切換采樣率更換中頻使得變頻結構從二次變頻簡化為一次變頻、一次變頻簡化為直接采樣。在實現相同功能的情況下,越簡約的架構,性能和穩定性越高,但簡約不意味著簡單,相反這需要整個系統的協同配合。

功放模塊同樣也有很多研究點,功放的前沿研究一直圍繞著更寬的帶寬、更高的效率進行。功放作為射頻收發機系統的功耗大戶,除了運營成本之外,更重要的是低能效意味著高熱量和低穩定度。晶體管的壽命是受溫度影響的,過高的熱量會損壞器件,通常一個手指粗細的晶體管消耗的熱量需要數十倍于其體積的鋁塊加上風冷/水冷才能保持系統正常運行。采用電源調制、負載調制等結構均是為了提高其效率,但其又會帶來非線性惡化等新的問題,這時數字模塊中嵌入射頻算法進行聯合設計是解決這些問題的辦法。

5. 小結

本文針對射頻收發機架構進行了簡單的分享。同時筆者認為,數字模塊、射頻模塊、功放模塊需要聯合設計構成一個整體才能發揮其實力,真正做到“聚是一團火,散是滿天星”。

www.amplustech.com

審核編輯 黃宇

-

FPGA

+關注

關注

1641文章

21912瀏覽量

611731 -

移動通信

+關注

關注

10文章

2667瀏覽量

70609 -

數字模塊

+關注

關注

0文章

5瀏覽量

6317 -

射頻收發機

+關注

關注

0文章

28瀏覽量

5994

發布評論請先 登錄

相關推薦

射頻收發器與基帶的區別

AN149 GD32VW553射頻性能和收發器功耗測試指南

AN149 GD32VW553射頻指標及收發功耗測試指南

射頻收發機發展史

射頻收發器屬于什么類別

射頻收發器是混合集成電路嗎

射頻收發信機的主要結構有哪幾種,各有什么優缺點

一文簡單介紹射頻識別RFID

一文淺談射頻收發機

一文淺談射頻收發機

評論