什么是reg_model鏡像值?

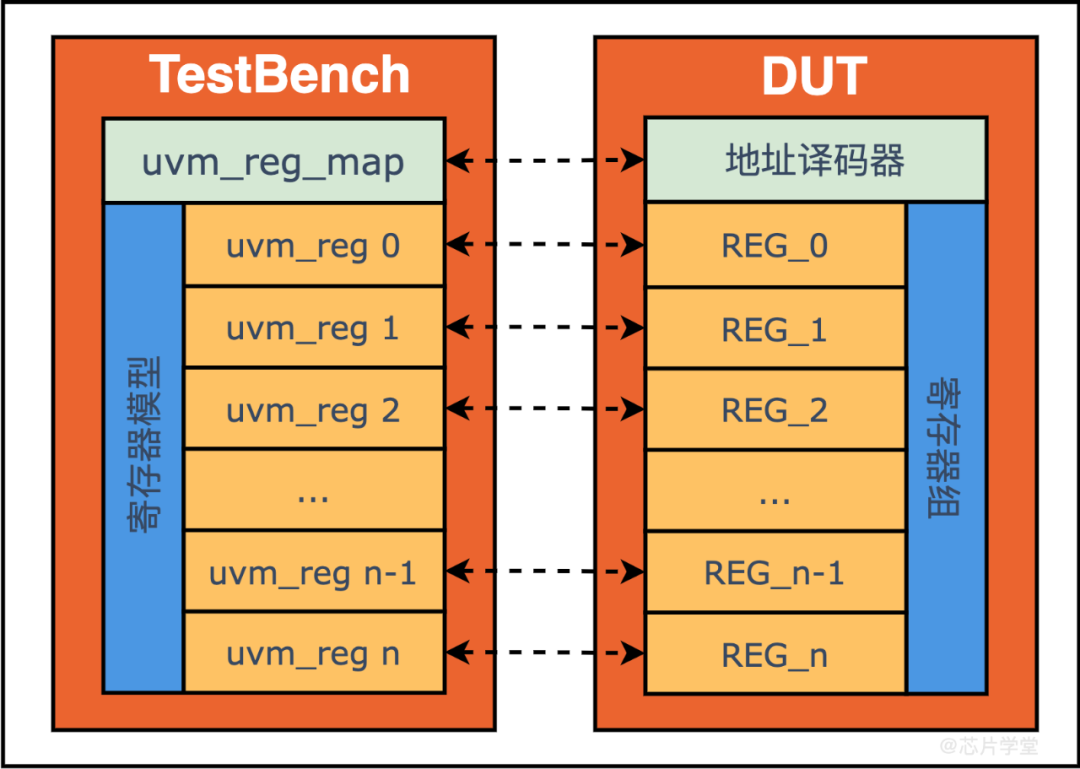

DUT的配置寄存器的值是實(shí)際值,reg_model有鏡像值、期望值的概念。

鏡像值:存放我們認(rèn)為此時(shí)DUT里寄存器的實(shí)際值。

期望值:存放我們期望DUT寄存器被賦予的值。

什么是auto predict?

那么怎么更新reg_model里面的鏡像值呢?有三種方式更新reg_model里面的鏡像值。

方式1:reg_model調(diào)用自己的auto predict

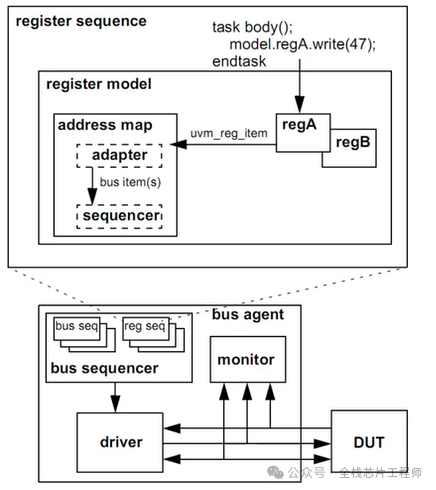

舉個(gè)例子,如下圖,model.regA.write(47),通過regA找到對(duì)應(yīng)的uvm_reg_item,然后找到address_map里面對(duì)應(yīng)的地址,用adapter完成轉(zhuǎn)換得到bus_item并給到sequencer。然后通過driver的讀寫完成reg_model寄存器的鏡像值刷新。

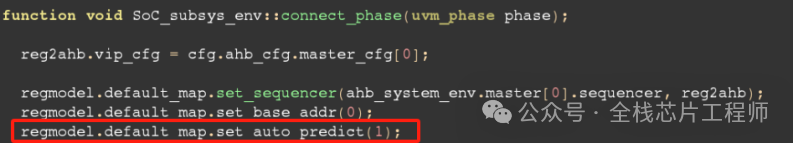

在寄存器模型創(chuàng)建的組件的connect_phase()調(diào)用寄存器模型中的uvm_reg_map的set_auto_predict(on)來選擇打開(on=1)或關(guān)閉(on=0)自動(dòng)預(yù)測(cè)功能,默認(rèn)關(guān)閉。

景芯SoC驗(yàn)證項(xiàng)目采用的就是auto_predict,如下圖,在SoC_subsys_env.sv里面connect_phase階段寫一句regmodel.default_map.set_auto_predict(1)即可。默認(rèn)是關(guān)閉的。

自動(dòng)預(yù)測(cè)打開的優(yōu)點(diǎn)在于我們UVM環(huán)境實(shí)現(xiàn)起來會(huì)比較簡單,工作量大大降低,缺點(diǎn)是無法predict寄存器模型之外的總線行為(例如sequence),因而不能保證寄存器模型與DUT的實(shí)時(shí)匹配。

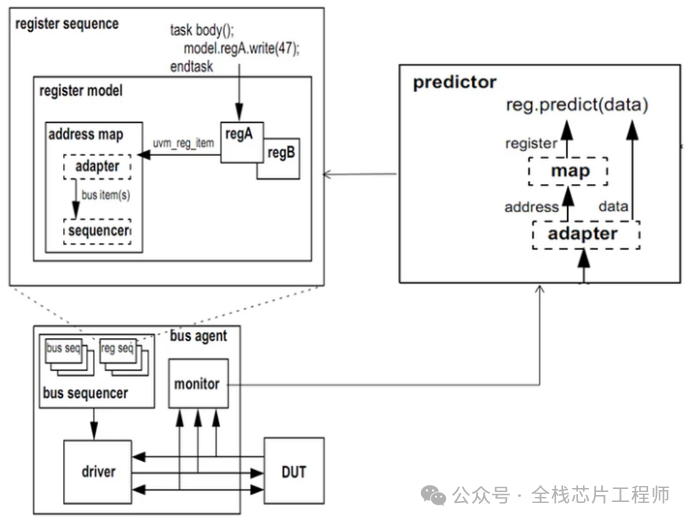

方式2:關(guān)閉自動(dòng)預(yù)測(cè)功能并實(shí)例化uvm_reg_predictor

如果關(guān)閉自動(dòng)預(yù)測(cè)功能,那么我們需要將uvm_reg_predictor實(shí)例化(或者繼承一個(gè)我們自己的predictor),將predictor實(shí)例與我們monitor相連接(這里還需要我們monitor能夠正確抓去總線數(shù)據(jù)),這樣predictor就會(huì)實(shí)時(shí)的獲取monitor所監(jiān)測(cè)到的transaction信息,通過transaction中提供的address信息與uvm_reg_map中的寄存器address進(jìn)行匹配進(jìn)而發(fā)起相應(yīng)的uvm_reg的predict()行為。

這樣一來uvm_reg的predict行為就跟寄存器模型中的讀寫行為脫鉤了,只是跟monitor上的行為想關(guān)聯(lián),即使不是寄存器模型發(fā)起的讀寫(例如通過一般的sequence發(fā)起的總線讀寫),也是可以實(shí)時(shí)的更新寄存器模型中的鏡像值和期望值,這樣做更能保證寄存器模型中的值與DUT中的寄存器值最大程度的保持一致。

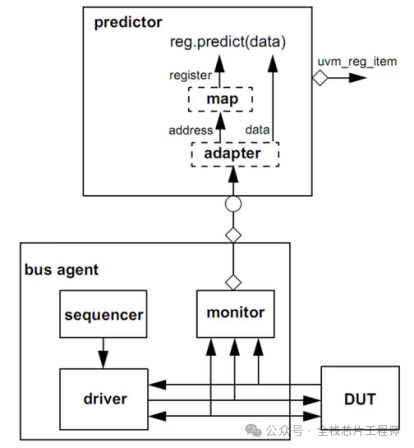

方式3:reg_model被動(dòng)實(shí)例化uvm_reg_predictor

reg_model不做寄存器配置,僅作為被動(dòng)檢測(cè),由bus agent的monitor來獲取DUT的寄存器配置值,經(jīng)過adapter轉(zhuǎn)為為address和data,address從map關(guān)系中找到對(duì)應(yīng)的register,然后把data通過uvm_reg_item返回給reg_model。

我們需要在寄存器模型創(chuàng)建的組件的connect_phase()調(diào)用寄存器模型中的uvm_reg_map的set_auto_predict(on)來選擇打開(on=1)或關(guān)閉(on=0)自動(dòng)預(yù)測(cè)功能,默認(rèn)關(guān)閉。

自動(dòng)預(yù)測(cè)打開的優(yōu)點(diǎn)在于我們UVM環(huán)境實(shí)現(xiàn)起來會(huì)比較簡單,工作量大大降低,缺點(diǎn)是無法predict寄存器模型之外的總線行為(例如sequence),因而不能保證寄存器模型與DUT的實(shí)時(shí)匹配。

關(guān)閉自動(dòng)預(yù)測(cè)我們就需要實(shí)例化uvm_reg_predictor,并將uvm_reg_predictor實(shí)例中的bus_in與我們的uvm_monitor中的uvm_analysis_port相連接,這就需要我們保證uvm_monitor實(shí)現(xiàn)必須完善,這樣就可以保證我們寄存器模型與DUT中的寄存器值最大可能的保持一致性。

-

寄存器

+關(guān)注

關(guān)注

31文章

5427瀏覽量

123716 -

soc

+關(guān)注

關(guān)注

38文章

4358瀏覽量

221993 -

模型

+關(guān)注

關(guān)注

1文章

3500瀏覽量

50128 -

DUT

+關(guān)注

關(guān)注

0文章

190瀏覽量

12876

原文標(biāo)題:詳解寄存器模型reg_model的auto_predict

文章出處:【微信號(hào):全棧芯片工程師,微信公眾號(hào):全棧芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

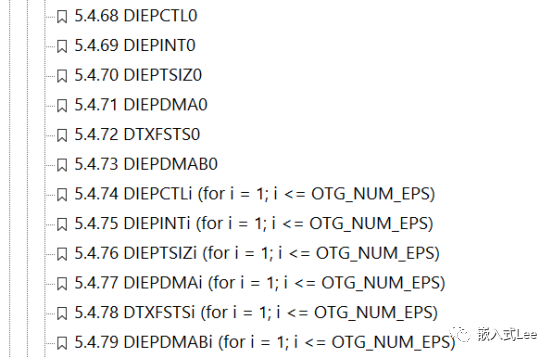

基于DWC2的USB驅(qū)動(dòng)開發(fā)-發(fā)送相關(guān)的寄存器DMA寄存器詳解

ARM寄存器詳解

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

寄存器操作方法_對(duì)寄存器操作的通用方法總結(jié)

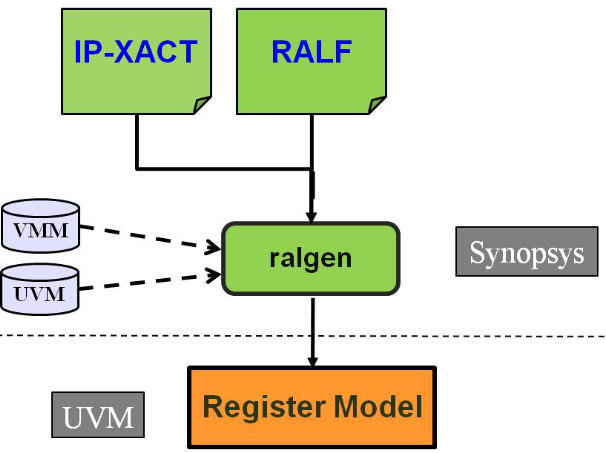

簡述RAL寄存器模型基礎(chǔ)

簡化UVM寄存器模型的使用

詳解寄存器模型鏡像值

詳解寄存器模型鏡像值

評(píng)論