文章來源:學習那些事??????

原文作者:小陳婆婆???

在半導體制造流程中,晶圓測試是確保產品質量和性能的關鍵環節。與此同時封裝過程中的缺陷對半導體器件的性能和可靠性具有重要影響,本文就上述兩個方面進行介紹。

晶圓測試

對于碳化硅(SiC)材料而言,由于其獨特的物理和化學性質,測試過程尤為重要。以下是以碳化硅晶圓為例,對其電學測試系統的詳細解析。

測試系統概述?

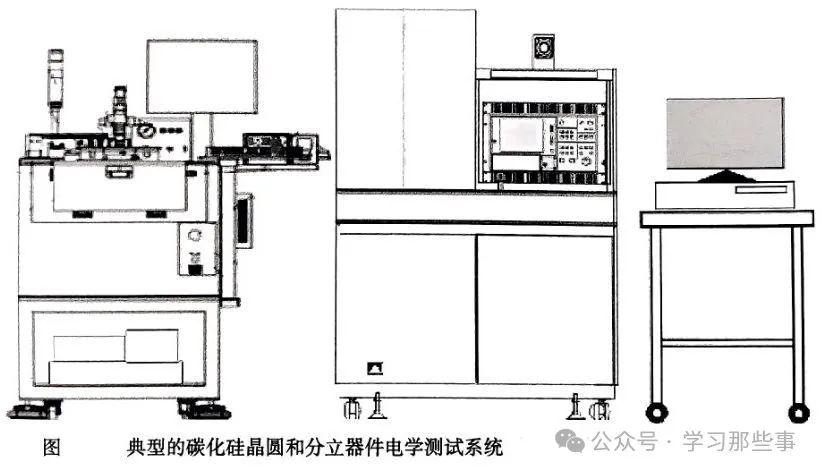

如上圖所示,一個典型的碳化硅晶圓和分立器件電學測試系統主要由三部分組成:電學檢測探針臺、晶體管檢測儀以及控制用計算機。這三部分協同工作,共同構成了完整的測試系統。

探針臺解析

探針臺如圖所示,是測試系統的核心部件之一,主要負責晶圓的電學檢測。它主要由載物臺、探卡、絕緣氣體供應設備等組成。

載物臺:用于放置晶圓,可以兼容4~8寸的晶圓。載物臺上設有真空氣孔,能夠牢固地吸附住晶圓,防止在測試過程中晶圓發生移位。

探卡:通過探針與晶圓上的電極接觸,實現電信號的傳輸和檢測。

絕緣氣體供應設備:提供壓縮空氣和N?等絕緣氣體,用于防止在測試高壓過程中發生“打火”現象。此外,還可以將晶圓浸泡在氟油中進行測試,以提高測試的絕緣效果和準確性。氟油測試法不僅測試效果優于壓縮空氣絕緣,而且測試完成后氟油容易揮發,不會污染晶圓表面。

曲線追蹤儀功能

曲線追蹤儀,如圖所示是測試系統的另一個重要部件,主要用來輸出高電壓和大電流,并通過連線傳導到探針上。

電源配置:儀器內部含有集電極電源和步進式信號源兩組電源,可通過線路配置將電壓加到集電極、發射極和基極上,以滿足不同的測試需求。

測試電路:設備中包含7種固定的測試電路,可用于完成不同的測試項,如正向電壓測試、反向漏電流測試等。

測試實例分析

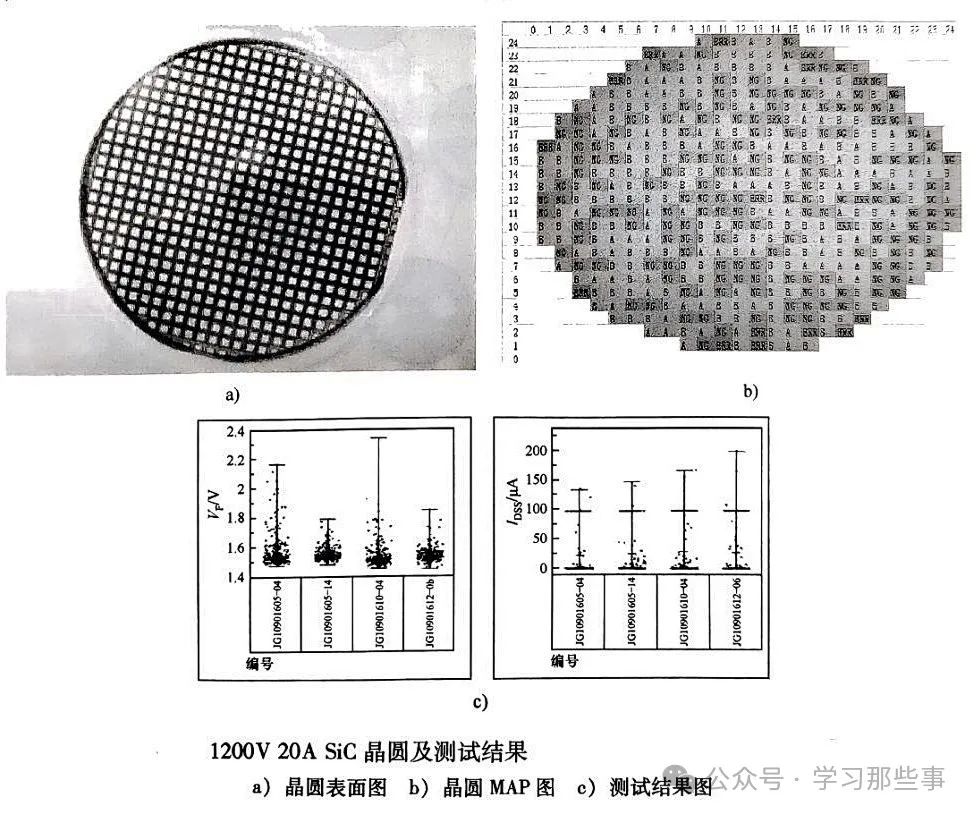

晶圓結構:如圖a所示,1200V 20A SiC SBD晶圓正面為陽極,背面為陰極。

測試過程:探針臺內的步進式電機帶動載物臺對晶圓進行點測。通過步進式掃描,可以得到晶圓上每個測試點的電學性能數據。

測試結果:如圖b所示,通過等級MAP圖可以直觀地看到晶圓上各測試點的性能分類(A、B、NG、ERR)。對5塊晶圓的測試結果進行匯總(如圖c所示),可以看出VF基本都在1.5~1.6V之間,反向IDSS漏電流大部分都在10μA以下。這表明晶圓正向分布的一致性良好,但反向特性仍有進一步提升的空間。

綜上所述,硅晶圓電學測試系統是一個復雜而精細的系統,通過合理的配置和精確的測試,可以確保晶圓的質量和性能符合設計要求。

封裝過程缺陷解析

封裝過程是半導體器件制造中的關鍵環節,其質量直接影響器件的性能和可靠性。以下是封裝過程中常見的缺陷及其詳細解析:

裝片空洞

定義:裝片空洞是指在封裝過程中,由于密封不良、裝片機參數設置不當或芯片表面存在異物(如氧化物)等原因,導致芯片與框架基島之間未能形成良好的黏結或釬接,從而產生空洞。

影響:空洞的存在會嚴重影響功率器件的導電性,導致RDS(ON)值超標,進而影響器件的性能。此外,空洞還會降低芯片的導熱效率,形成熱量聚集點,增加器件在溫度和功率循環過程中的受力不均勻性,從而引發焊料層裂紋,進一步影響封裝產品的可靠性。

控制標準:一般功率芯片對空洞的大小和總面積有嚴格規定,非車規級產品中要求總面積不超過芯片面積的10%,單個空洞不超過5%。

鍵合不良

定義:鍵合不良包括引線短路、彈坑損傷、第二焊點虛焊或鍵合強度弱等問題。

影響:引線短路會導致不同極性的焊線之間發生擊穿,造成功率器件失效。彈坑損傷和虛焊會降低鍵合強度,使得器件在受到交變應力時容易發生接觸不良,進而影響器件的可靠性和使用壽命。

預防措施:在封裝體設計時,應確保不同極性的焊線之間的距離足夠大,以避免擊穿短路。同時,應嚴格控制封裝過程中的工藝參數,以減少對芯片的機械沖擊,并確保焊料厚度和冷卻速率合適,以減少熱應力沖擊。

封裝破裂

定義:封裝破裂是指在封裝過程中,由于機械沖擊、熱應力等因素導致的芯片內部或表面出現裂紋。

影響:封裝破裂可能導致器件的瞬間電氣失效,尤其是當裂紋生長到影響電路連接時。裂紋還會降低器件的可靠性,因為裂紋的擴展需要時間,所以即使初始時能通過功能檢測,也可能在后續的使用環境中出現問題。

預防措施:應嚴格控制封裝過程中的工藝參數,以減少對芯片的機械沖擊。同時,應確保有足夠的焊料厚度來阻止裂紋的擴展,并選擇合適的冷卻速率來減少熱應力沖擊。此外,還應嚴格控制劃片過程中的崩角大小,以防止裂紋的產生。

綜上所述,在封裝過程中應嚴格控制各項工藝參數和條件,以確保封裝質量符合設計要求。同時,還應加強質量檢測和控制手段,及時發現并處理潛在的缺陷問題。

-

半導體

+關注

關注

335文章

28696瀏覽量

234079 -

晶圓

+關注

關注

52文章

5130瀏覽量

129281 -

碳化硅

+關注

關注

25文章

3043瀏覽量

50163

原文標題:晶圓測試與缺陷解析

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

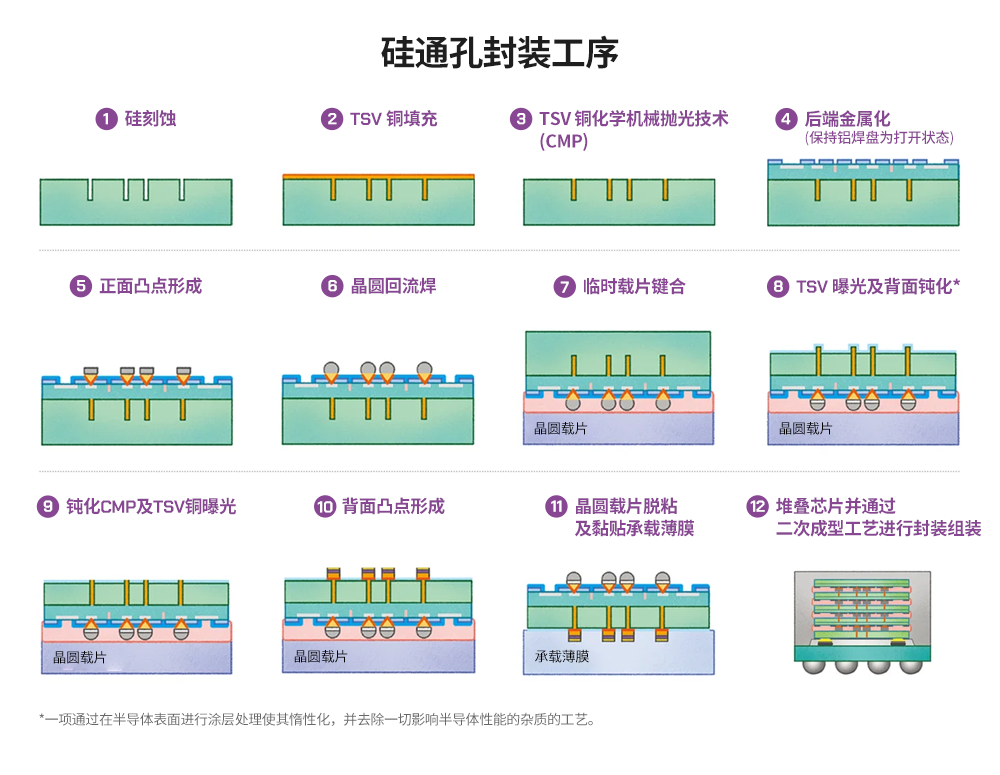

晶圓級多層堆疊技術及其封裝過程

什么是晶圓級封裝?

LED封裝過程中的存在缺陷檢測方法介紹

晶圓封裝過程缺陷解析

晶圓封裝過程缺陷解析

評論