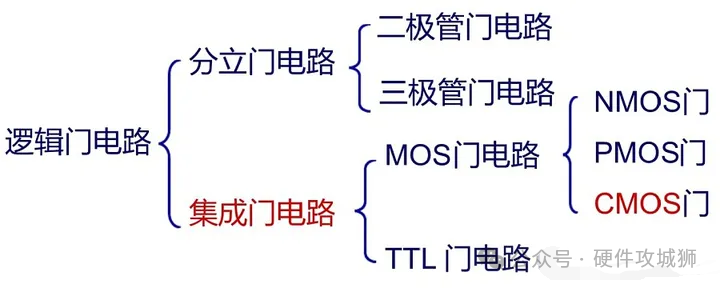

邏輯門電路的類別

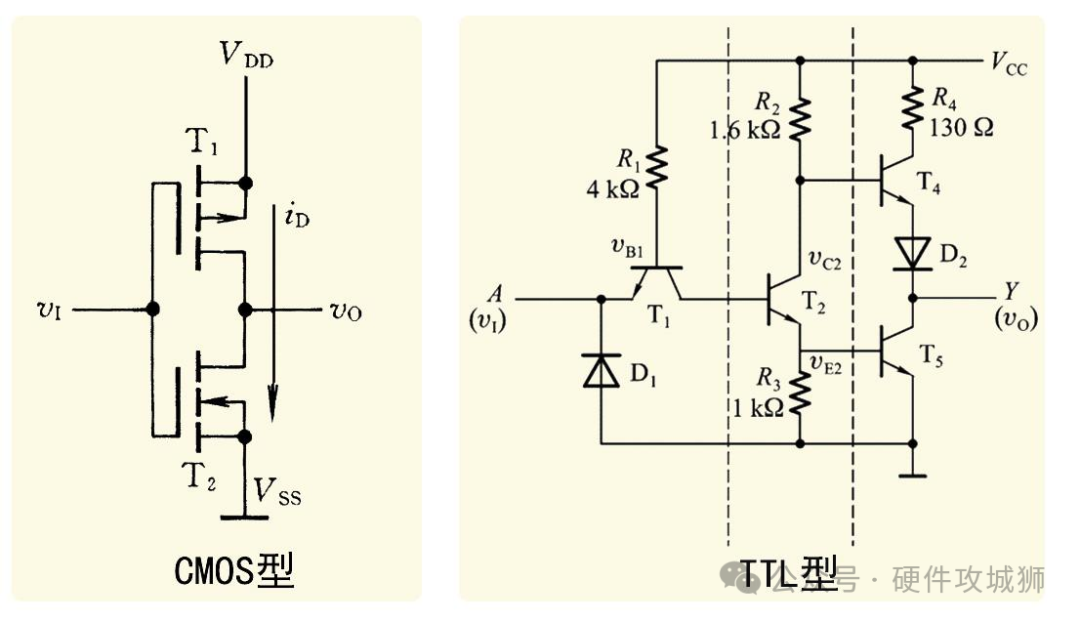

除了分立元件邏輯門(二極管和晶體管),對于集成電路邏輯門大致可以分為兩類:

絕緣柵場效應管CMOS集成邏輯門、雙極型晶體管TTL集成邏輯門

CMOS與TTL比較:

②供電電壓不一樣,TTL常用5V供電,CMOS:5V、3.3V、2.4V、1.8V

③TTL抗干擾能力弱,噪聲容限小,主要是因為CMOS邏輯電平范圍寬,高電平閾值區間與低電平區間的距離大,抗干擾能力強;但CMOS器件輸入阻抗大,容易捕捉干擾,噪聲大。但CMOS輸出阻抗低,在KΩ范圍內;CMOS器件不用的輸入引腳必須接地或者固定電平,(即注意靜電防護)而TTL器件引腳懸空默認高電平。

④TTL功耗大,CMOS功耗低,靜態功耗幾乎沒有,電平切換才有大電流。

⑤TTL器件工作速度快,傳輸延時5~10ns;cmos傳輸延時25~50ns。

集成邏輯門的性能參數

1、噪聲容限:在工作過程中,輸入端允許加入的干擾噪聲大小

低電平噪聲容限:正脈沖有影響

高電平噪聲容限:負脈沖有影響

噪聲容限越大,抗干擾能力越強

2、輸入端負載特性

在電路的實際使用過程中,通常會在輸入端和地之間加一個輸入電阻,輸入負載特性就是輸入電壓與輸入電阻之間的關系

【注】CMOS輸入端沒有電流,輸入電阻大小無所謂,無論多大電阻都不會改變輸入本來的狀態

3、平均傳輸延遲時間

由于晶體管的導通和截至都需要一定的時間,因此當集成邏輯門電路的輸入信號發生變化時,輸出信號的變化并不是立刻的,中間存在一定的延遲時間

平均傳輸延遲時間用tpd表示,是衡量門電路工作速度的重要指標,tpd越小,邏輯門電路的工作速度就越快

4、集成邏輯門器件的功耗

集成邏輯門器件的功耗是指在正常工作所消耗的功率,用PD表示

CMOS集成邏輯門的功耗相較于TTL邏輯門的功耗要低

扇入(fan-in)和扇出(fan-out)系數

扇入系數Ni :一個邏輯門電路所能允許的輸入端數目的個數

扇入系數No:一個邏輯門電路所能驅動同類門電路的最大個數,扇出系數越大,表示門電路帶負載能力越強

扇入與扇出系數反映了門電路的輸入端數目和輸出驅動能力的指標。

扇入越大越好,扇出越大越壞。在設計中,盡量減小扇出。對于一定扇出數的電路,電路的工作頻率隨之確定,一般工作頻率越高,扇出數越小。

扇出系數(Fan-out)

扇出系數表達的是驅動能力,即帶電路負載的能力,同時也指的是對于一個門電路來講,它能帶自己同樣類型的門有多少個。

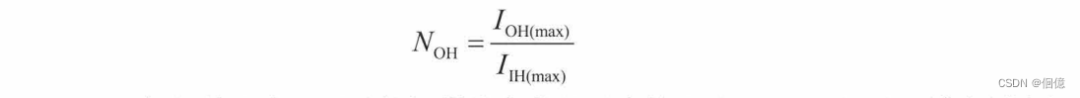

當輸出達到IOH時是能帶載的最大能力,由此計算扇出系數

當輸出電流大于IOH,輸出的高電平得不到保證

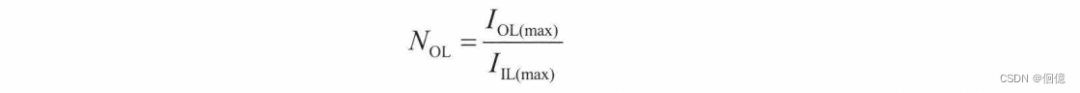

輸出0時,帶的負載門電流是往里流【灌電流】會抬高輸出電壓

輸出1時,帶的負載門電流是往外流【拉電流】會拉低輸出電壓

邏輯門輸出高電平時的扇出系數NOH為:

邏輯門輸出低電平時的扇出系數NOL為:

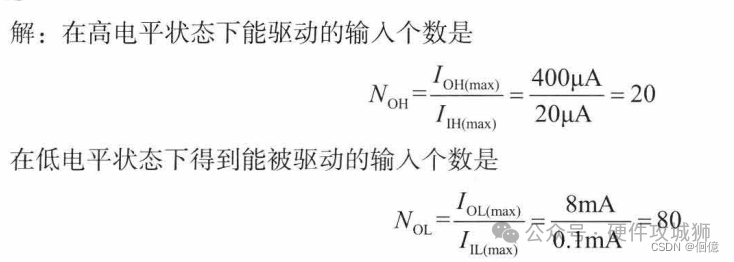

例:已知某門電路的電流參數為IOL(max) = 8mA,IIL(max) = 0.1mA,I

OH(MAX) = 0.4mA,IiH(max) =20uA,求可以帶多少個同類門電路的輸出

【注】在實際應用過程中如果高電平扇出系數和低電平系數不同,應采用較小的那個

NO=(NOL,NOH)min

例如TTL反相器,能夠帶TTL反相器個數數多少?

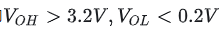

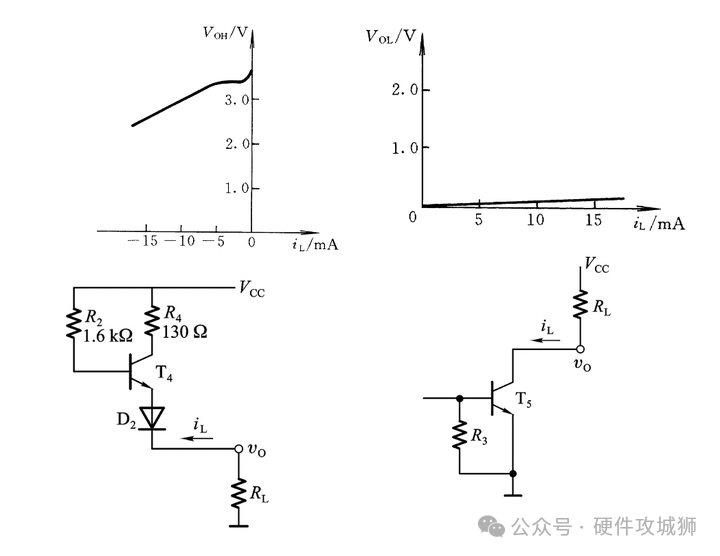

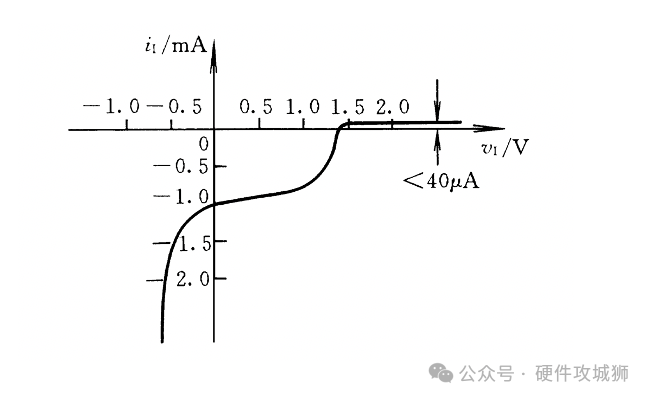

扇出系數取決于什么?由于TTL電路不管是高低電平電路,輸入都是要取電流的。而TTL電路的輸出存在著特性:無論輸出高電平還是低電平,都會隨著電流的增加電壓往不理想方向變化?因此就存在這么一個問題——帶多少負載還處在理想范圍?

由于每個輸入都取電流,現在要做的事情:雖然輸入取了電流,但帶完負載后輸出仍然能夠滿足噪聲容限極限電平值,即

因此我們可以根據下圖所示輸出高低電平特性曲線,得到

對應的電流是多少?

然后根據下圖所示的輸入電壓電流曲線來找到每個門輸入高低電平對應的電流分別是所少

最后高低電平分別進行:門輸出電流/門輸入電流,從這兩個值中選擇最小的一個就是扇出系數。

理想的的CMOS電路的驅動能力無限,因為CMOS電路不取電流,電壓傳遞有這個效應建立起來就可以。一般來說CMOS門電路帶負載能力比TTL門電路更強一點,故扇出系數遠比TTL電路高,因為正常電壓傳輸不需要電流。

TTL電路,其扇出系數一般為(8~10),CMOS門電路的扇出系數一般為(20~25)。

由于CMOS集成電路的輸入阻抗極高,因此電路的輸出能力受輸入電容的限制,但是,當CMOS集成電路用來驅動同類型,在低頻(< 1MHz)的工作條件下,如不考慮速度,CMOS電路的扇出數可以達到50以上的輸入端。

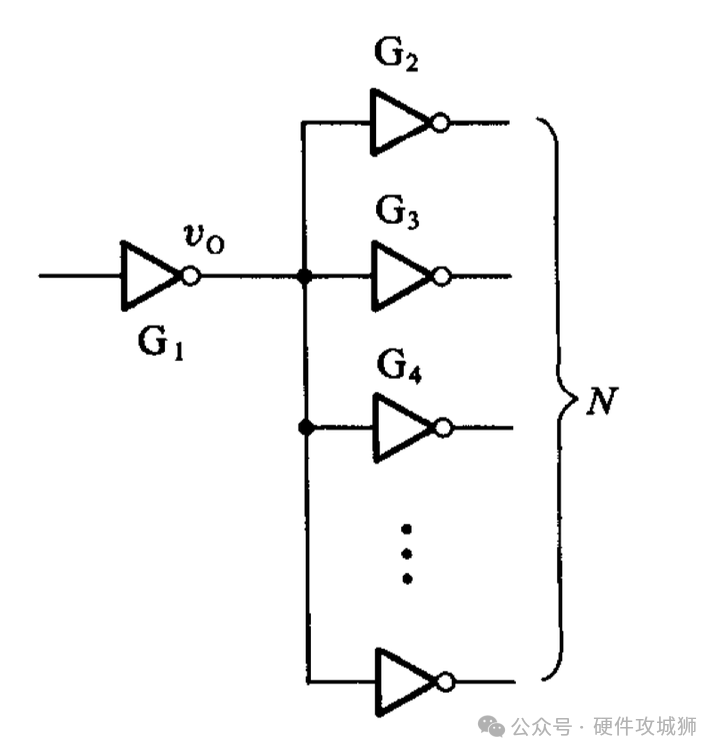

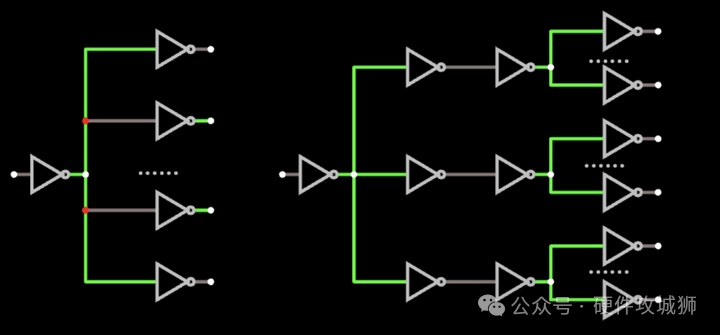

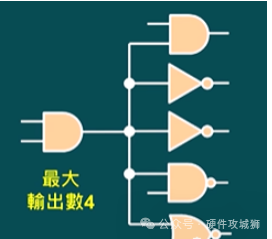

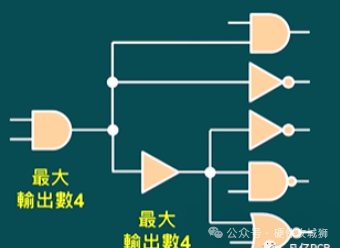

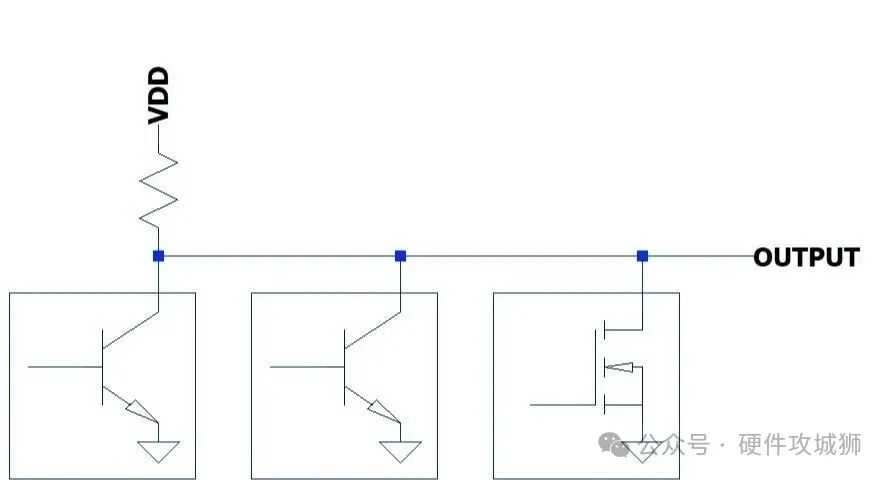

若門的驅動能力不夠時怎么處理? 每個門的輸出引入兩個反相器,然后它的輸出可以變成新的門扇出系數。從而原始門的扇出系數等于新的所有輸出扇出系數之和,如下圖所示:

為什么現在大部分數字芯片使用CMOS工藝而不是TTL工藝?

主要是因為TTL器件的邏輯單元三極管是電流驅動型器件,穩定時損耗高,發熱量大,無法做集成度比較高的芯片。但是TTL電路的延遲比CMOS電路的小。

邏輯電平驅動類別

TTL電路是電流控制器件,而CMOS電路是電壓控制器件

單端邏輯電平:電壓驅動

單端邏輯電平:電流驅動

TTL、LVTTL

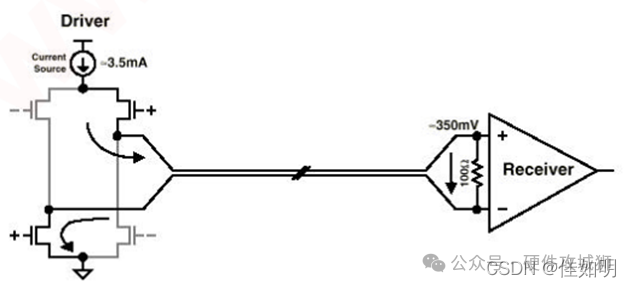

差分邏輯電平(高速):電流驅動

ECL、PECL/LVPECL、LVDS、CML、HCSL/LPHCSL、TMDS

差分邏輯電平(高速):電壓驅動

VML

在傳輸線理論分析的時候,總是分析一個電壓波形的傳遞,并未考慮電流能力(驅動電流的大小),而事實上,對于高速信號來說,為了要快速響應,或者長距離傳輸,都是采用電流驅動的。

LVDS/LVPECL/CML等電平,在輸入端都有匹配電阻(50/100歐姆),這些電阻對于輸入門來說承擔的是把電流轉換成電壓的任務。因為對于一個輸入邏輯門來說,它對電流的需求并不大,它需要的是足夠的電壓幅度。既然芯片需要的是電壓幅度,為何輸出端不直接把電壓傳遞過來呢。那是因為電壓傳遞速度比較慢,并且容易受到干擾。而電流驅動反應速度快,抗干擾能力強。

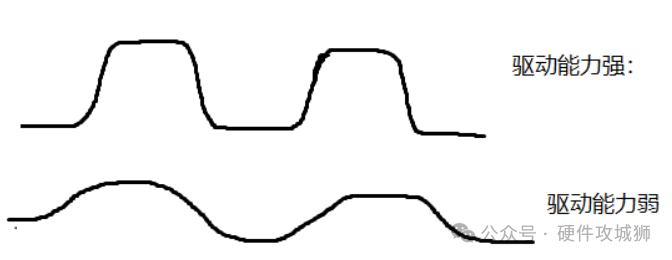

電流驅動型鏈路,在接收端都有一個電流轉成電壓的電路(這個電路同時也承擔著匹配的任務)。大家可以理解一下CMOS電路,如果驅動能力比較弱的話,信號的上升沿和下降沿就會很緩,能傳的頻率就會很低。

例如 LVDS差分電路是電流控制型器件,但采用CMOS工藝,在接收端轉換成350mv電壓。

拉電流和灌電流是衡量驅動能力的參數

由扇出的定義式我們可以看出扇出系數同灌電流和拉電流密切相關。

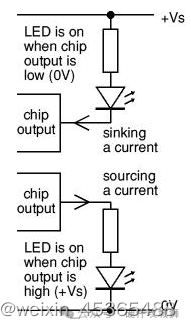

當邏輯門輸出端是低電平時,灌入邏輯門的電流稱為灌電流(sink current),一般是要吸收負載的電流。灌電流越大,輸出端的低電平就越高。由三極管輸出特性曲線也可以看出,灌電流越大,飽和壓降越大,低電平越大。邏輯門的低電平是有一定限制的,它有一個最大值UOLmax。在邏輯門工作時,不允許超過這個數值。

當邏輯門輸出端是高電平時,邏輯門輸出端的電流是從邏輯門中流出,這個電流稱為拉電流(sourcing current),一般是對負載提供電流。拉電流越大,輸出端的高電平就越低。這是因為輸出級三極管是有內阻的,內阻上的電壓降會使輸出電壓下降。拉電流越大,高電平越低。邏輯門的高電平是有一定限制的,它有一個最小值UOHmin。

由于高電平輸入電流很小,在微安級,一般可以不必考慮,低電平電流較大,在毫安級。所以,往往低電平的灌電流不超標就不會有問題,用扇出系數來說明邏輯門來同類門的能力。

所以,拉電流與灌電流反映了輸出驅動能力。(芯片的拉、灌電流參數值越大,意味著該芯片可以接更多的負載,因為,例如灌電流是負載給的,負載越多,被灌入的電流越大)。

對一個端口而言,如果電流方向是內部電流通過芯片引腳從芯片內流出的則是“灌電流”,比如一個IO通過一個電阻和一個LED連接至VCC,當該IO輸出為邏輯0時能不能點亮LED,去查該器件手冊中sink current參數。

對一個端口而言,如果電流方向外部電流通過芯片引腳向芯片內流入的則是“拉電流”,比如一個IO通過一個電阻和一個LED連至GND,當該IO輸出為邏輯1時能不能點亮LED,去查該器件手冊中sourcing current參數。

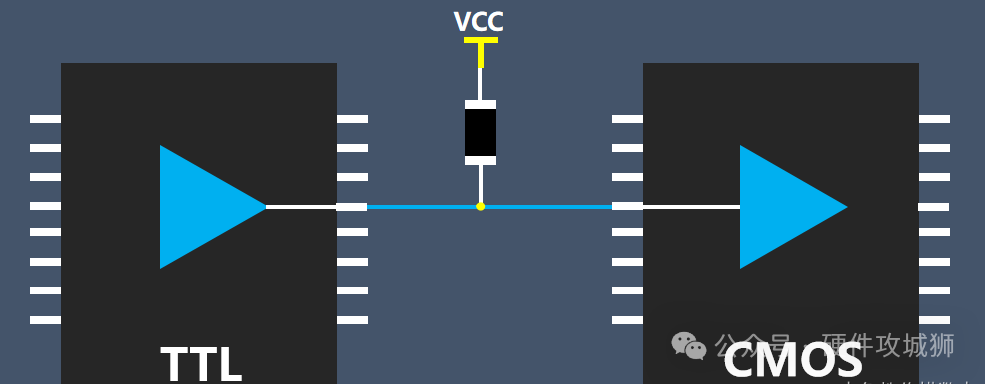

TTL和CMOS器件相互驅動分析

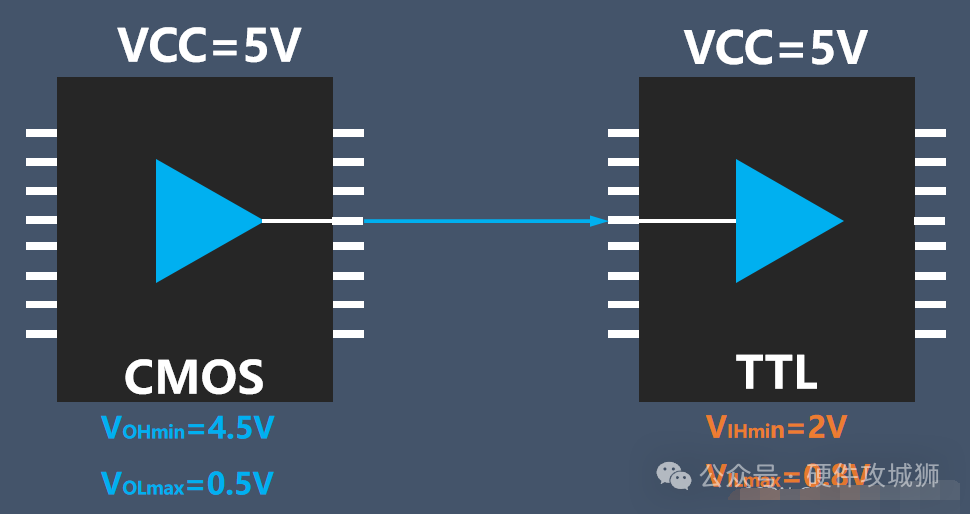

比較兩者輸入輸出電平,很明顯TTL不能直接驅動CMOS器件,而后者可直接驅動前者;所以TTL驅動CMOS需要在外圍加上拉電阻,而且TTL的VCC接了電阻,高電平驅動能力很小。

當CMOS器件IO做輸出,TTL器件IO做輸入時,TTL輸入高電平最小為2V,輸入低電平雖大為0.8V,顯然CMOS器件的輸出電平可以滿足TTL器件的輸入高低電平的范圍。

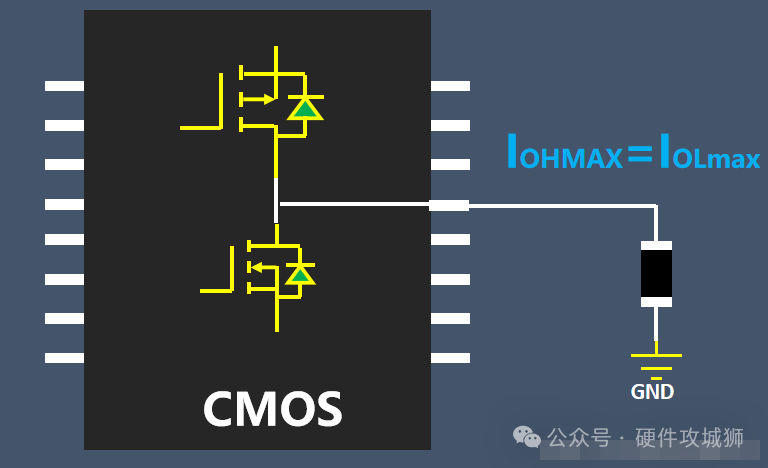

CMOS器件的高電平和低電平驅動能力相近,一般都可以到5mA左右,

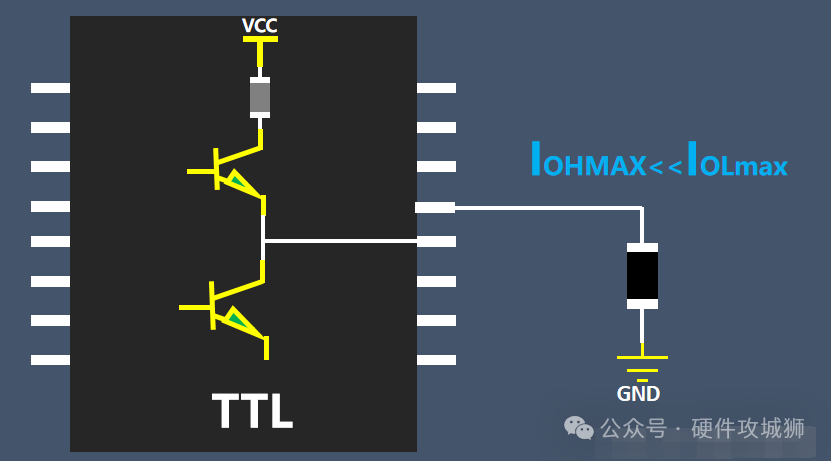

但是TTL器件IO的高電平驅動能力要遠小于低電平驅動能力,一般高電平驅動能力只有0.幾mA的樣子,但是低電平驅動能力可以到5mA左右。這是因為TTL器件IO口上面的三極管都是加了電阻的,這個電阻值在幾百歐的樣子,這就限制了其高電平的驅動能力。

由于CMOS器件輸入阻抗高,懸空的話會很容易受到干擾,所以一般CMOS器件不用的輸入引腳在數據手冊上都是要求上拉或者下拉。

數字電路中Buffer芯片設計

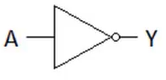

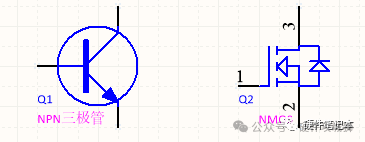

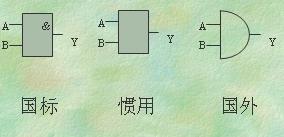

反相器是最基本門電路之一非門

反相器,顧名思義,在邏輯上起到的是取反作用,在數電中學習了許多反相器,其中最重要的兩個是CMOS反相器和TTL反相器。

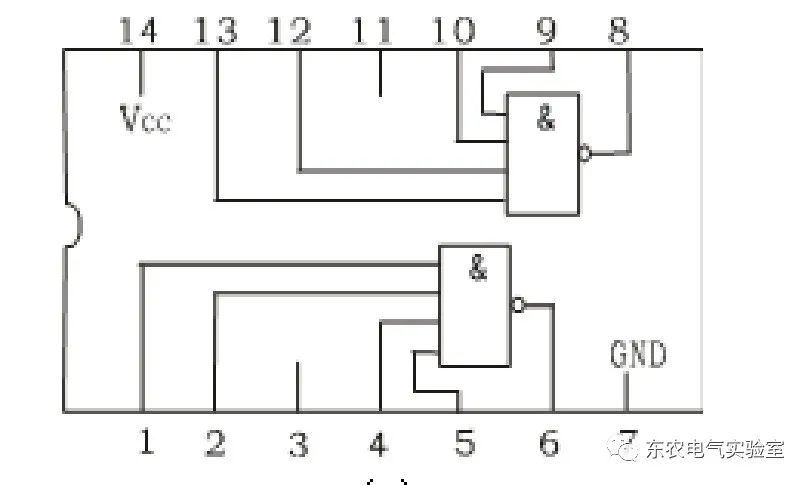

【注意】TTL電路輸入用的是多發射極的三極管,多發射級三極管輸入端是與的關系。

反相器驅動能力參數 ---- 動態特性

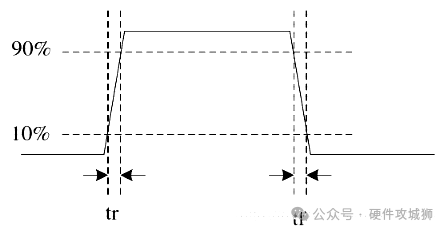

1、Transition Time(轉換時間):

上升時間和下降時間統稱為Transition Time,也有定義為20%到80%。

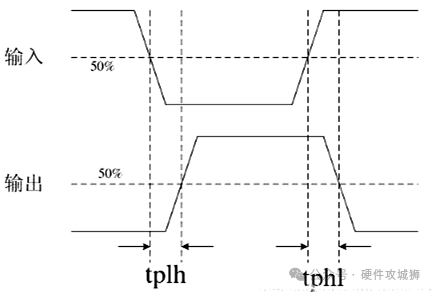

2、Propagation Delay(傳播延時):

在輸入信號變化到 50%Vdd到輸出信號變化到50%Vdd之間的時間。

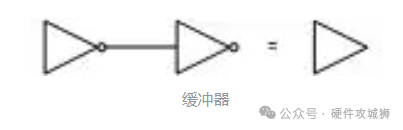

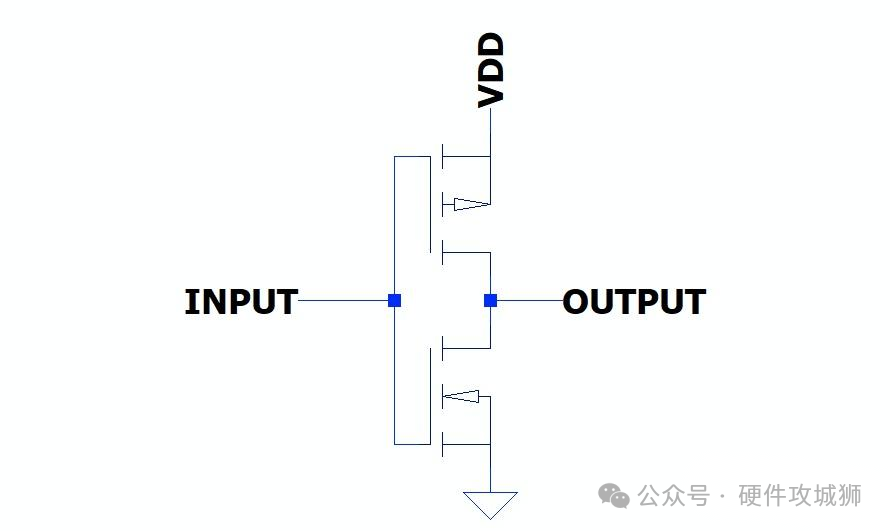

Buffer基本構成

在CMOS集成電路中,反相器由兩個互補的晶體管NMOS+PMOS組成,同時利用兩級反相器即可構成緩沖器,又稱為(buffer)門即buffer。

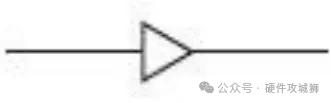

緩沖器可用如下符號表示。

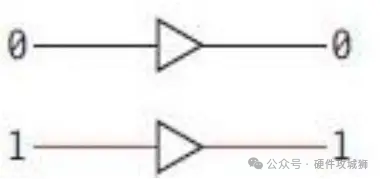

除了輸入端的小圓圈,這個符號與反向器是很相似的。很明顯,緩沖器 “沒有什么作用”,它的輸入與輸出是相同的。

緩沖器的輸入與輸出

緩沖器可以用于延遲信號,這是因為繼電器需要一點時間才會被觸發。

其中緩沖器與非門幾乎是兄弟,因為其外形實在太相似了,下面來看一下反相器(非門)的符號:

緩沖器其邏輯關系為:

當輸入為0時,輸出也為0

當輸入為1時,輸出以為1

那么這個門電路沒有任何邏輯運算,他與非門也只差一個小圈圈,其作用是什么?

緩存的功能為:用來放大或增強電壓或訊號電流,來達到功率增加其驅動能力。

什么意思?上圖:

如圖所示,這是一個四輸出的邏輯門,而其負載有5個門電路,顯然會發生驅動力不足,那么可以在輸出端前串聯一個緩沖器,如圖所示:

這樣可以將四輸出邏輯門的驅動能力增強。這就是緩沖器的作用,當然這是最簡單的緩存器,也可以用三態邏輯門,來制作緩沖器。

Buffer提高驅動能力/帶負載

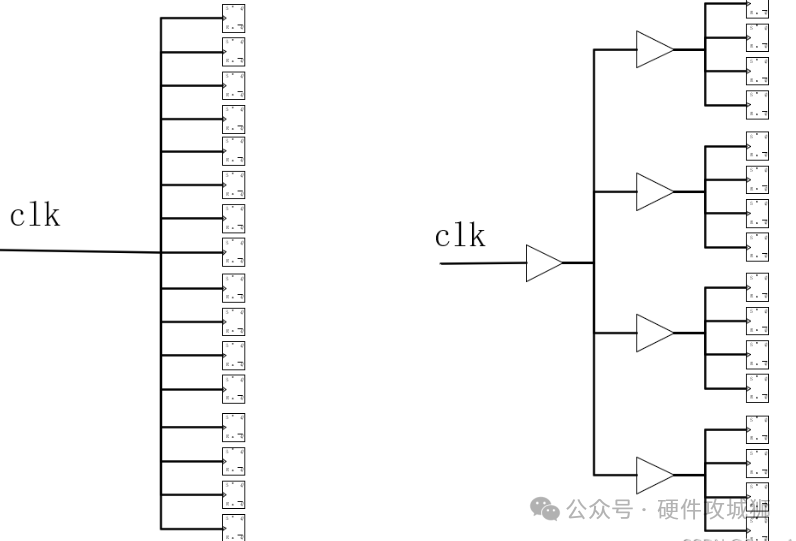

buffer一般是幾級器件尺寸逐步增大的反相器或類似結構的電路。buffer實際就是兩個串聯的反相器,常用于時鐘路徑中,用于增加時鐘驅動能力,使得時鐘clock具有良好的上升沿和下降沿。時鐘buffer本身是輸入負載較小,輸出驅動能力較強。因此前級電路驅動buffer容易,而buffer驅動后級電路也比較容易。

Buffer有同相、反相、三態輸出、時鐘緩沖器、總線輸出緩沖器、驅動器等,不同Buffer的作用:

增強驅動能力,輸出電流不夠的時候通過buffer可以增加輸出電流,加強驅動能力。

減少負載數量,負載數量很多時可以通過增加buffer來減少同時驅動的負載數量。

減小連線負載,當數據線很長的時候,負載電容很大,延時很長,增加buffer分割連線,減小驅動負載,當然這時候需要比較buffer本身延時和連線延時,只要連線延時明顯大于buffer自身延時就可以采用這種方式。

復制時鐘信號,單個晶振或多個晶振提供參考給多個芯片,會有信號完整性和成本問題,一個晶振加buffer可以做到最佳性價比。

轉換時鐘信號格式,晶振輸出信號和芯片需要的參考時鐘信號不匹配時可以通過buffer實現轉換。

轉換時鐘信號電平,已有頻率源和實際芯片要求的參考電平不一致時,可以使用buffer來轉換。

兩個重要作用:

1.提高驅動能力

buffer是一種寬高比很大的mos管,寬高比大意味著電流大,驅動能力高。

在扇出很大的wire中插入buffer可以提高帶負載能力,常見于時鐘樹中。

2.確保信號時序正確

當一條wire很長時,延遲很大(delay正比于長度的平方,設長度為1,delay為1),這時在中間插入buffer,wire delay變為1/4+1/4=1/2,只要buffer delay小于1/2,則buffer的插入可以縮短wire delay。

當一條wire的延遲不大時,如果有hold violation(表現為數據到達過快,需要滯后到達),則插入buffer,利用buffer delay可以修正這個hold violation。

增強驅動能力/減少連線負載/降低delay都是如何體現的?

當數據連線很長時,連線負載電容很大,導致存在很大的延時。此時插入buffer將連線分割成幾個連線,每個buffer驅動的負載較小,因此能夠有效減少延時,雖然buffer本身也具有延時,但是插buffer減少的連線延時明顯大于buffer自身延時就可以采用插buffer的方式。

通過插buffer的方式減少了電路的負載電容,負載電容減少后,同樣電壓的情況下,對電容充電速度快(上升沿陡峭),同樣電容小時存儲的電容小,放電所需的時間短(下降沿陡峭)。一句話來說就是: 插buffer的方式減少了電路的負載電容,從而增大了電路驅動能力。

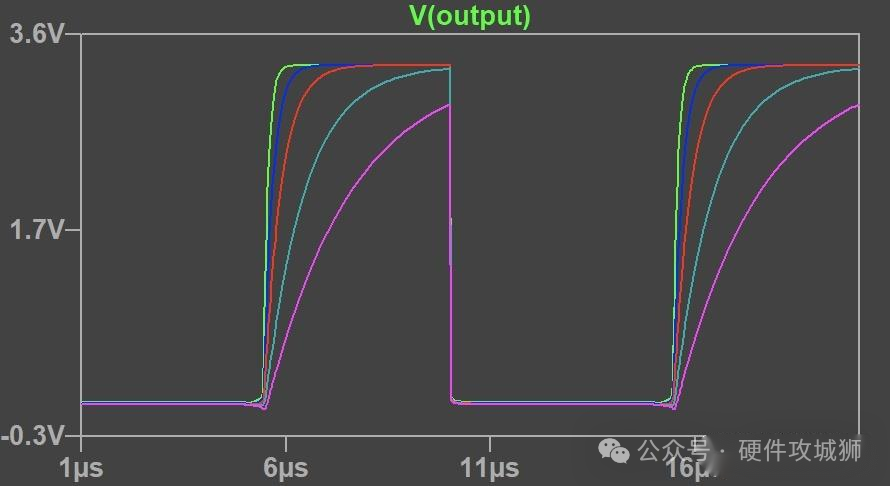

如下圖所示:

驅動能力強:擺幅大,上升快

驅動能力弱:擺幅小,上升慢

時鐘驅動16個reg時,負載很大,時鐘上升很慢,并且時鐘擺幅小,此時插入4個buffer。加buffer之前你的時鐘直接驅動寄存器或者很多個寄存器。加buffer以后你的時鐘只驅動buffer,而你的buffer會去驅動寄存器。時鐘buffer本身是輸入負載較小,輸出驅動能力較強的。而且通常會做成一個時鐘buffer網絡來驅動設計里面全部的寄存器,并保證整個時鐘網絡上的信號有很好的transition,以及平衡從時鐘源到所有寄存器的insertion delay.寄存器的CK端接在時鐘上面, 在時鐘上加入buffer是在做時鐘樹的時候讓時鐘到每一個寄存器的CK端的SKEW盡可能的小,還有增加驅動的功能。

工作原理:通過插buffer的方式減少了電路的負載電容,負載電容減少后,同樣電壓的情況下,對電容充電速度快(上升沿陡峭),同樣電容小時存儲的電容小,放電所需的時間短(下降沿陡峭)。一句話來說就是: 插buffer的方式減少了電路的負載電容,從而增大了電路驅動能力。

不插buffer會發生什么情況?

不插buffer會導致驅動能力不夠,通常是兩種情況

第一種是輸出電流不夠,導致信號狀態異常,這常常發生在后級電路對輸入電流有要求的時候,另一種則是輸出電流不夠,導致信號上升下降沿太差,這常常發生在后級電路的輸入電容較大的情況。

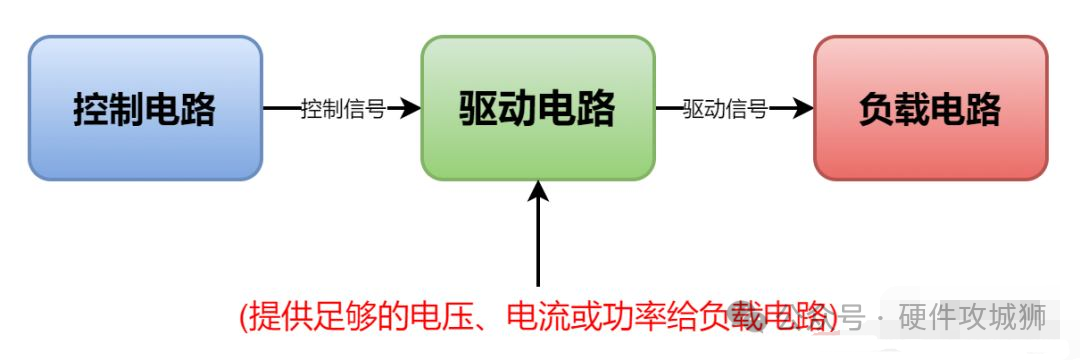

驅動電路定義

驅動電路(Drive Circuit):如下圖所示,驅動電路位于控制電路與負載電路之間,將控制電路的控制信號轉化為負載電路所需的驅動信號,提供足夠電流或功率驅動負載電路;

驅動電路:晶體管與MOS管構成的放大電路,開關電路;驅動IC;

一、驅動電路作用

在電源或者硬件設計中,無論是三極管還是MOS管,一般都需要驅動電路進行驅動。驅動電路的主要作用有:

1.提高系統可靠性

2.提高變換效率(開關器件開關、導通損耗)

3.減小開關器件應力(開/關過程中)

4.降低EMI/EMC

提供足夠的驅動能力

打個比方,一個單片機的高電平信號為5V,而5V是沒辦法直接驅動12V或者24V的繼電器正常工作的。通常這時候就需要引入驅動電路,使5V也能夠控制末端繼電器的開斷。

保證開關管良好的開關狀態

在一個電路中,開關管不能太快或者太慢,太快會對電磁造成很大的干擾,太慢開關損耗太大。

保證器件的可靠性,避免過壓和過流

由于開關寄生參數的存在,在導通或者關斷是,往往產生很大的電壓電流尖峰,這會對電路的性能和器件的可靠性有影響。

二、常見驅動方式

1、直接驅動

直接驅動電路是由單個電子元器件(如二極管、三極管、mos管、電阻、電容等)連接起來組成的驅動電路,電路中不具備電氣隔離,多用于功能簡單的小功率驅動場合。在復雜的數字電源系統中,直接驅動電路由于集成度低、故障率高等原因,已被逐漸淘汰。

功率開關管驅動

以控制信號類別分類,驅動方式可以分為電流驅動和電壓驅動。

電流驅動

電流驅動實際上是通過控制三極管導通來控制信號的通斷。

控制方式: 電流型驅動是通過控制電流的大小來實現設備或器件的操作。驅動器提供恒定的電流,設備的性能取決于電流值。

穩定性: 電流型驅動在某些情況下可以提供更穩定的操作,因為電流不受電阻變化的影響。這對于一些需要精確控制的應用很有用。

靈敏度: 電流型驅動通常比電壓型驅動更適用于一些對電流變化較為敏感的設備,如光電二極管(Photodiode)和激光二極管(Laser Diode)。

適用范圍: 電流型驅動常用于需要對電流進行精確控制的設備,如光電子器件、傳感器等。BJT常用于低功率數字電源

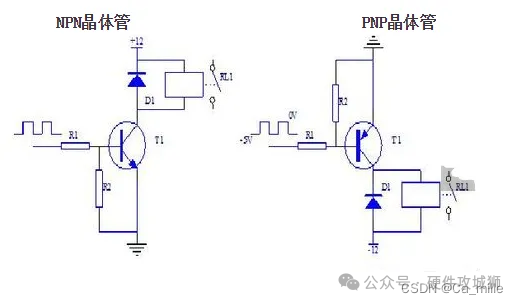

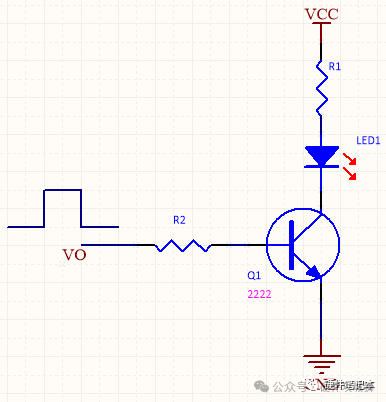

在NPN晶體管電路中,R1起限流作用、R2起下拉作用。因為在電路關斷之后,三極管be端電壓緩慢下降,可能會處于較長時間的放大狀態,會損壞三極管。因此需要下拉電阻R2,使得關斷時積極電壓迅速拉低,提高三極管的關斷速度。

1、當輸出為0V時,三極管截止,繼電器線圈無電流流過,為OFF狀態;

2、當輸出為+Vcc時,三極管飽和,繼電器線圈流過一定的電流,繼電器吸合,為ON狀態;

3、當輸入電壓又+Vcc變為0時,,三極管由飽和變為截止。

由于繼電器線圈相當于一個電感,由于電感的特性是通直流、阻交流,在斷開瞬間,線圈兩端會產生較大的反向電動勢,電壓值可達一百多伏,這個電壓加上電源電壓作用在三極管的集電極上足以損壞三極管。所以需要并聯一個續流二極管,為自感電勢提供泄放通路。(續流需要選擇肖特基二極管,有利于快速泄放電勢)

電壓驅動

電壓驅動實際上是通過控制MOS管導通來控制信號的通斷。

控制方式: 電壓型驅動是通過控制電壓的大小來實現設備或器件的操作。驅動器提供恒定的電壓,設備的性能取決于電壓值。

靈活性: 電壓型驅動通常更靈活,適用于各種設備,因為不同設備可能對相同電壓產生不同的響應。

易于集成: 電壓型驅動適用于集成電路(IC)等多種設備中,因為IC中通常使用電壓信號進行通信和控制。

適用范圍: 電壓型驅動常用于需要對電壓進行精確控制的設備,如邏輯門、存儲器等。常用于中小功率數字電源。在高頻場合多采用變壓器或專用芯片進行驅動。

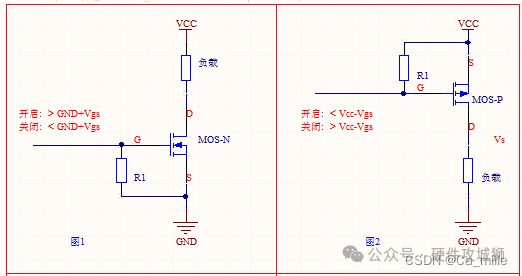

圖1是N管常用的電路接法。N管S端接地,D端接負載。當G端信號大于Vgnd+Vgs的時候,MOS管開啟,當信號電壓小于Vgnd+Vgs時關閉。R1電阻為下拉電阻。

圖2是P管常用的電路接法。P管S端接Vcc,D端接負載。則當G端信號電壓小于Vcc-Vgs的時候,MOS開啟,當信號電壓大于Vcc-Vgs時關閉。

電流和電壓特點

電流驅動型:

優點:精度高、響應速度快、效率高、抗干擾能力強、驅動功率大、耐壓、容量大

缺點:開關速度慢、成本高、穩定性差

電壓驅動型:

優點:開關速度快

缺點:不適合于高電壓的場合、抗干擾能力弱

從器件來說:

電壓驅動的如:

場效應管,因為它的內阻很大,加電壓控制時電流很小,近似為零,所以可以理解成:電壓驅動;

電流驅動的如:

普通的NPN、PNP型三極管,因為它的內阻較小,加電壓控制時電流相對較大一般小功率的都有100uA以上,大功率的可達20mA以上),所以可以理解成:電流驅動;

從控制原理來說:

電壓驅動的如:場效應管,它是通過加到G、S端的電壓(微觀的就是電場)來控制D、S內部通道的寬窄(即通道可變)來控制D、S兩端電流;

電流驅動的如:普通的NPN、PNP型三極管,是通過加到B、E端的電流(微觀的就是電子的流動)來控制C、E內部的電流流動(即通道不變)。

電壓驅動型器件內阻大,加電壓后電流小,只需要較小的驅動功率,場效應晶體管(FET)是電壓控制器件、MOS電路是電壓控制器件,又比如氣體型霓虹燈,電壓低了連亮都不亮。亮了以后電流很小,那么就把它確定為電壓型器件。

電流驅動型器件內阻較小,加電壓后電流較大,需要較大的驅動功率,雙極型晶體管(BJT)是電流控制器件、TTL電路是電流控制器件,又比方發光二極管,其輸入電壓基本是一個確定值,提高電流可以改變亮度,減小電流降低亮度,它確定為電流型器件。

電壓驅動(Voltage Drive)是通過控制電路的輸出電壓來實現對電路的控制。在電路中,電壓是電流的驅動力,通過控制電壓來控制電路中的電流和功率。電壓驅動方式通常使用開環控制,即電路輸出與輸入電壓成正比關系。當輸入電壓變化時,輸出電壓和輸出電流也會隨之變化,電路的穩定性較差。

電流驅動(Current Drive)是通過控制電路的輸出電流來實現對電路的控制。在電路中,電流是電壓和電阻的函數,通過控制電流來控制電路的電壓和功率。電流驅動方式通常使用閉環控制,即電路輸出電流與輸入電流成正比關系。當輸入電流變化時,輸出電流會自動適應,電路的穩定性較好。

電壓驅動方式比電流驅動方式適合用于復雜的電路控制。例如,在數碼電路中,由于需要對各個部件進行動態調節,因此要求輸出電壓穩定,而電流驅動方式則無法滿足這一需求。而在高功率功放、磁控管等高阻負載的電路中,電流驅動方式優勢更加明顯。這些負載的阻值變化范圍大,且負載阻值與電流成正比,要求輸出電流能夠自適應變化。

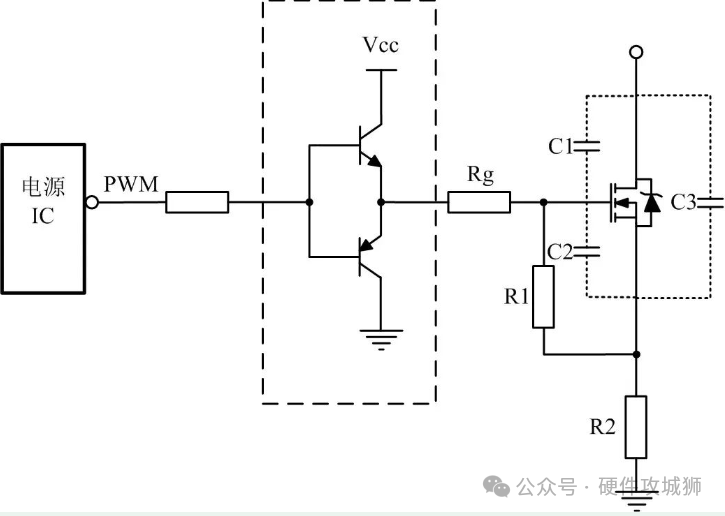

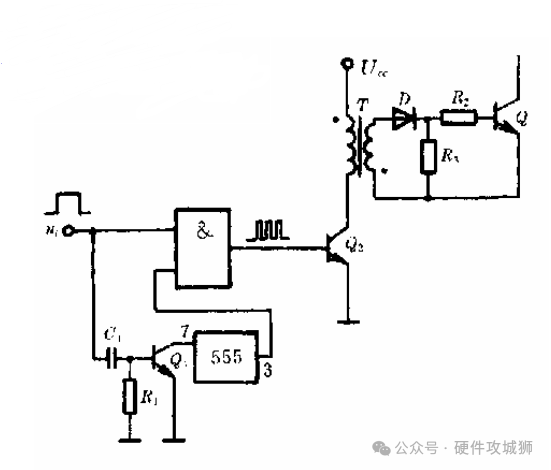

2、推挽驅動

當電源IC驅動能力不足時,可用推挽驅動。

這種驅動電路好處是提升電流提供能力,迅速完成對于柵極輸入電容電荷的充電過程。這種拓撲增加了導通所需要的時間,但是減少了關斷時間,開關管能快速開通且避免上升沿的高頻振蕩。

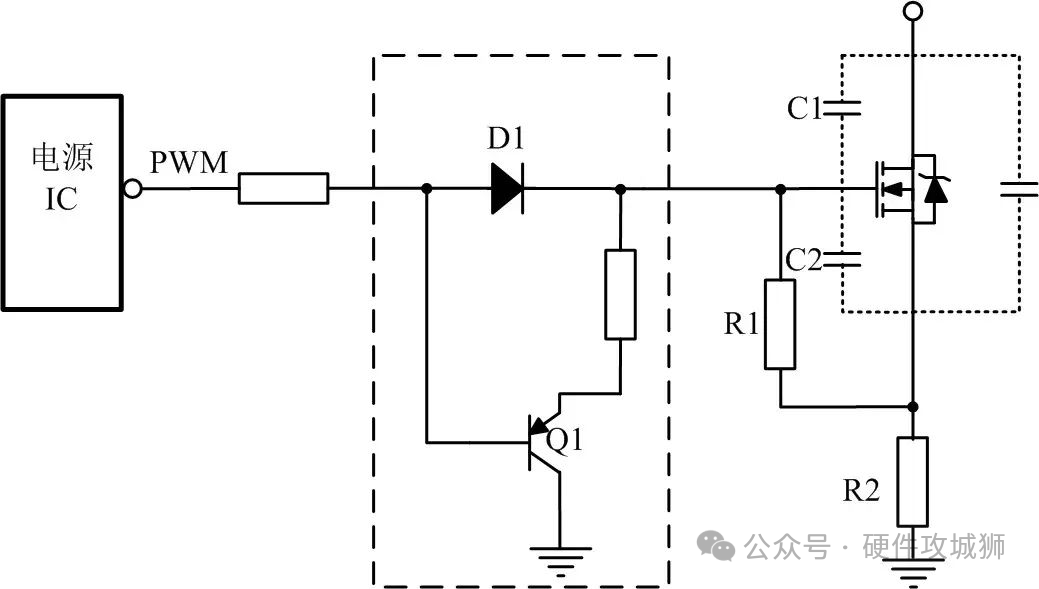

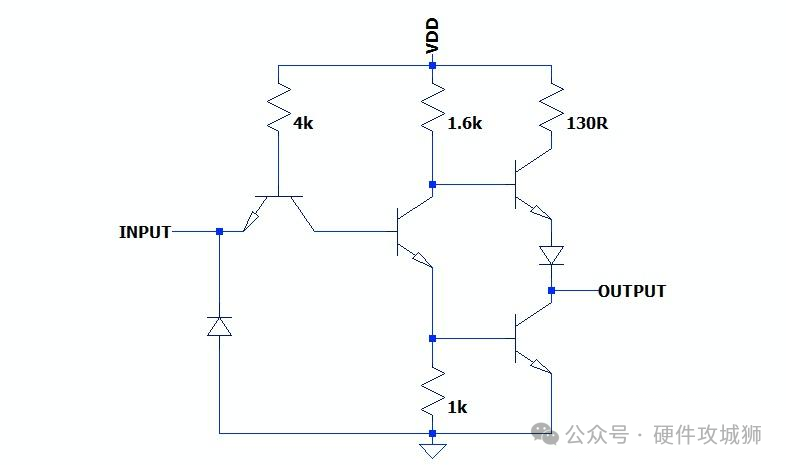

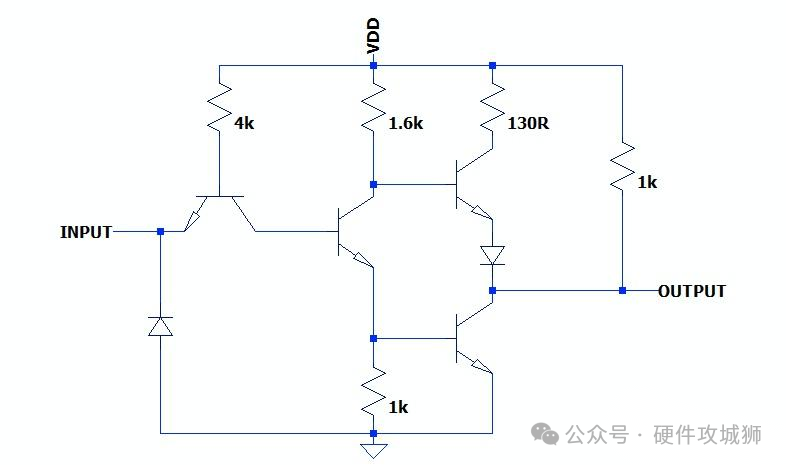

如下圖所示,推挽驅動電路包含一個PNP三極管及一個NPN三極管,采用互補輸出。輸入高電平時,上管NPN開啟,下管PNP關閉,驅動MOS管開啟;輸入低電平時,上管NPN關閉,下管PNP開啟,驅動MOS管關閉。

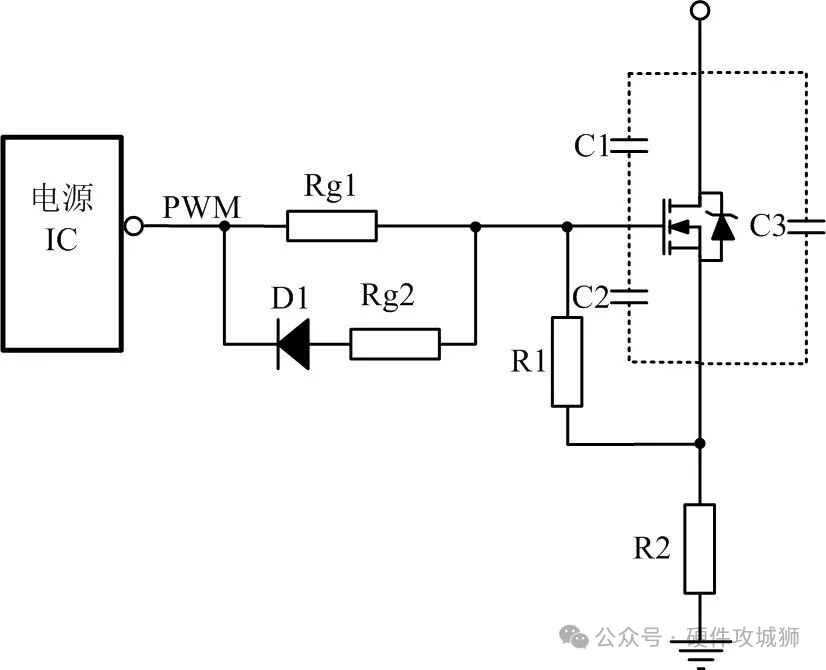

加速關斷驅動

MOS管一般都是慢開快關。在關斷瞬間驅動電路能提供一個盡可能低阻抗的通路供MOSFET柵源極間電容電壓快速泄放,保證開關管能快速關斷。

為使柵源極間電容電壓的快速泄放,常在驅動電阻上并聯一個電阻和一個二極管,如上圖所示,其中D1常用的是快恢復二極管。這使關斷時間減小,同時減小關斷時的損耗。Rg2是防止關斷的時電流過大,把電源IC給燒掉。

如下圖,用三極管來泄放柵源極間電容電壓是比較常見的。如果Q1的發射極沒有電阻,當PNP三極管導通時,柵源極間電容短接,達到最短時間內把電荷放完,最大限度減小關斷時的交叉損耗。

還有一個好處,就是柵源極間電容上的電荷泄放時電流不經過電源IC,提高了可靠性。

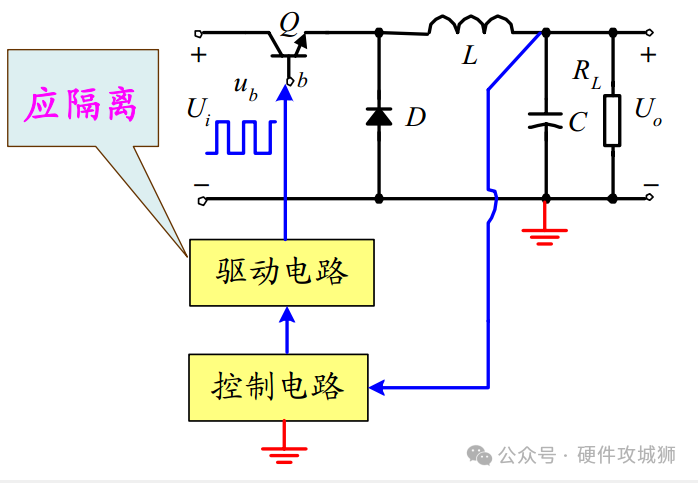

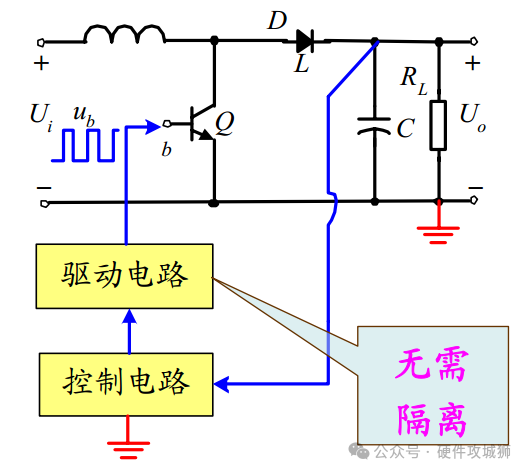

3、隔離驅動

電路包含隔離器件,常用的有光耦驅動、變壓器驅動以及隔離電容驅動等。其中光耦驅動電路具有簡單、可靠、開關性能好等特點。而變壓器驅動電路不僅可以起到驅動作用,還可用于電壓隔離和阻抗匹配。

驅動電路為什么要采取隔離措施

安規問題,驅動電路副邊與主電路有耦合關系,而驅動原邊是與控制電路連在一起, 主電路是一次電路,控制電路是ELV電路,一次電路和ELV電路之間要做加強絕緣,實現絕緣要求一般就采取變壓器光耦等隔離措施。

注:

ELV(特低電壓)電路:在正常工作條件下,在電路的任意兩個導體之間或任一導體與地之間電壓的交流峰值不超過42.4V或直流值不超過60V的二次電路。

一次電路:直接與交流電網電源連接的電路。通常是由高壓線路、變電站以及與之相連的發電機和負載組成。特點是電壓較高,通常在110 kV至1000 kV范圍內,能夠實現大功率的傳輸和供應。

驅動電路采取隔離措施的條件

控制參考地與驅動信號參考地(e極)不同—驅動電路應隔離。

控制參考地與驅動信號參考地(e極) 同—驅動電路無需隔離;

驅動電路隔離技術

驅動電路隔離技術一般使用光電耦合器或隔離變壓器(光耦合;磁耦合)。由于 MOSFET 的工作頻率及輸入阻抗高,容易被干擾,故驅動電路應具有良好的電氣隔離性能,以實現主電路與控制電路之間的隔離,使之具有較強的抗干擾能力,避免功率級電路對控制信號的干擾。

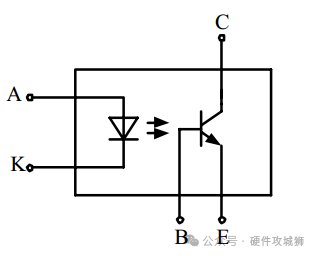

光耦隔離驅動可分為電磁隔離與光電隔離。采用脈沖變壓器實現電路的電磁隔離,是一種電路簡單可靠,又具有電氣隔離作用的電路,但其對脈沖的寬度有較大限制,若脈沖過寬,磁飽和效應可能使一次繞組的電流突然增大,甚至使其燒毀,而若脈沖過窄,為驅動柵極關斷所存儲的能量可能不夠。光電隔 離,是利用光耦合器將控制信號回路和驅動回路隔離開。該驅動電路輸出阻抗較小,解決了柵極驅動源低阻抗的問題,但由于光耦合器響應速度較慢,因而其開關延遲時間較長,限制了適應頻率。

典型光耦內部電路圖

光耦指的是可隔離交流或直流信號。

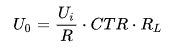

1.由IF控制Ic;電流傳輸比CTR-Current Transfer Ratio

2.輸入輸出特性與普通三極管相似,電流傳輸比Ic/IF比三極管“β ”小;

3.可在線性區, 也可在開關狀態。驅動電路中, 一般工作在開關狀態。

光耦基本電路

光耦的特點:

1. 參數設計簡單

2. 輸出端需要隔離驅動電源

3. 驅動功率有限

磁耦合-變壓器隔離

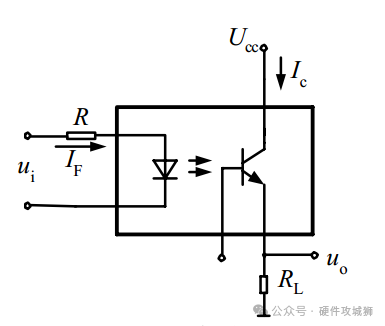

受高頻調制的單向脈沖變壓器隔離電路

磁耦合:用于傳送較低頻信號時—調制/解調

磁耦合的特點:

1.既可傳遞信號又可傳遞功率

2.頻率越高,體積越小-適合高頻應用

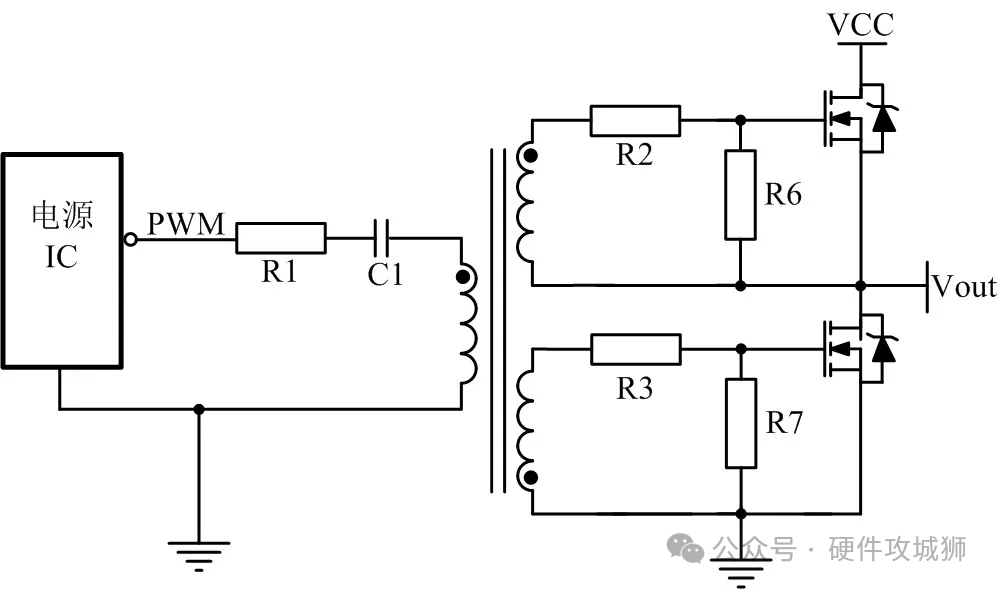

為了滿足高端MOS管的驅動,經常會采用變壓器驅動。其中R1目的是抑制PCB板上寄生的電感與C1形成LC振蕩,C1的目的是隔開直流,通過交流,同時也能防止磁芯飽和。

在第一個周期內OUTA 開啟,給變壓器一次繞組施加正電壓,上管感應導通。在接下來的一個周期內,OUTB 開啟(開啟時間與OUTA相同),在磁化電感上提供極性相反的電壓,下管導通。電路會產生兩個雙極性對稱的柵極驅動電壓輸出,符合半橋電路的控制要求。

專用驅動集成芯片

目前專用驅動芯片在數字電源中應用廣泛,許多驅動芯片自帶保護和隔離功能。根據其控制的功率器件數量,驅動芯片可以分為單驅芯片與雙驅芯片。其中雙驅芯片通常用于半橋、全橋等電源拓撲,因為需要一對互補的控制信號。而單驅芯片則更適用于buck、boost、反激等電源拓撲。

三、驅動能力

所謂驅動能力,是指前級電路的輸出信號可以使得后級電路有效響應,這個有效的包含兩層意思:

第一是前級輸出信號能被后級電路識別,

第二是在規定的時間內被后級電路識別。

驅動能力指輸出端口的電流流入/流出大小,但大部分情況指輸出端口的扇出能力。

扇出:一個輸出端口連接多個輸入端口。

從直流特性來講

數字器件的輸出端口有最大電流限制,超過電流限制,則有可能使輸出電平幅度變低/燒毀器件。比方說,某單片機GPIO口高電平時的最大輸出電流是20mA,那這個20mA規格就表征了該I/O口的電平驅動能力。而如果負載過大(比如小電阻),則負載電流有可能超過其最大輸出電流,這時我們說驅動能力不足。驅動能力不足的直接后果是輸出電壓下降,對邏輯電路來說,無法保持其高電平甚至會出現邏輯混亂,這種現象一般是不允許出現的。因此,從直流特性的角度,驅動能力就是指輸出端口的電流最大流入/流出能力。

從交流特性來講

由于輸入端口存在輸入電容,因此輸出端口電平反轉過程,可以認為是輸入端口電容充放電過程。輸出端口扇出越大,則充放電速度/電平反轉越慢,一定開關頻率的情況下存在一個最大的扇出值,因此當實際扇出值大于最大扇出值時,電平反轉速度過慢而無法滿足要求。因此,從交流特性角度來講,驅動能力也可以指器件輸出端口的扇出能力,不過扇出能力還是和上端口的電流的流入流出能力有關。

電路的的驅動能力是上一級的1/R,即電阻的倒數,驅動能力大,說明看過去的電阻小。電路的負載能力是下一級的load(即電容)總和,負載能力大,說明能驅動下級的器件就很多”。

究竟“驅動能力”和“負載能力”的區別是什么?

個人感覺是兩者是一樣的,都是代表上級電路可以驅動下級電路的能力的大小。

上下拉電阻會增強驅動能力嗎?

答:不存在上下拉電阻增強驅動能力這回事,因為除了OC輸出這類特殊結構外,上下拉電阻就是負載,只會減弱驅動力。

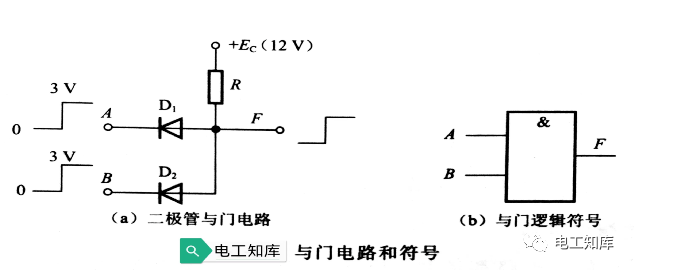

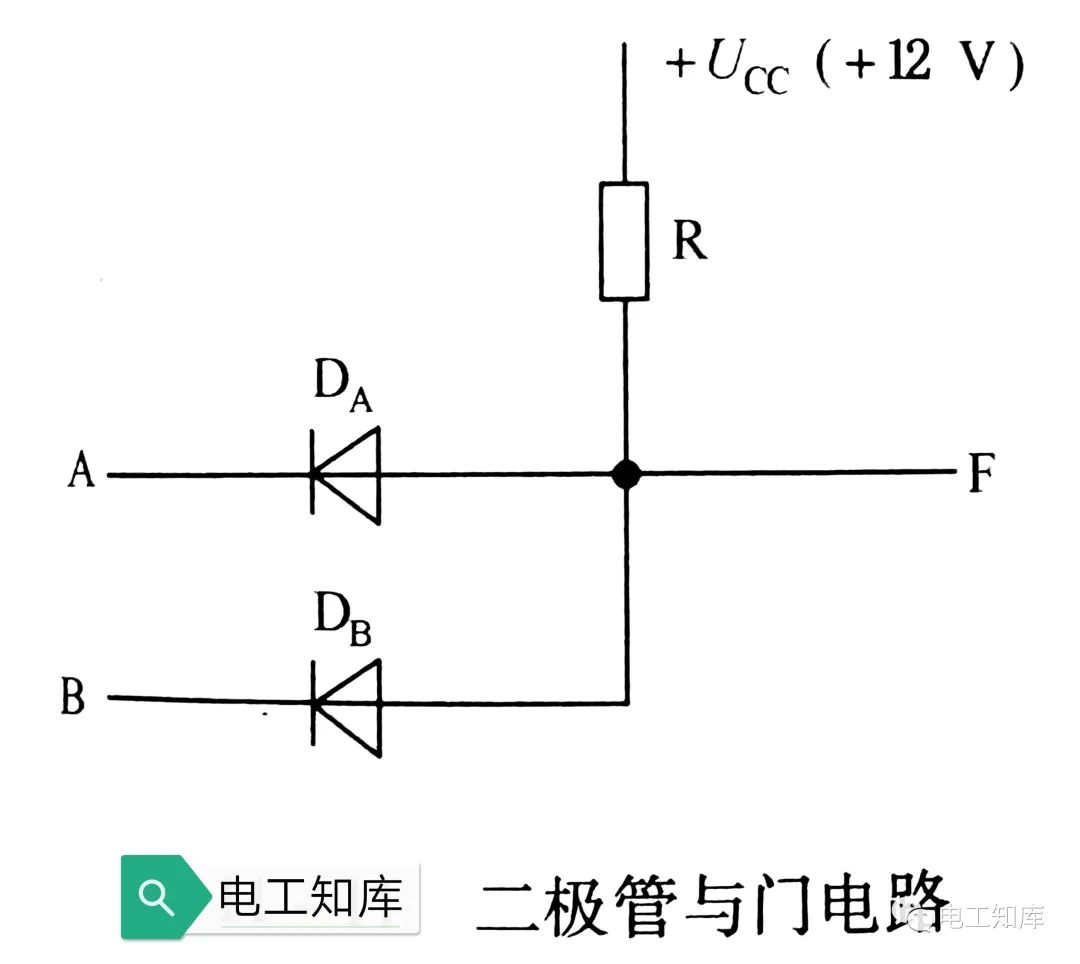

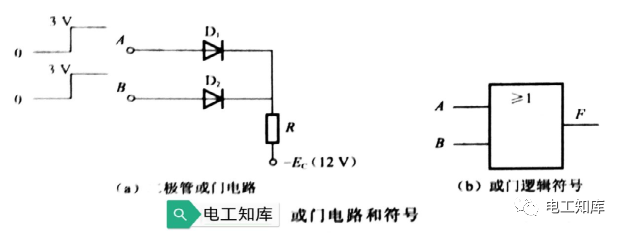

二極管邏輯

今天已經很難看到二極管邏輯電路了,其實用性也不算高,不過因為電路簡單,非常適合用來理解基本概念。

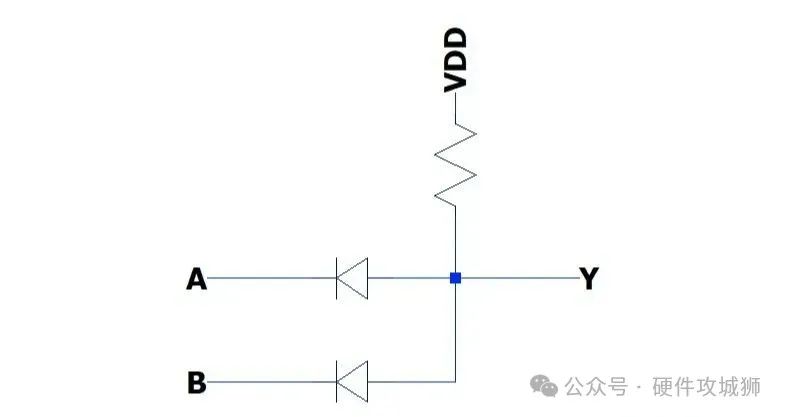

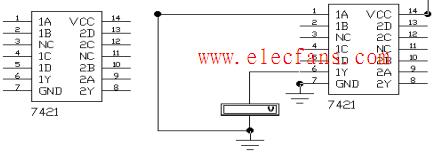

一個最簡單的二極管與門如下圖。與門實現邏輯與操作Y=A&B,即A或者B任意為L的時候,輸出Y為L,只有當A和B都為H時,Y才為H。

上圖,基本二極管與門

假設二極管無導通壓降,在這個電路中,二極管充當了單向開關的角色,當A和B等于VDD時,兩根二極管反向截至,Y被電阻上拉到VDD,這是Y就是H;當A或者B任意一端為GND時,二極管導通,因為二極管導通時電阻很小,遠小于上拉電阻,所以Y被拉到了GND,即邏輯L。

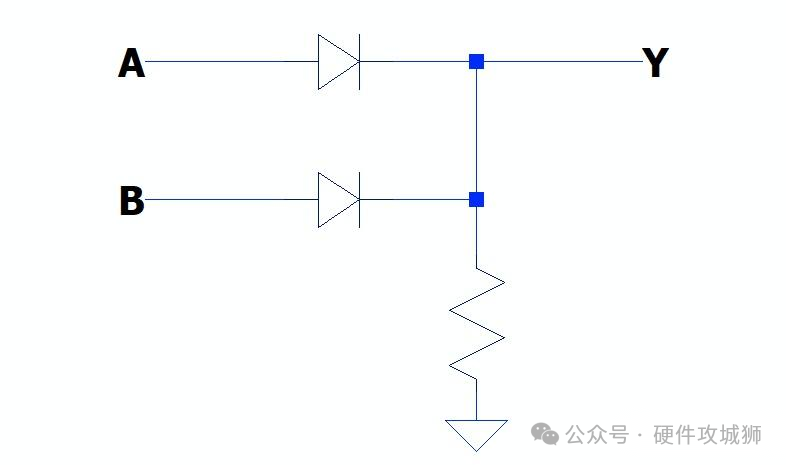

至于二極管或門,只要把二極管轉一下,再把電阻從拉到VDD改成拉到GND就可以了,非常簡單。

上圖,基本二極管或門

基本原理

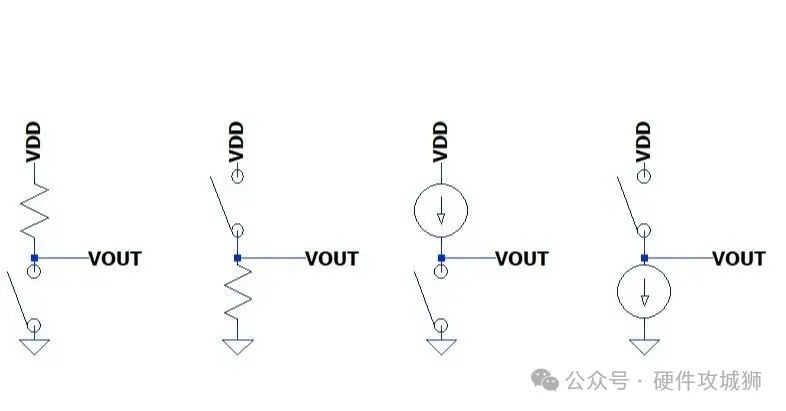

你看,在這么原始的邏輯電路中就已經出現了上下拉電阻,這里面的原理也非常簡單粗暴:利用開關的閉合(電阻為0)和開啟(電阻無窮大)的特性,配合電阻,就可以輕松實現兩種電壓的輸出。這種電路還有一個變形,就是用恒流源取代電阻,一方面集成電路工藝,恒流源比電阻更容易獲得,另一方面恒流源的驅動能力也更好。根據開關和電阻(或恒流源)的相對位置,有以下基本電路:即開關接到GND(L)或開關接到VDD(H)。

上圖,幾種開關電路接法

這幾種電路都是由開關的閉合或開啟決定了VOUT是VDD還是GND。開關的相對位置不同,還決定了電路在某一狀態下的驅動能力:開關的導通電阻為0,可視為驅動力無窮大,可是電阻(或恒流源)的驅動能力呢,只有VDD/R(或者恒流I),這就導致了電路在輸出H或L的時候驅動能力不對稱(換一個說法,就是電路在輸出H或者L的時候,輸出阻抗不一樣)。

除了驅動能力的問題,這種單開關加電阻的模式還會帶來靜態功耗的問題,因為只要開關閉合,不管外部有沒有負載,都會消耗電流。

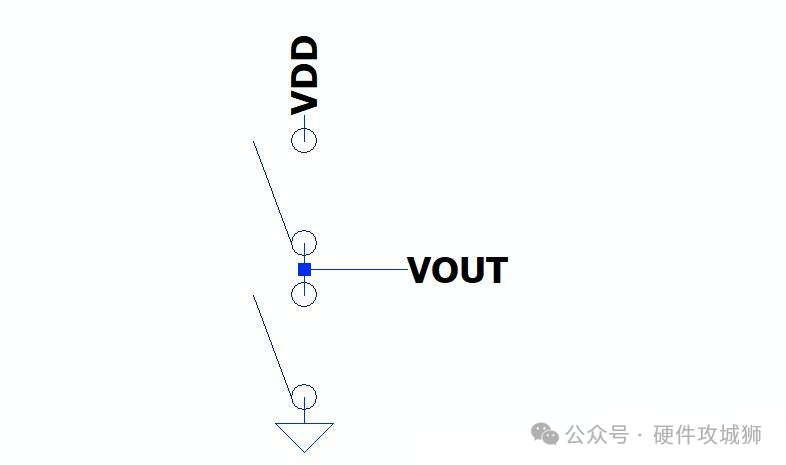

既然開關的驅動力比電阻強,那么能不能把電阻也換成開關?恭喜你,發現了現代CMOS邏輯電路的基本單元:倆互補的開關。這樣不管輸出H還是輸出L,驅動能力都是無窮大!好的,這時候上下拉電阻就不見了。

這樣兩個開關的電路還多出來了一種狀態:當兩個開關都開啟時,VOUT即不是VDD也不是GND,而是一個懸空的狀態(即高阻態,Hi-Z),這時候外部給什么信號它就是什么狀態。這樣又出現了一個新的邏輯門大類:三態邏輯門。

上圖,互補開關電路

很多經驗不是空穴來風,只是在流傳的過程中丟失了重要的前提條件。有一些邏輯器件,他們輸出高和輸出低時的驅動能力差別很大。

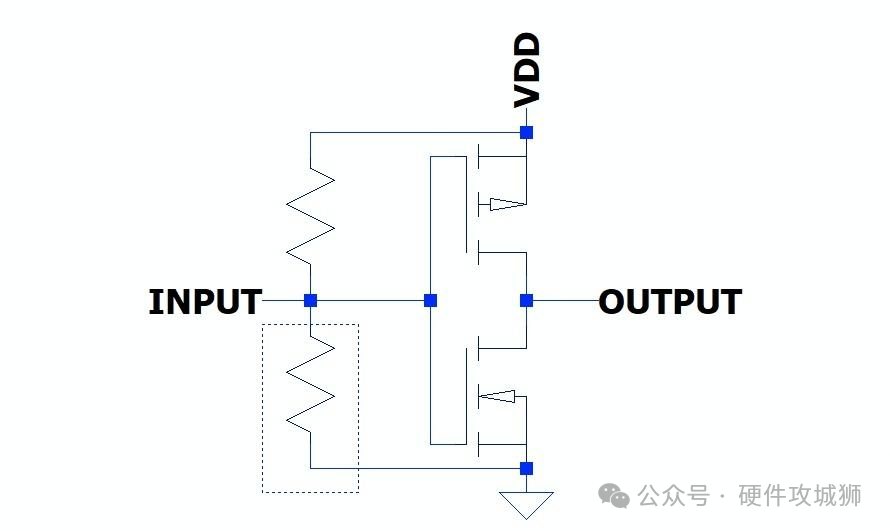

TTL(70xx、74Fxx、74Sxx、74LSxx等)家族的器件就屬于這種類型,如下圖是7404(TTL反相器)的原理圖,由于非對稱的輸出級設計,輸出為高時驅動能力只有0.4mA,而輸出低時居然能輸出16mA的電流(手冊中的輸出電流不是晶體管或者電路本身的極限,而是超過這個電流以后,輸出的電壓可能無法滿足邏輯族的要求)。

上圖,7404的簡化電路

這個時候在輸出端口外加一個上拉電阻,就可等效以增強端口在輸出H時的驅動能力,但代價是端口輸出L時,驅動能力相應地減弱,不過這時候芯片輸出能力足夠強,用這點代價來換取另一個狀態下驅動能力的增強,還是劃算。

上圖,帶上拉電阻的7404

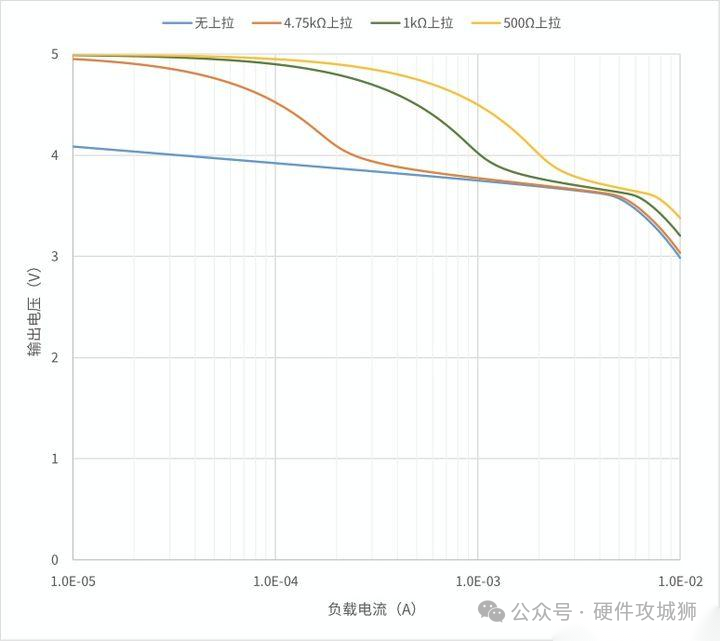

下表是仿真有無上拉電阻時,負載電流與輸出電壓的關系,可以看到上拉電阻確實增強了在一定負載下的輸出電壓,不過當負載電流較大時效果并不明顯,而且邊際效應也很顯著,當上拉電阻減小到一定程度以后,增強效果也不太顯著,而且會大大增加靜態功耗。

上表,帶不同上拉電阻的7404輸出電壓與負載電流的關系

既然非對稱的輸出級有這樣的問題,那為啥不能把這個驅動器設計成上下對稱的呢?

一方面,如果要設計成上下對稱的結構,上管需要用P管,而當時的工藝限制,P管各方面性能都不如N管,速度、功耗和成本都不是很劃算,所以能看到很多上年代的芯片,內部幾乎沒有P管(包括MOS工藝的器件也是)。

另一方面,TTL輸入結構的特點,輸入為H時所需電流很小,而輸入為L所需的輸入電流很大,這樣對輸出L時的驅動能力要求就很高,反而對輸出H時沒有驅動能力要求(TTL輸入懸空時等效為H)。

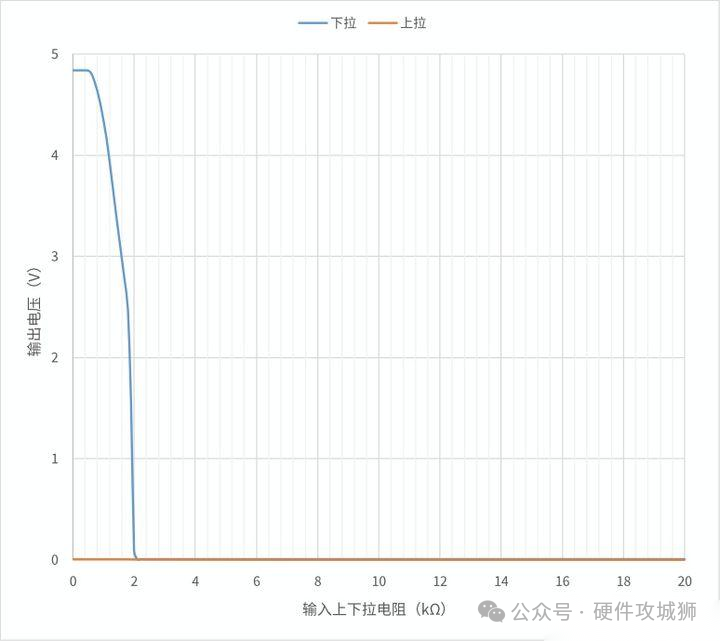

但TTL的這種特點,又會帶來一個比較麻煩的問題:下拉電阻值需要很大才能滿足要求,而下拉電阻太大則會導致輸出高時負載太重以至于無法達到規定電壓,所以TTL要盡量避免使用下拉。

下圖是仿真結果,因為這是一個反相器,所以下拉時輸出高是所期望的,而下拉電阻超過1.8kΩ時已經無法滿足TTL定義的最低高電平標準了;而上拉時,就算上拉電阻達到20kΩ,也絲毫不影響輸出。

上表,TTL上下拉電阻取值與輸出電壓的關系

CMOS電路

相信現在已經沒多少人會在設計時選用TTL家族的器件了,可能多數人都沒接觸過這類器件,最常用的還是CMOS家族(HC、HCT、LVC、CD4000等)。

CMOS家族的東西就比較簡單粗暴,上下對稱的結構,上下管驅動能力也基本一致,這個時候輸出的上下拉電阻對增強驅動能力幾乎沒有幫助不說,還加重了負載,屬于得不償失(其實多數情況下是無關痛癢)。

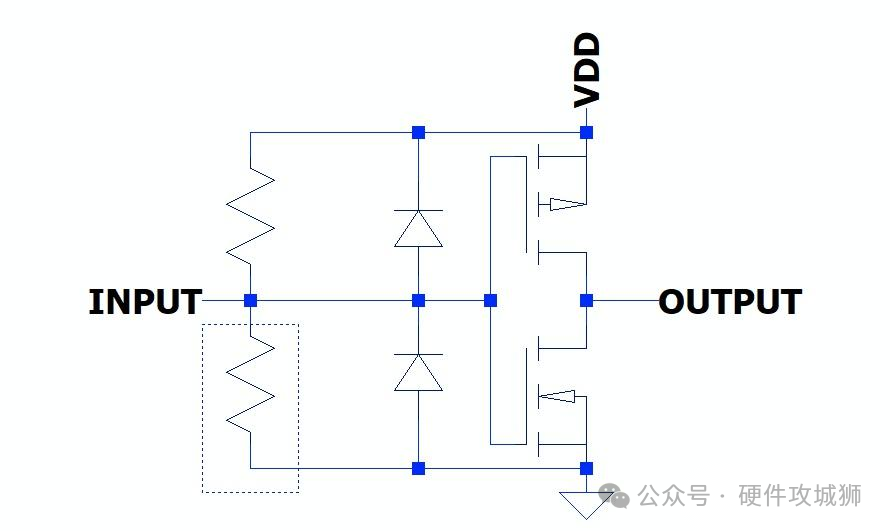

下圖是基本的CMOS反相器,只需要一對互補的MOS管即可實現(現實中的CMOS反相器一般是三對這種管子級聯出來的,為了提高開環增益)。

但是CMOS器件的輸入懸空時,不會被拉向任何一個方向,處于一種浮空的狀態,這樣會造成輸出紊亂,不是我們所希望的結果,這種情況下需要在輸入端接入上拉或者下拉電阻給電路提供一個確定的狀態。一般可拔插的對外接口(如JTAG)需要在I/O上加上上下拉電阻,有三態的總線視工作情況也可能需要上下拉,不過大多數的CMOS電路不需要額外的上下拉電阻。

上圖,CMOS器件在使用是一般要加上下來避免輸入懸空

因為CMOS輸入是電壓控制型,輸入阻抗很高,所以上下拉電阻的值可以很大,理論上用MΩ級別的電阻都沒問題。

不過理論歸理論,工程師得認清現實。現實的CMOS輸入結構,為了保護MOS管的柵極,會在柵極上加入ESD二極管,二極管反向偏置的時候是有漏電流的,還會隨溫度的升高還會指數增長!所以CMOS電路的上下拉電阻一般在100kΩ以下,一些制程比較先進的CPU,I/O口的漏電流或者上下拉電流較大,上下拉電阻一般取在幾kΩ級別。所以設計上下拉電阻前一定要仔細閱讀芯片手冊,查查I/O的輸入電流,看看取什么樣的電阻值才合理。

上圖,CMOS輸入有ESD二極管

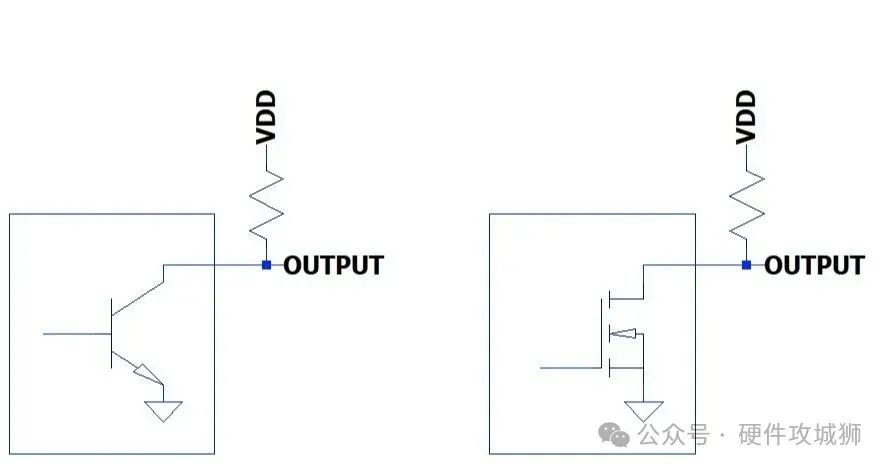

其他需要上下拉的情況

開集(Open-Collector)和開漏(Open-Drain)的輸出結構往往也需要加上拉電阻:理清推挽、開漏、OC、OD的特點與應用。OC和OD輸出結構只有下管,所以只能輸出L和高阻(Hi-Z)兩種狀態,而高阻態是難以被電路識別的,所以需要合適的上拉電阻把高阻態轉變為高態。

上圖,OC(左)和OD(右)輸出結構

雖然OC和OD輸出結構看起來很復古,使用時也需要外接電阻有點麻煩,但這種結構最大的好處就是可以做線與,也就是多個OC或者OD可以接到一起,只要其中一個輸出L,總線就是L,這在多外設中斷和電源時序控制方面很常用。

上圖,OC/OD的線與接法

I2C也是OC/OD結構,這樣很輕松就能在一條數據線上雙向傳輸數據而不需要額外的方向控制信號,而CAN總線則巧妙地利用線與特性來實現總線仲裁。

在處理OC或者OD電路的時候,一定要注意評估總線負載電容、上拉電阻與所需速度的關系,負載電容越大,速度越快,所需的上拉電阻要越小:通俗理解STM32中的上/下拉電阻。比如I2C總線,如果只掛載了一片從設備,使用4.75kΩ的上拉電阻可能就滿足400kHz的總線要求了,但如果掛了10片從設備呢,1kΩ的上拉電阻也不一定能搞定100kHz的總線速度,這種時候可能得考慮總線負載隔離或者降低總線速度了。

下圖是在200pF負載電容情況下,上拉電阻為500Ω、1kΩ、2kΩ、4.75kΩ和10kΩ下的波形,可以看到上拉電阻越大,對電容充電速度越慢,所以上升沿也越慢,當上拉電阻不合適時上升沿已經嚴重變形,無法保證正常工作。

上圖,OC電路不同上拉電阻對波形的影響

邏輯反相器可以當成放大器來用!不是開玩笑,我還真見過產品上用這種騷操作的,只需要把反相器接成反向放大器就可以了,不過邏輯器件當線性器件用,性能嘛...

上圖,邏輯反相器(非門)當成線性放大器用

單片機I/O口驅動,為什么一般都選用三極管而不是MOS管?

這里其實有兩個問題:

1.單片機為什么不直接驅動負載?

2.單片機為什么一般選用三極管而不是MOS管?

圖1

答:

1.單片機的IO口,有一定的帶負載能力。但電流很小,驅動能力有限,一般在10-20mA以內。所以一般不采用單片機直接驅動負載這種方式。

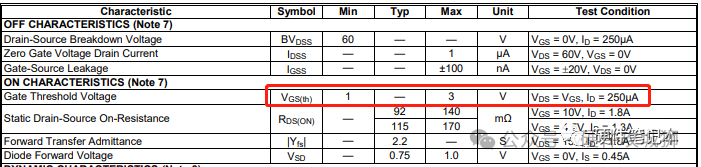

2.至于單片機為什么一般選用三極管而不是MOS管?需要了解三極管和MOS管的區別,如下:

①三極管是電流控制型,三極管基極驅動電壓只要高于Ube(一般是0.7V)就能導通。

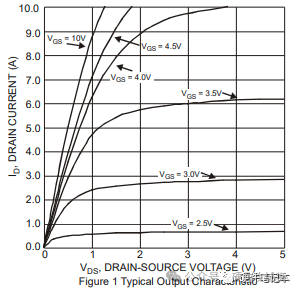

②MOS管是電壓控制型,驅動電壓必須高于閾值電壓Vgs(TH)才能正常導通,不同MOS管的閾值電壓是不一樣的,一般為3-5V左右,飽和驅動電壓可在6-8V。

我們再來看實際應用:

處理器一般講究低功耗,供電電壓也越來越低,一般單片機供電為3.3V,所以它的I/O最高電壓也就是3.3V。

①直接驅動三極管

3.3V電壓肯定是大于Ube的,所以直接在基極串聯一個合適的電阻,讓三極管工作在飽和區就可以了。Ib=(VO-0.7V)/R2。

圖2 驅動三極管示意圖

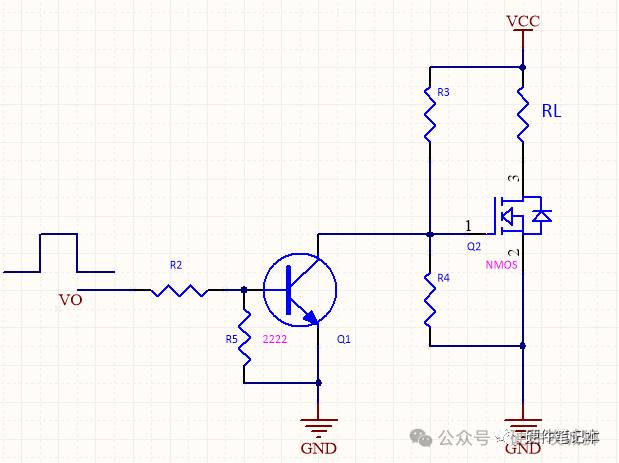

②驅動MOS管

通過前面也了解到,MOS管的飽和電壓>3.3V,如果用3.3V來驅動的話,很可能MOS管根本就打不開,或者處于半導通狀態。

在半導通狀態下,管子的內阻很大,驅動小電流負載可以這么用。但是大電流負載就不行了,內阻大,管子的功耗大,MOS管很容易就燒壞了。

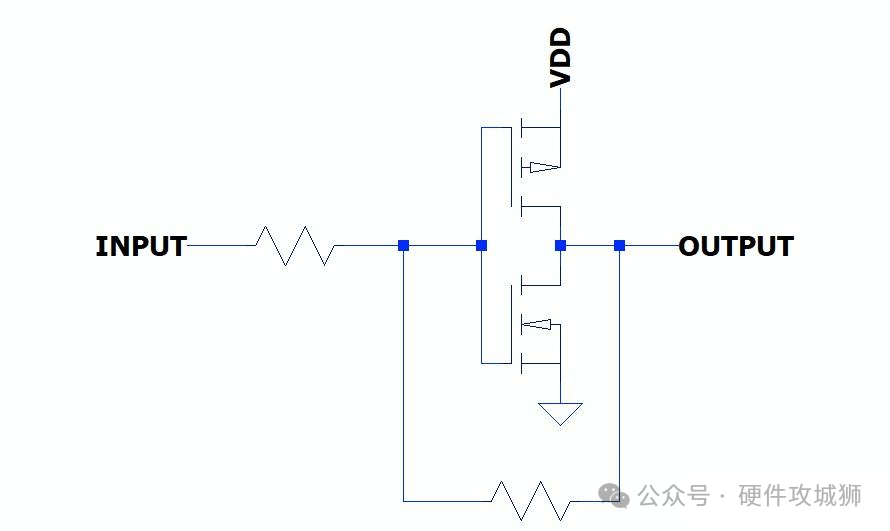

所以,一般選擇I/O口直接控制三極管,然后再控制MOS管。

圖3 I/O口驅動三極管后再驅動MOS管

當I/O為高電平時,三極管導通,MOS管柵極被拉低,負載RL不工作。

當I/O為低電平時,三極管不導通,MOS管通過電阻R3,R4分壓,為柵極提供合適的閾值電壓,MOS管導通,負載RL正常工作。

為什么要這樣操作呢?一定要用三極管來驅動MOS管嗎?

那是因為三極管帶負載的能力沒有MOS管強,當負載電流有要求時,必須要用MOS管來驅動。

那可以用I/O口直接驅動MOS管嗎?答案是可以的,但這種型號不好找,這里給大家推薦一個NMOS型號:DMN6140L-13(因為用的少,目前就知道這個型號)。

圖4 DMN6140L-13閾值電壓

這個管子的閾值電壓是1V,3.3V的時候可以完全導通,導通時的最大電流大約2.3A的樣子。

圖5 DMN6140L-13導通電流

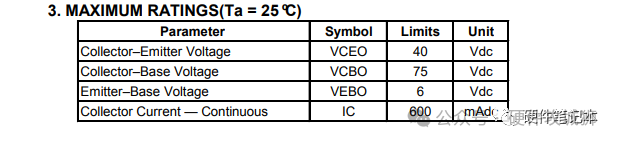

我們再來看看,常用的NPN三極管LMBT2222ALT1G的帶載能力,最大電流IC=600mA。

圖6 LMBT2222ALT1G導通電

可見MOS管的驅動能力是三極管4倍,所以對負載電流有要求的都使用MOS管。

那他們的價格相差多少呢?在立創上搜了一下,MOS管的三極管的價格幾乎是三極管的6倍

所以,在要求不高,成本低的應用場合,一般使用三極管作為開關管。

驅動波形實例調試

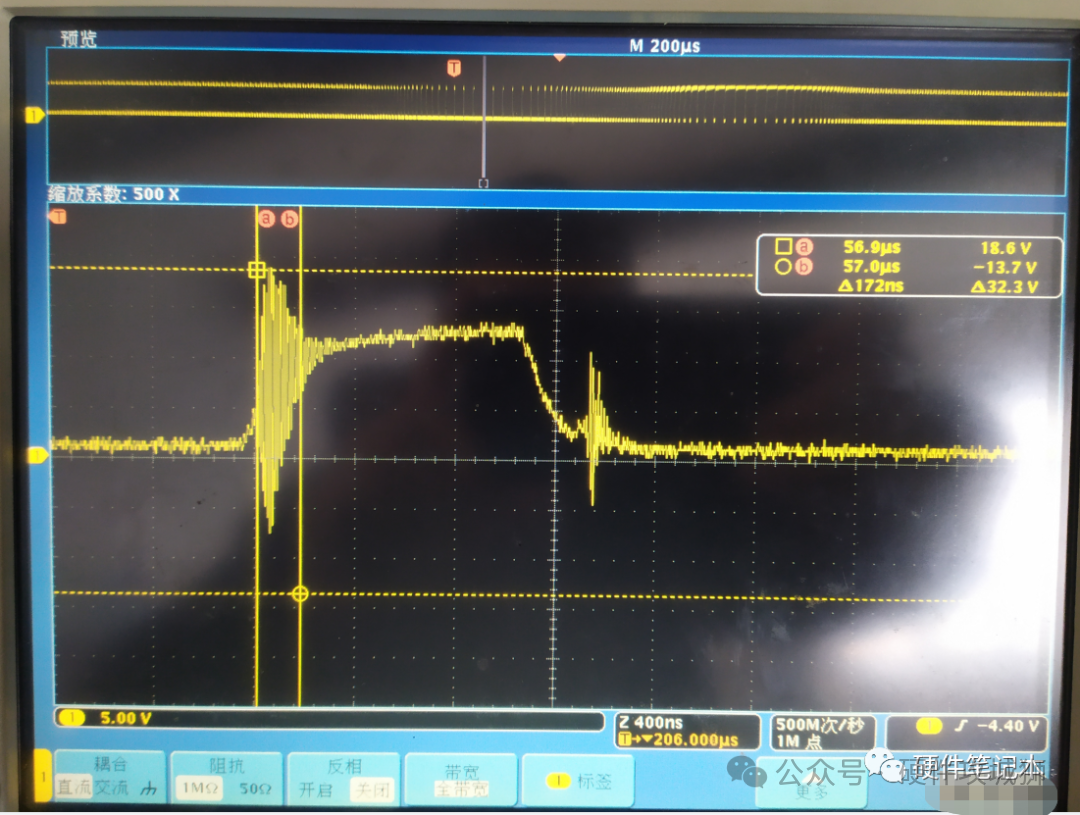

首先,供電正常,確保沒有虛焊或短路。但當我測試Vgs波形的時候,有點不敢相信自己的眼睛,如下圖。一般來說,MOS管驅動波形出現振蕩是很正常的現象,但是振蕩的這么厲害,波形根本沒法看,不能正常工作。

圖二 樣板驅動波形

用紅外測試儀監測了MOS管溫度,溫升瞬間升到幾十度,還好我反應快,馬上就斷掉了開關,不然辦公室又得開始放鞭炮了。

三、原因查找:

我猜想會不會是驅動芯片本身有問題?

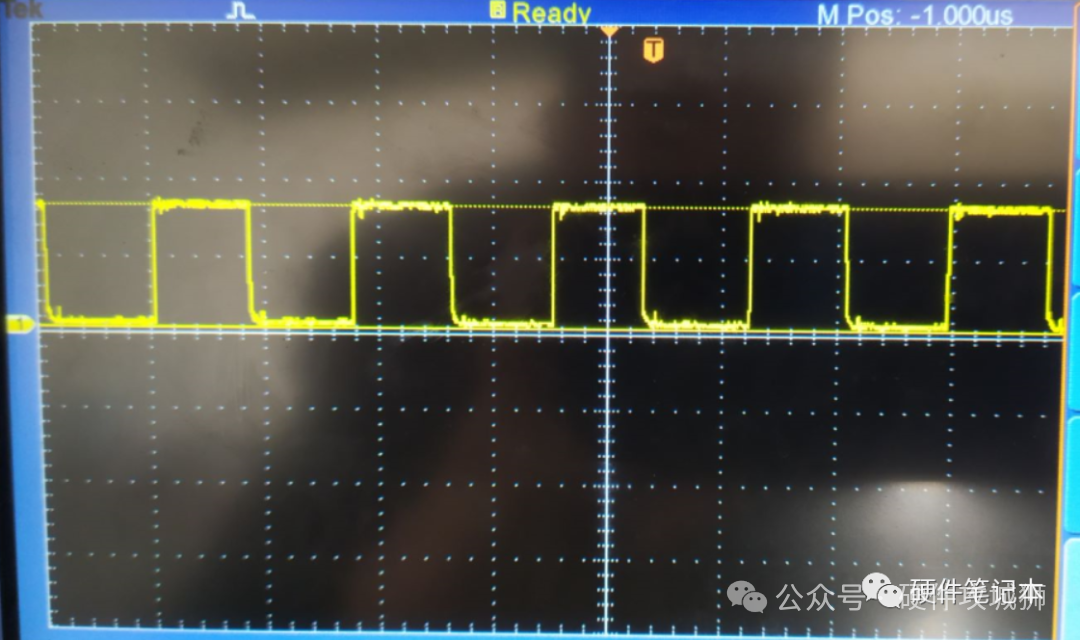

于是我用示波器直接測了驅動芯片的輸出波形,如下圖,波形正常。

圖三 驅動芯片輸出波形

那問題會不會出在驅動布板上,仔細查看了驅動部分的PCB,MOS管的回路盡量短,也都進行了包地處理,跟之前布板差別不大,所以排除PCB布板的問題。

于是我又嘗試調整了驅動電阻的阻值,因為這個電阻的大小對管子的振蕩影響很大。多測調試無果。

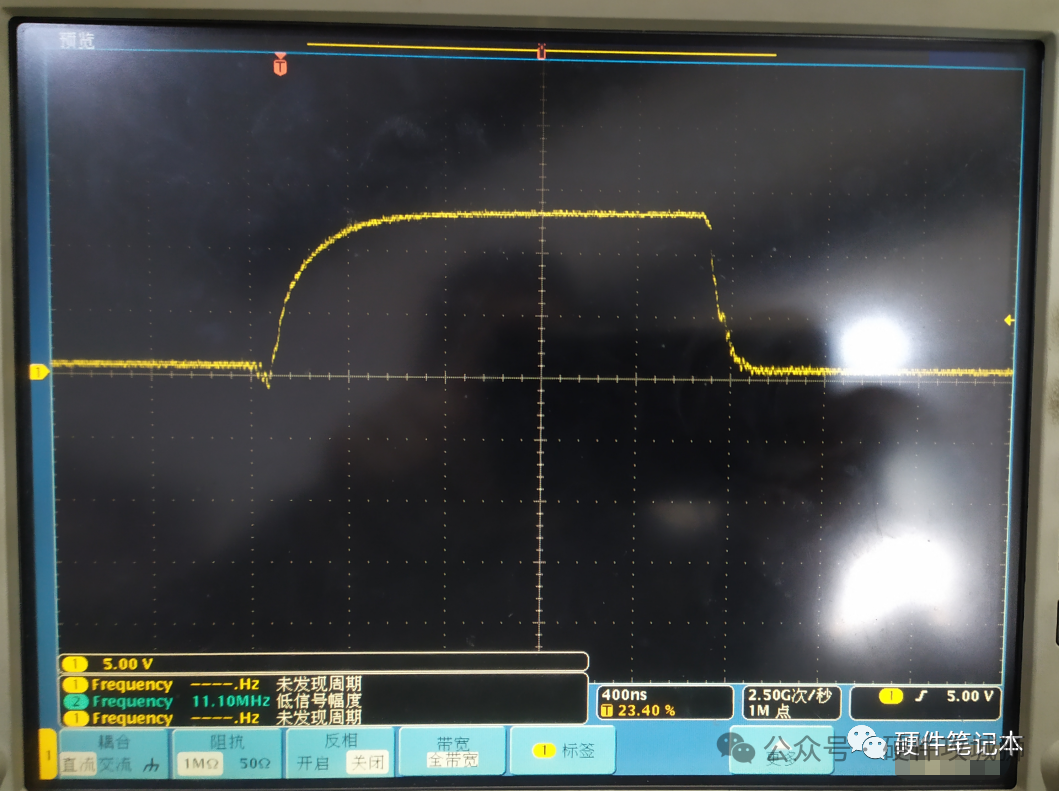

那唯一的不同之處在于驅動部分單獨做成一個小板插在主板上。我判斷大概率問題出在這里,于是重新打板將驅動直接畫在主板上。事實證明我的判斷是正確的,測得驅動波形如下圖,波形很漂亮,有木有?

圖四 PCB更改后樣板驅動波形

四、原因分析:

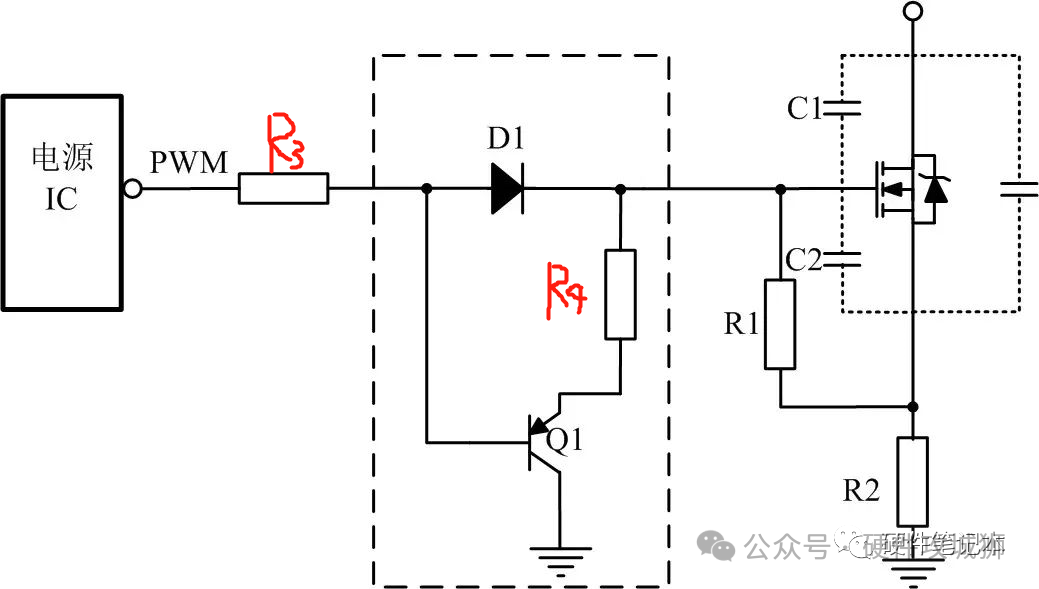

先簡單介紹一下我們所使用的驅動電路。如下所示。該電路一直量產至少上萬片,所以這個電路肯定是沒問題的。

當驅動PWM為高時,通過R3→D1→C2→R2→GND,給MOS管充電。

當驅動PWM為低時,通過C2→R4→Q1→GND,MOS管放電。

管子做到快開慢關。一般電阻R3小于R4,阻值為幾歐姆。

R1的作用是防止靜電擊穿,為靜電提供釋放回路,一般為10K左右。

圖五 驅動電路圖

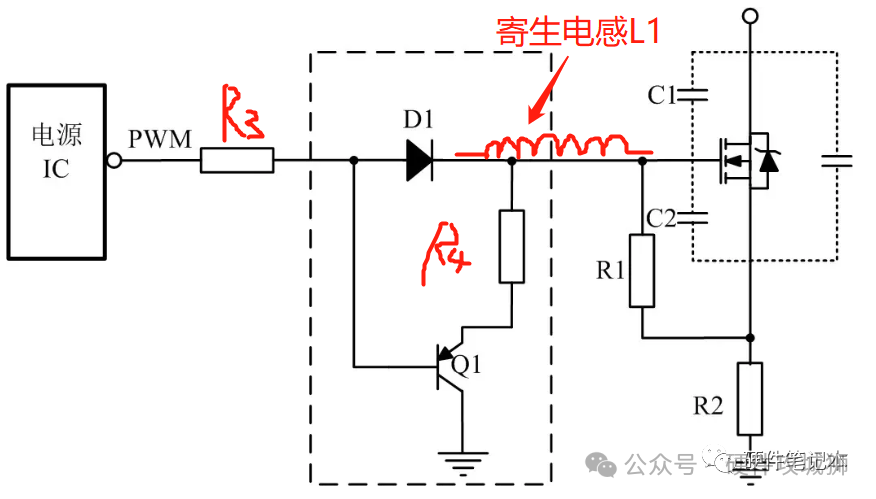

再回到我們的問題上,為什么將驅動插在小板上,驅動波形會變差,會振蕩的那么厲害呢?

實際上這個振蕩是由R3,L1和C2串聯振蕩引起的。其中,L1是驅動芯片輸出到柵極之間的寄生電感,這個距離越遠,L1越大。驅動做成小板通過插針的形式連接,其實就是增大了這個距離,也就是增大了電感L1,所以就振蕩的特別厲害。

電阻R3的作用主要起到阻尼振蕩的作用,讓管子導通的不那么快,吸收管子的振蕩尖峰。阻值越大,振蕩越小,但效率也會降低。

圖六 驅動電路中的寄生電感

最后,驅動電路部分一定要注意的幾個細節:

1.布局時,驅動部分一定要靠近MOS管且MOS管的驅動回路面積要盡量短,減小寄生電感的影響。

2.MOS管選型時,輸入電容C2和密勒電容C1盡量選擇容值比較小的。

3.調試時,可通過改變R3的阻值來改變驅動波形的振蕩。

-

二極管

+關注

關注

148文章

10102瀏覽量

171764 -

TTL

+關注

關注

7文章

540瀏覽量

71941 -

晶體管

+關注

關注

77文章

10020瀏覽量

141798 -

邏輯門電路

+關注

關注

2文章

68瀏覽量

12267

原文標題:驅動電路、驅動能力詳解

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

NMOS邏輯門電路工作原理

CMOS邏輯門電路

邏輯門電路的類別和性能參數

邏輯門電路的類別和性能參數

評論