PCIe 復位簡介

PCI Express 是一種即插即用協(xié)議,主機在啟動時將枚舉 PCIe 設(shè)備。此過程包括主機從讀取請求中獲得每個設(shè)備的地址大小,然后為設(shè)備分配基地址。因此,PCIe 接口必須在主機查詢時準備就緒,否則將不會分配基地址。PCI Express 規(guī)范規(guī)定,PERST# 必須在系統(tǒng)電源正常后 100 毫秒內(nèi)解除,并且 PCI Express 端口必須在 PERST# 解除后不超過 20 毫秒內(nèi)準備好進行 Link training。這通常稱為 100 毫秒啟動時間要求。

對 CIPS 進行配置

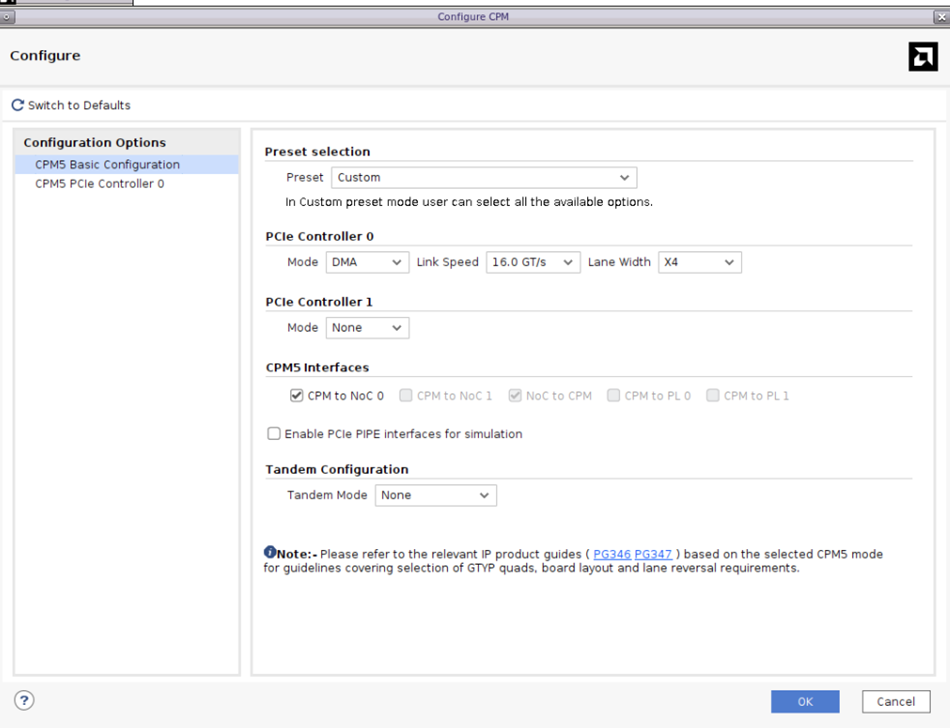

首先進入 CIPS 的 CPM 界面,選擇所需要的 PCIe 配置,如圖 1 所示,本設(shè)計的采用的是 gen4x4(Link speed 和 Lane Width 用戶可根據(jù)自己的需求進行配置),Mode 必須要選擇 DMA 模式。

圖 1

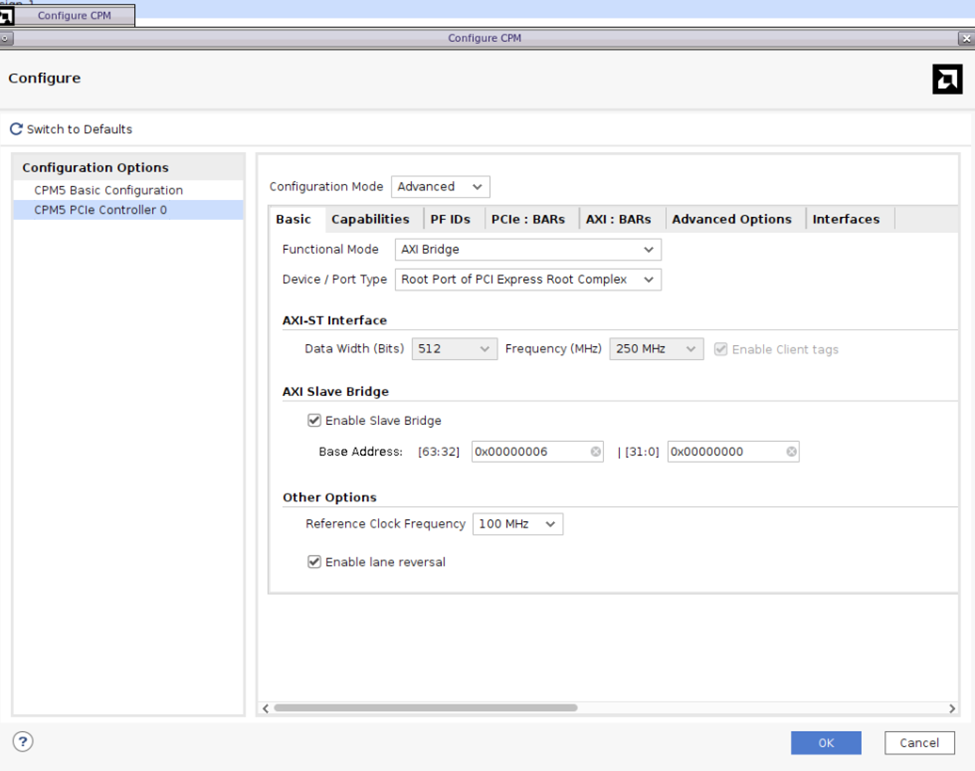

然后點擊 CPM5 PCIe Controller 0,在 Basic 界面,如圖2所示,將 Function mode 選擇為 AXI bridge。 Device/ Port Type 選擇為 Root Port of PCE Express Root Complex,其他界面可以應用默認配置。

圖 2

接下來需要對 PS PMC 進行配置,其他的配置頁面不進行過多描述,詳細可以參考 CPM RP 的 Example design,本篇文章主要對 IO 界面的配置進行描述。因為在 PCIe 做 RP 時,需要控制與其連接的 EP,對于不同的系統(tǒng)架構(gòu)難以設(shè)計出一個普遍可行的方案,故 RP 的驅(qū)動在目前的版本并未對復位進行操作,PS PR 的驅(qū)動可在下面鏈接中獲取:

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/85983409/Xilinx+PCIe+Root+and+EndPoint

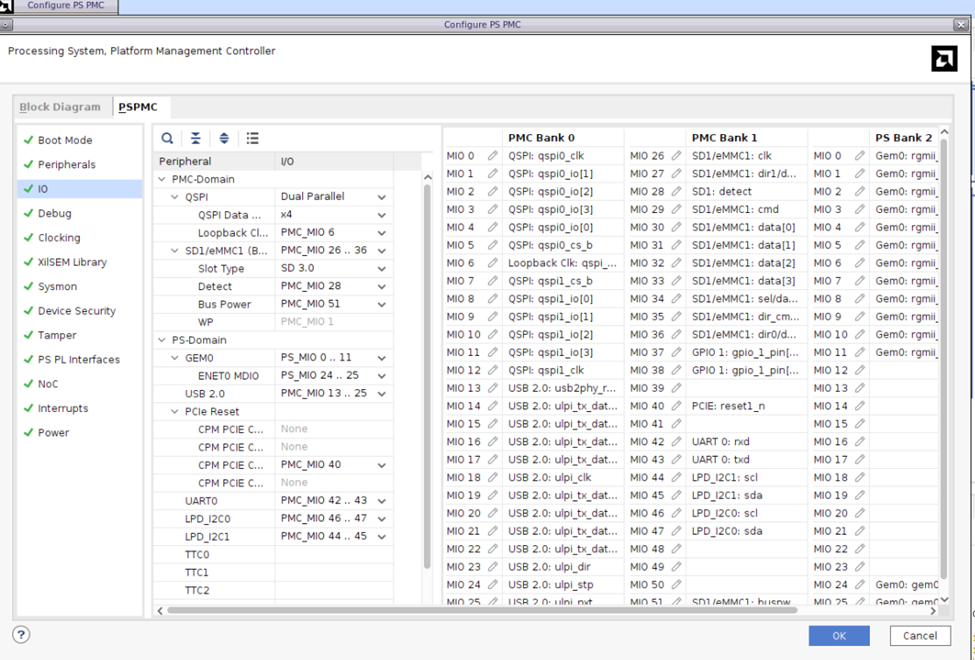

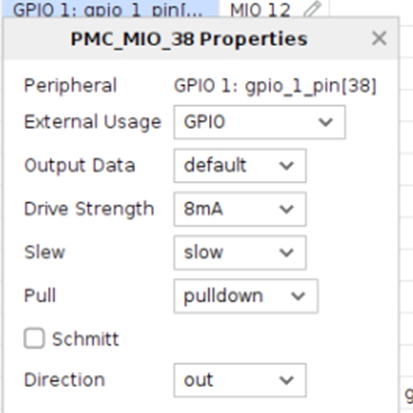

本篇文章通過舉例來說明,用戶如何根據(jù)自己的硬件電路設(shè)計來實現(xiàn)對 EP 端復位的控制,如下圖 3 所示,MIO38 為 PCB 板上金手指 Perst 所連的 Pin 腳,此時在 PS PCM 頁面中不要將此管腳配置成 PCIe reset 管腳,而是需要將此管腳按照下圖 4 配置為 GPIO 管腳。GPIO 管腳的配置如圖 4 所示,Direction 配置為 Out,并設(shè)置為 PULL DOWN。

圖 3

圖 4

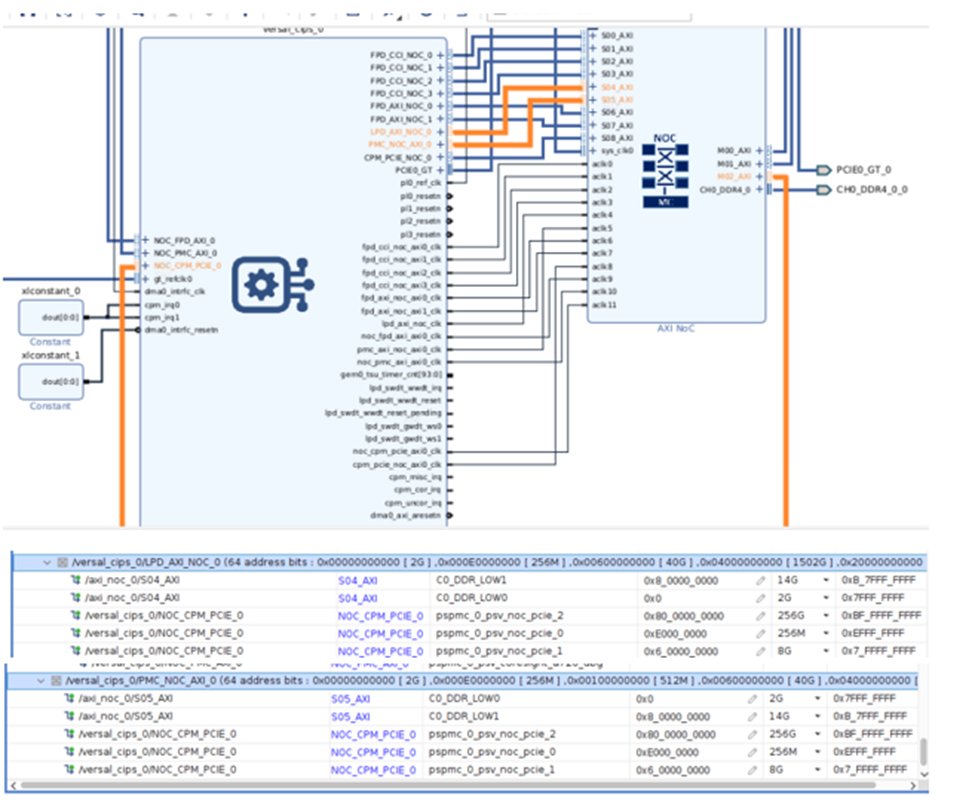

除了 CIPS 的配置需要注意之外,LPD_AXI_NOC_0 和 PMC_NOC_AXI_0兩個接口需要連通到 NOC_CPM_PCIE_0,如果 LPD_AXI_NOC_0 和 PMC_NOC_AXI_0 這兩個接口沒有連通到 NOC_CPM_PCIE_0,那么此時 CPU 對 PCIE 的鏈路情況無感知,其會在 Petalinux 中打印 PCIe link down,即使用戶根據(jù)本篇文章對復位進行了配置,在 PCIe debugger 中看到 LTSSM 已進入 L0,并且 PCIe 的 Link up 信號已拉高,因為 CPU 與 PCIE 之間的鏈路沒有打通,CPU 無法感知到 PCIE 的狀態(tài)依然會顯示 PCIe Link down。

圖 5

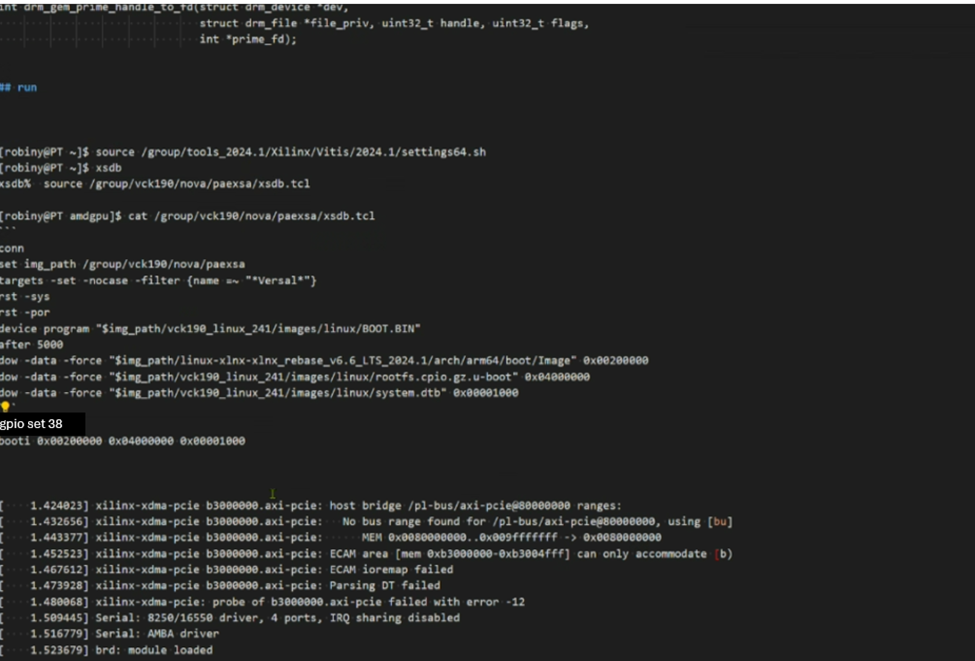

在 Load Petalinux 的 Image 之前,需要運行指令 gpio set 38,如下圖 6 所示,這個指令是將 PCIe 的復位拉高,因為在 CIPS 中,是將復位 MIO38 配置成 Pull down,在此狀態(tài)下 PCIe 處于復位狀態(tài),所以在 Load image 前需要將復位拉高,使得雙端進入 Link training 狀態(tài),在運行 Petalinux 時,會顯示 PCIe link up,接下來會完成 PCIE 的整個枚舉流程。

圖 6

-

接口

+關(guān)注

關(guān)注

33文章

8961瀏覽量

153295 -

PCIe

+關(guān)注

關(guān)注

16文章

1328瀏覽量

84761 -

CPM

+關(guān)注

關(guān)注

0文章

13瀏覽量

7862 -

復位信號

+關(guān)注

關(guān)注

0文章

67瀏覽量

6546

原文標題:開發(fā)者分享|CPM PCIE 做 RC 時如何完成對復位信號的控制

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

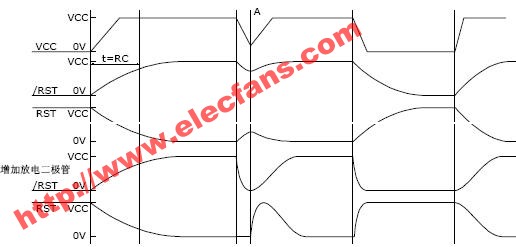

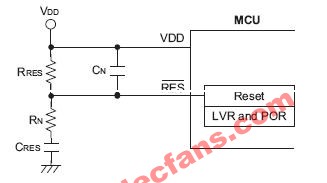

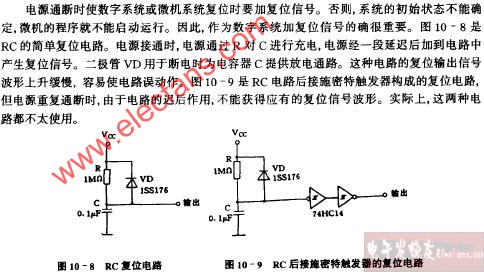

rc復位電路的電阻作用

請教幾個問題關(guān)于dm8168 的pcie做rc模式怎么設(shè)置?

異步復位,同步釋放的方式,而且復位信號低電平有效

RC復位電路復位時間的計算

PCIe總線的信號介紹

PCIe總線的兩種復位方式

同步復位和異步復位的優(yōu)缺點和對比說明

Versal CPM AXI Bridge模式的地址轉(zhuǎn)換

RC復位電路中R如何影響芯片復位?

AMD Versal? Adaptive SoC CPM PCIE PIO EP設(shè)計CED示例

CPM PCIE做RC時如何完成對復位信號的控制

CPM PCIE做RC時如何完成對復位信號的控制

評論