前言

這個文章的題目有點騙眼球的感覺,其實是自己踩過大坑,很是痛恨這個電路,希望大家以后不要踩了。工程師要畫這個電路時,網上一搜,不經深入分析就拿來用,給項目埋了炸彈。

RS485自動收發電路

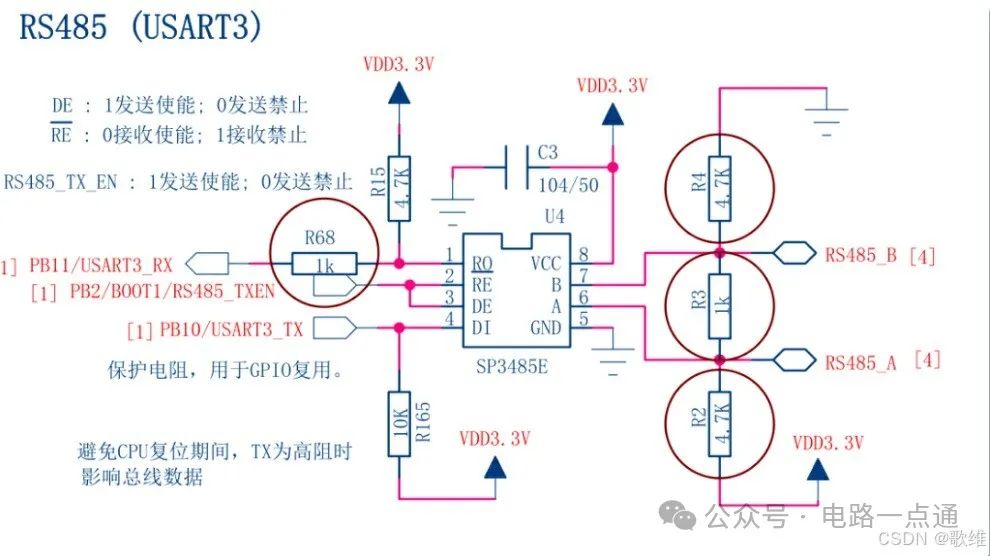

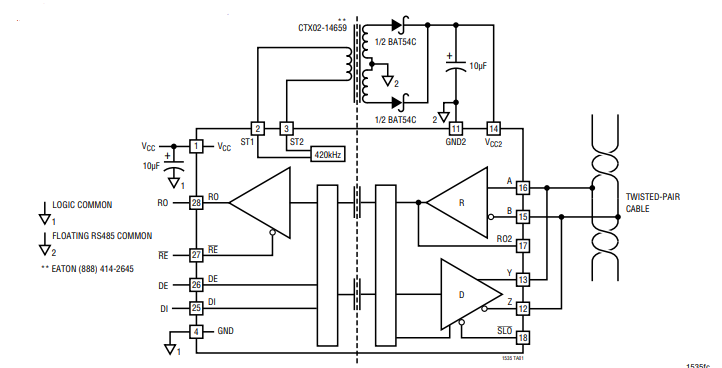

因為RS485采用叉分信號,只支持半雙工。正常的RS485芯片驅動電路是需要GPIO來切換發送和接收模式。如下圖所示,一般的RS485電平轉換芯片都有RE/DE腳,用來切換收發模式。

RS485標準電路參考

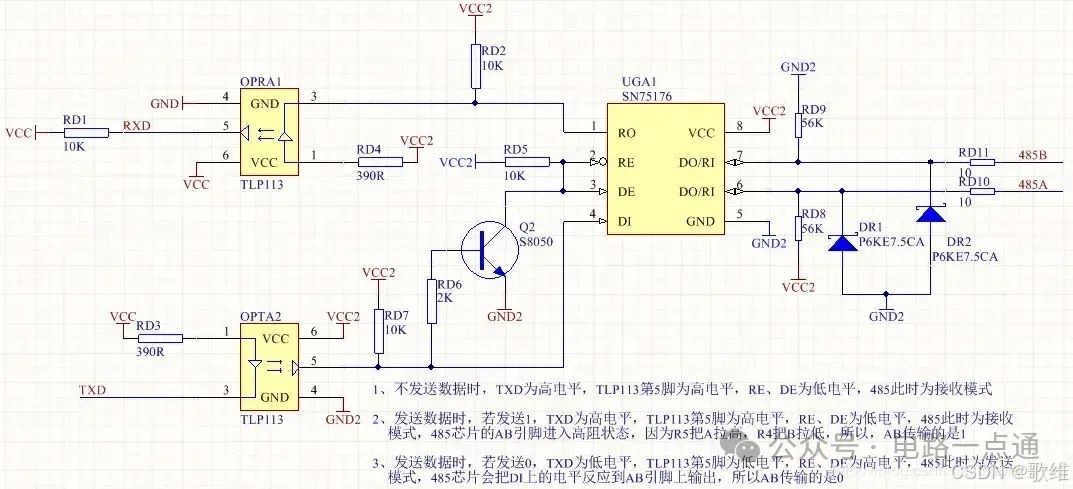

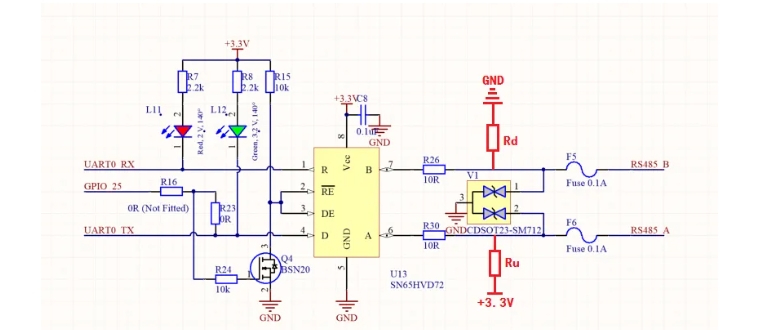

嵌入式行業,特別是MCU相關的都比較愛摳成本,便宜的MCU往往就是GPIO數量不夠。如果是上Linux系統的方案,一般串口支持RS485就還得改GPIO驅動,會有軟件工作量。于是有大聰明發明了自動切換的電路,省掉了那個GPIO。下圖是網上找的一個自動收發電路圖,收發原理直接看圖中文字描述。

1. 不發送數據時,接收模式,沒問題。

2. 發送數據0時,發送模式,輸出0,沒問題。

3. 發送數據1時,接收模式,外圍A,B由上下拉電路控制,輸出1,問題出在這里。

RS485自動收發電路

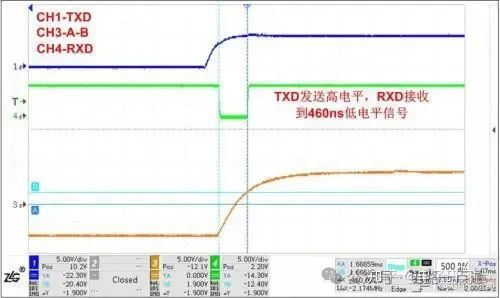

由于自己示波器測量的圖片丟失,網上找別的測試圖來說明,引用文章鏈接:

https://zhuanlan.zhihu.com/p/48018717

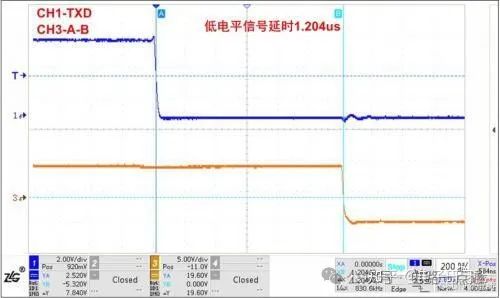

三極管的關斷時間較長(主要是由于三極管關斷時的存儲時間較長),因此若TXD發送低電平,DE&RE引腳較長時間后才會升至高電平,才會切到發送模式,發送低電平的延時時間較長,如下圖所示為1.204 μs。

關斷延時

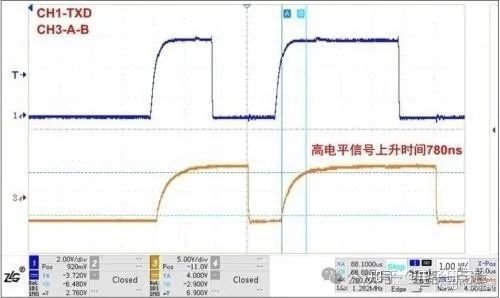

二是自動收發電路發送高電平是通過外部上下拉電阻驅動的,上升沿較緩慢,波形如下圖所示,可以看出,發送高電平的上升沿較為緩慢,限制了高速通信的應用。

上下拉驅動上升沿緩慢

RS485自動收發電路風險

如下圖所示,TXD變為高電平,DE&RE引腳降為低電平,AB差分電壓緩慢上升,由于此時RS-485收發器已經處于接收狀態,在AB差分電壓上升至RS-485收發器門限電平前RXD引腳會出現到一段時間的低電平信號,例如門限電平為-200mV~-50mV的收發器,AB差分電壓上升至-50mV前RS-485收發器均可輸出低電平,此低電平信號的時間與AB差分電壓上升時間和RS-485收發器的接收延時有關。由于串口一般是將每個位分成16份,檢測中間的3份的電平信號從而確定此位的信號高低,因此若此低電平信號保持至每個位的信號檢測時,則會使MCU接收到一個起始位,從而接收到錯誤的數據,因此這個問題同樣限制了高速通信的應用并且降低了通信的可靠性。

rxd接收到低電平

我們在實際應用中就是遇到這個問題,概率收到錯誤數據,導致丟包(數據校驗不通過而丟棄)。在研發的環境中,連接的終端設備少,距離近,這個丟包概率比較低,不容易發現。在Modbus應用中,概率丟包只會影響數值更新速度慢,影響不大。但是我們在現場做升級操作時,幾乎很難成功,因為在研發環境沒問題,我們優先排查現場環境信號干擾等問題,浪費了很多時間。這個電路有兩個缺點:

1. 通信速度慢:

三極管有電容效應,導致關斷時間較長,導致RE/DE從低到高電平變化出現比較大的斜坡.同時485輸出高電平,是依靠上下拉來完成的,會導致上升沿不夠迅速,因此上下拉的阻值選擇也是影響速度的關鍵。

2. 驅動能力弱:

由于當tx為高,485電平是由其上拉電阻完成的,因此弱提高驅動能力,就要減小電阻,由于485芯片驅動能力有限,電阻太小會導致tx為低的時候,485芯片無法將485總線拉低,因此總線上所有上拉電阻的并聯值不應該小于375歐。還用當接入120歐的終端電阻的時候,AB兩相的電壓差由終端電阻和上下拉分壓得到,會導致AB兩相的電壓差變小,因此自動收發串口轉RS485設計不太適合添加終端電阻。

終端電阻的問題

終端電阻主要是為了匹配通信線的特性阻抗,防止信號反射,提高信號質量。在組建RS-485總線網絡時,通常使用特性阻抗為120Ω的屏蔽雙絞線,由于RS-485收發器輸入阻抗一般較高(例如RSM485ECHT輸入阻抗為96kΩ,最多可連接256個節點),在信號傳輸到總線末端時會由于受到的瞬時阻抗發生突變(以RSM485ECHT為例,阻抗由120Ω變為96kΩ),導致信號發生反射,影響信號的質量。

實際上只有距離+高速率的環境需要添加終端電阻,例如長度>500米 + 波特率超過500kbps。

總結和建議

RS485總線和電路看似簡單,但是要看應用場景,對穩定性有要求的不建議使用自動收發驅動電路。

在沒有遇到信號反射問題時,盡量不要使用終端電阻;硬件設計時,可以預留外掛或焊接120Ω電阻的位置。

要查看RS485驅動芯片的輸入阻抗參數,和支持外掛設備數。上、下拉電阻與收發器輸入阻抗的并聯值應大于375Ω;

如果是現場做工程項目,建議帶上萬用表和示波器,測一下空閑狀態下的電壓值,收發的信號質量,這樣才安心。

-

RS485

+關注

關注

39文章

1229瀏覽量

83822 -

收發電路

+關注

關注

0文章

23瀏覽量

2131

原文標題:踩坑又給項目埋雷,這RS485自動收發電路設計

文章出處:【微信號:zfdzszy,微信公眾號:張飛電子實戰營】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

LTC1535隔離型RS485收發器技術手冊

RS485接口電路設計全面指南:從基礎到實踐

如何構建RS485通信網絡 RS485串口助手的使用與配置

工業現場經常用到的 RS485 通信,原來它的收發機制是這樣的

RS485保護電路設計改進方案

【產品應用】RS485典型電路應用詳解

Rs485電路的限流電阻為什么都用ptc

踩坑又給項目埋雷,RS485自動收發電路設計

踩坑又給項目埋雷,RS485自動收發電路設計

評論