近日,北京大學集成電路學院賈天宇老師開設的《現(xiàn)代SoC處理器架構設計》如期進行,算能首席科學家楊柳西博士、處理器架構師張明俊受邀,為北大博士講授了RXU高性能通用處理器設計的課程。

《現(xiàn)代系統(tǒng) SoC 芯片設計》是涉及到多個異構硬件子系統(tǒng)的體系架構設計和集成的系統(tǒng)性工程,該課程圍繞現(xiàn)代 SoC 芯片的體系架構和微架構實現(xiàn)技術,特別是高性能通用處理器、加速子系統(tǒng)、互聯(lián)等內容,著重強調專業(yè)與實踐結合,培養(yǎng)學生成為高素質的處理器設計師和計算機架構師。

理論與工業(yè)實踐并舉,聯(lián)合北大開設通用處理器課程

算能處理器架構師張明俊從指令流的角度出發(fā),介紹了分析指令流的一些基本概念,包括BasicBlock、控制流圖、數(shù)據(jù)依賴圖等,結合這些程序分析的基本數(shù)據(jù)結構,介紹了通用處理器流水線的一個發(fā)展歷史以及動態(tài)調度算法的發(fā)展歷史,包括經(jīng)典的:ScoreBoard算法、Tomasulo 算法、改進版Tomasulo 算法以及SMT 通用處理器的原理。

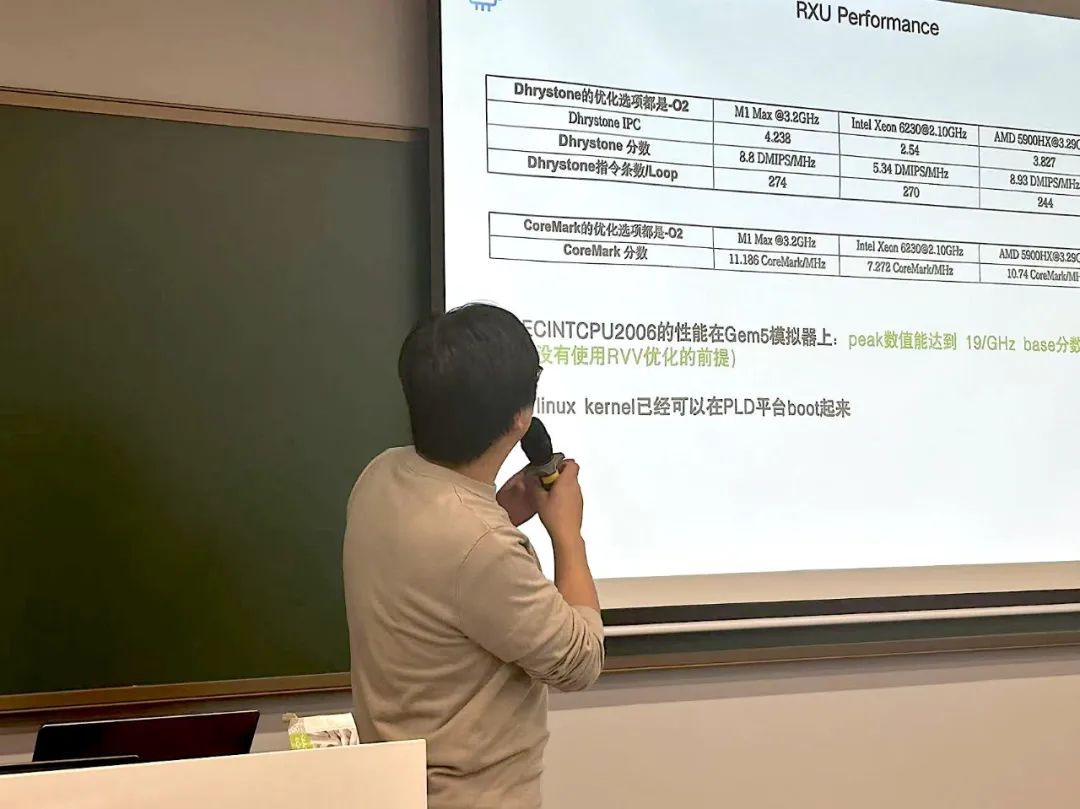

結合當前的高性能通用處理器的基本結構,課程還介紹了算能自研RXU通用處理器的相關知識,包括:前端子系統(tǒng)、中端子系統(tǒng)、后端子系統(tǒng)、訪存子系統(tǒng)、以及中斷&調試子系統(tǒng),并對其中的關鍵部件和算法做了詳細的介紹:BPU的Tage算法、Rename模塊、ROB模塊等。

楊柳西博士帶領大家深入探討了計算機起源和進化,以幾十年的工業(yè)實踐為引導,讓同學們充分認識到處理器設計的復雜性與挑戰(zhàn),尤其是在面對X86、ARM的激烈競爭時,RISC-V架構的機會在哪里,如何發(fā)揮出自己的優(yōu)勢。課程最后,他指出處理器設計的哲學猶如比爾·克林頓所說, “求其上者得其中,求其中者得其下,求其下者無所得”,鼓勵大家未來從事處理器設計工作后,一定要高標準、嚴要求,才能有創(chuàng)新和突破。

持續(xù)推動產學合作,為全球RISC-V生態(tài)蓄力

通過與北京大學的課程合作,算能將業(yè)界先進的處理器設計理念和方法論帶進高等學府,將引導更多青年才俊投身RISC-V高性能處理器設計領域,培養(yǎng)更多緊缺人才。

算能不僅為高校提供業(yè)界領先的處理器設計課程,也為學生們提供了豐富的企業(yè)實習機會,在校生既可以參與算能發(fā)布的相關研究課題,也可以直接上手,來到企業(yè)參與一線的開發(fā)工作。算能也將持續(xù)推動RISC-V的科研轉化和商用落地,培養(yǎng)出更多具備國際競爭力的高端處理器設計人才,為全球RISC-V的生態(tài)發(fā)展貢獻力量。

-

處理器

+關注

關注

68文章

19863瀏覽量

234373 -

芯片

+關注

關注

459文章

52383瀏覽量

439063 -

RISC-V

+關注

關注

46文章

2535瀏覽量

48550

發(fā)布評論請先 登錄

HPM5E31IGN單核 32 位 RISC-V 處理器

首款RISC-V架構服務器,助力行業(yè)精準適配AI場景

RISC-V MCU技術

Imagination放棄RISC-V處理器內核開發(fā)

Andes晶心科技推出D45-SE RISC-V處理器

RISC-V架構及MRS開發(fā)環(huán)境回顧

官宣!OpenWrt正式支持賽昉科技JH-7110 RISC-V應用處理器

Rivos全新產品采用Andes晶心科技NX45 RISC-V處理器

《RISC-V能否復制Linux 的成功?》

RISC-V,即將進入應用的爆發(fā)期

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態(tài)!

算能助力RISC-V技術探索,《微處理器與系統(tǒng)設計》課程圓滿結課

開源芯片系列講座第22期:異步電路機制為RISC-V處理器賦能

走進北大 | 算能RISC-V通用處理器設計成功開課

走進北大 | 算能RISC-V通用處理器設計成功開課

評論