原創(chuàng) 杜芹 半導體芯聞

最近一段時間以來,芯片巨頭英特爾在商業(yè)和市場層面經(jīng)歷了諸多挑戰(zhàn)。但有一說一,英特爾在前沿技術領域的探索和布局依然具有行業(yè)標桿意義,其發(fā)布的技術路線圖和成果為半導體行業(yè)提供了重要參考方向。

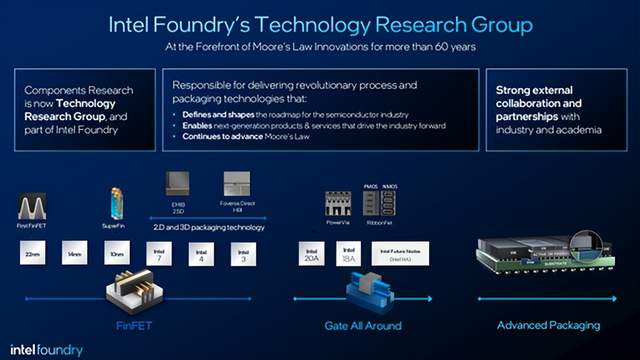

在IEDM 2024大會上,英特爾發(fā)布了7篇技術論文,展示了多個關鍵領域的創(chuàng)新進展。這些技術涵蓋了從FinFET到2.5D和3D封裝(EMIB、Foveros、Foveros Direct),即將在Intel 18A節(jié)點應用的PowerVia背面供電技術,以及全環(huán)繞柵極(GAA)晶體管RibbonFET等。此外,英特爾還揭示了一些面向未來的先進封裝技術,為推動行業(yè)發(fā)展提供了新的視角。

在這些前沿技術中,三個核心領域尤為值得關注:面向AI發(fā)展的先進封裝、晶體管微縮技術和互連微縮技術。在IEDM 2024大會上,英特爾代工高級副總裁兼技術研究總經(jīng)理Sanjay Natarajan詳細介紹了這些領域的關鍵突破。

先進封裝的突破:選擇性層轉移技術

異構集成已經(jīng)成為當今芯片界的主流實現(xiàn)性能提升的手段。但是異構集成技術面臨著很大的挑戰(zhàn)。當前異構集成技術主要采用“晶圓對晶圓鍵合”(Wafer-to-Wafer HB)或“芯片對晶圓鍵合”(Chip-to-Wafer HB),會因順序裝配芯粒而導致吞吐量、芯片尺寸和厚度受限。

英特爾通過選擇性層轉移(Selective Layer Transfer)技術,突破了當前異構集成的技術瓶頸。這項技術能夠以超高效率完成超過15,000個芯粒的并行轉移,僅需幾分鐘即可實現(xiàn)相較于傳統(tǒng)方法數(shù)小時或數(shù)天的提升。其創(chuàng)新性地實現(xiàn)了亞微米級芯粒的轉移,支持僅1平方毫米大小、厚度為人類頭發(fā)1/17的芯粒。這提供了一種靈活且成本效益顯著的異構集成架構,使得處理器與存儲器技術的混合搭配成為可能。Intel Foundry率先采用無機紅外激光脫鍵技術,實現(xiàn)了芯粒轉移的技術突破,推動了旗艦AI產品開發(fā)所需的先進異構集成技術的發(fā)展。

英特爾代工高級副總裁兼技術研究總經(jīng)理Sanjay Natarajan表示:“我們有理由期待這一技術能夠像PowerVia背面供電技術一樣在業(yè)內普及。我們將積極開創(chuàng)并推動這項技術的發(fā)展,我認為我們會看到業(yè)內領先企業(yè)都逐步采用這一技術。”

面向AI時代,英特爾提出了全面的封裝解決方案,以實現(xiàn)AI系統(tǒng)的大規(guī)模量產。除了選擇性層轉移技術,英特爾還聚焦于:

先進內存集成(memory integration):解決容量、帶寬和延遲瓶頸,提升性能。

混合鍵合(hybrid bodning)互連的間距縮放:實現(xiàn)異構組件間的高能效和高帶寬密度連接。

模塊化系統(tǒng)的擴展:通過連接解決方案降低網(wǎng)絡延遲和帶寬限制。

GAA晶體管的突破:物理和二維材料

晶體管技術的進步一直以來都是英特爾的主業(yè)之一,英特爾的目標是到2030年實現(xiàn)一萬億晶體管的宏偉目標。

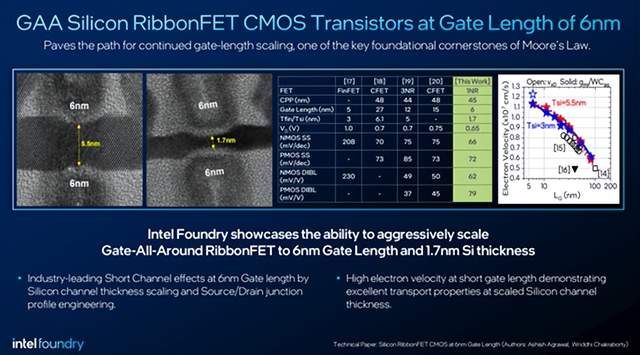

Intel展示了其在Gate-All-Around(GAA)RibbonFET晶體管上的技術突破,成功將柵極長度縮小至6nm,并實現(xiàn)1.7nm硅通道厚度。通過對硅通道厚度和源漏結的精準工程設計,有效減少了漏電流和器件退化,提高了晶體管在極短柵極長度下的性能穩(wěn)定性。英特爾研究數(shù)據(jù)顯示,與其他先進節(jié)點技術相比,在6nm柵極長度下,RibbonFET在短柵極長度下具備更高的電子遷移率和更優(yōu)的能效特性。除此之外,RibbonFET實現(xiàn)了最佳的亞閾值擺幅(Subthreshold Swing,SS)和漏電流抑制性能(DIBL)。

左圖是透射電子顯微鏡(TEM)圖像,中間展示看這些晶體管的部分關鍵參數(shù),右圖是柵極長度與電子速度關系圖

這一進展展示了在短溝道效應優(yōu)化方面的行業(yè)領先水平,這為未來更高密度、更低功耗的芯片設計奠定了基礎,同時推動了摩爾定律的持續(xù)發(fā)展,滿足了下一代計算和AI應用對半導體性能的嚴苛需求。

為了推進GAA晶體管技術的發(fā)展,英特爾也將目光瞄準了二維半導體材料。

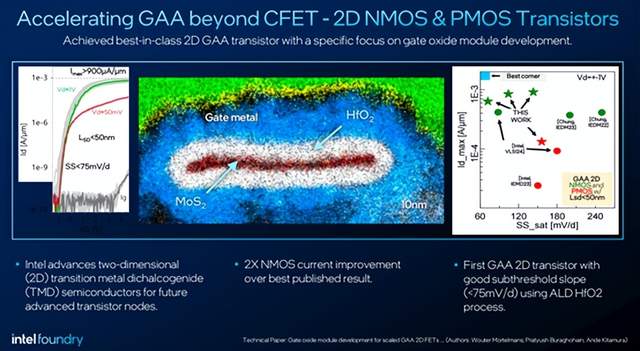

據(jù)Sanjay Natarajan的介紹,具體而言,英特爾在GAA技術中引入了二維(2D)NMOS和PMOS晶體管,該晶體管以二維MoS2為溝道材料,結合高介電常數(shù)的HfO2作為柵氧化層,通過ALD(原子層沉積)工藝實現(xiàn)精確控制。下圖的橫截面成像清晰展示了柵極金屬、HfO?氧化物和二維MoS2之間的結構集成,其整體厚度在納米級別,漏源間距(L_SD)小于50nm,次閾值擺幅(SS)低于75mV/d,最大電流性能(I_max)達到900μA/μm以上,能夠顯著提升柵極對溝道的控制能力。

右側的圖表中將Intel的研究結果(THIS WORK)與其他同類研究進行了對比,顯示在驅動電流和次閾值擺幅上的明顯優(yōu)勢。

英特爾的研究驗證了結合GAA架構和2D材料,晶體管性能堪稱飛躍。而且一旦英特爾將基于硅的溝道性能推至極限,采用2D材料的GAA晶體管很有可能會成為下一步發(fā)展的合理方向。

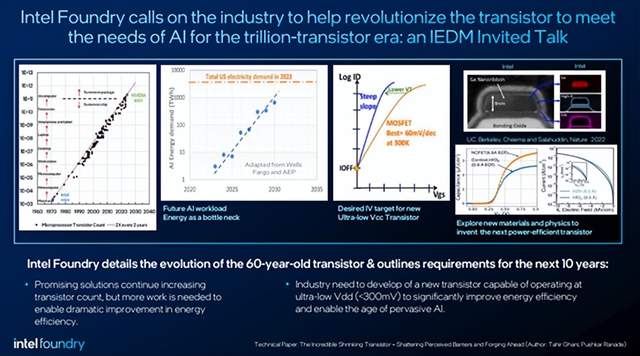

就英特爾所觀察到的而言,晶體管數(shù)量的指數(shù)級增長趨勢,符合摩爾定律,從微型計算機到數(shù)據(jù)中心,晶體管數(shù)量每兩年翻倍。但是,隨著AI工作負載的持續(xù)增加,AI相關能耗可能會在2035年超越美國當前的總電力需求,能源瓶頸成為未來計算發(fā)展的關鍵挑戰(zhàn)。因此,未來需要的是新型晶體管。下一代晶體管需要具備超陡次閾值擺幅(低于60mV/dec)和極低的靜態(tài)漏電流(I_off),支持在超低供電電壓(<300mV)下運行。

英特爾也在材料和物理層面不斷探索,并在IEDM上展示了采用Ge(鍺)納米帶結構的晶體管,其9nm厚度和結合氧化物界面的創(chuàng)新設計,為實現(xiàn)低功耗和高效傳輸?shù)於嘶A。Intel進一步研究結合高介電常數(shù)材料和新型界面工程,以開發(fā)更加節(jié)能高效的下一代晶體管。

英特爾也呼吁整個行業(yè)共同推動晶體管技術的革命,以滿足萬億晶體管時代中AI應用的需求。通過對過去60年晶體管發(fā)展的總結,Intel同時提出了未來10年的發(fā)展目標:1)必須開發(fā)能夠在超低供電電壓(<300mV)下工作的晶體管,以顯著提高能效,為普遍化的AI應用提供支持;2)持續(xù)增加晶體管數(shù)量的技術是可行的,但能源效率的革命性突破將是未來發(fā)展的重點。

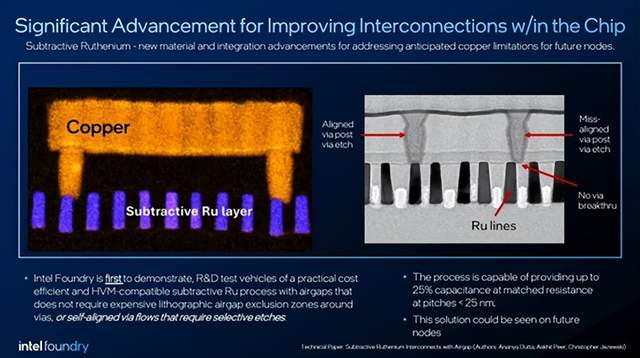

互連縮放的突破:釕線路

隨著晶體管和封裝技術的持續(xù)微縮,互連已成為半導體體系中的第三個關鍵要素。這些互連導線負責連接數(shù)以萬億計的晶體管。然而,我們清晰地看到,銅互連的時代正逐漸走向尾聲。銅互連存在一個實際問題:使用時需要添加阻擋層和籽晶層。隨著尺寸的不斷縮小,這些相對高電阻的層占據(jù)了更多的可用空間。英特爾觀察到,當線寬不斷縮小時,銅線的電阻率呈指數(shù)級上升,達到難以接受的程度。因此,盡管晶體管尺寸越來越小、密度和性能不斷提升,但傳統(tǒng)的布線方式已無法滿足連接所有晶體管的需求。

英特爾的突破在于采用具有高成本效益的空氣間隙釕(Ru)線路,作為銅互連的潛在替代方案。這個空氣間隙解決方案無需昂貴的光刻技術,也不需要自動對準通孔工藝。它巧妙地將空氣間隙、減法釕工藝和圖案化相結合,有望打造出合理的下一代互連技術,使之與未來的晶體管和封裝技術相匹配。

這種新工藝在小于25nm的間距下,實現(xiàn)了在匹配電阻條件下高達25%的電容降低,有效提升了信號傳輸速度并減少了功耗。高分辨率的顯微成像展示了釕互連線和通孔的精確對齊,驗證了沒有發(fā)生通孔突破或嚴重錯位的問題。減法釕工藝支持大規(guī)模生產(HVM),通過消除復雜的氣隙排除區(qū)和選擇性蝕刻需求,具備實際應用的經(jīng)濟性和可靠性。

寫在最后

半導體產業(yè)是一個高度復雜的生態(tài)系統(tǒng),需要各方共同努力才能取得突破。英特爾在封裝、晶體管和互聯(lián)等領域的創(chuàng)新成果,為整個行業(yè)提供了寶貴的經(jīng)驗和啟示。如同Sanjay Natarajan所述,英特爾的目標是為整個行業(yè)提供路線圖,以協(xié)調和統(tǒng)一我們所有的研發(fā)資金和努力。這樣,下一代產品和服務就能推動整個行業(yè)向前發(fā)展,并繼續(xù)推進摩爾定律。英特爾確實始終將自己視為摩爾定律的守護者,致力于承擔這一責任,不斷探索推進摩爾定律的新技術。這不僅是為了英特爾的利益,更是為了整個行業(yè)的共同利益。

聲明:本網(wǎng)站部分文章轉載自網(wǎng)絡,轉發(fā)僅為更大范圍傳播。 轉載文章版權歸原作者所有,如有異議,請聯(lián)系我們修改或刪除。聯(lián)系郵箱:viviz@actintl.com.hk, 電話:0755-25988573

審核編輯 黃宇

-

英特爾

+關注

關注

61文章

10135瀏覽量

173526 -

封裝

+關注

關注

128文章

8359瀏覽量

144413 -

晶體管

+關注

關注

77文章

9908瀏覽量

140153

發(fā)布評論請先 登錄

相關推薦

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

晶體管電流放大器的原理 晶體管在功放電路中的應用實例

晶體管和二極管的區(qū)別是什么

NMOS晶體管和PMOS晶體管的區(qū)別

什么是單極型晶體管?它有哪些優(yōu)勢?

GaN晶體管和SiC晶體管有什么不同

晶體管收音機和半導體收音機哪個好

晶體管,場效應管是什么控制器件

NPN晶體管的電位關系

晶體管放大飽和截止怎么判斷

晶體管電流的關系有哪些類型 晶體管的類型

半導體未來三大支柱:先進封裝、晶體管和互連

半導體未來三大支柱:先進封裝、晶體管和互連

評論