前言

在調試MGT Bank的時候總會出現這樣那樣的問題,我們有時候會用到這個工具IBERT,那IBERT究竟是什么呢?

IBERT簡介

IBERT(Integrated Bit Error Ratio Tester),集成誤碼率測試儀,它可以利用FPGA內部資源,評估檢測FPGA中GTX的通斷和通信性能。一般的誤碼率可以算到十的負十二次方級別。

這里暫時不介紹IBERT具體的生成過程,因為只是對IP核進行配置即可,下面大概描述下這個過程:

IBERT IP核生成及使用簡介

在Vivado中IP catalog中搜索IBERT,如下:

開始定制IP核。

第一頁:

第二頁

第三頁

注意第三頁的系統時鐘,有兩種選擇,可以選擇外部時鐘源,我這里選擇的就是外部時鐘源,由外部晶振直接提供,還可以選擇第二項,使用GTX差分時鐘:

定制完畢之后,打開Xilinx提供的例子程序:

之后我們的操作就在例子程序中進行,我們需要給MGT Bank提供時鐘,GTX差分時鐘,這個時鐘也許需要我們在FPGA中配置時鐘芯片等。我們的程序就在例子程序的頂層添加吧。

生成bitstream

上板子下載程序

之后是如下界面:

我們通過觀察需要觀察的GTX 通道的Status即可,還可以觀察誤碼率:

FAR-End以及Near-End PCS/PMA

還有一個地方比較關鍵,有多個選擇:

回環模式,可以選擇的有:

正確選擇了,如果你的MGT Bank沒問題,狀態就正常了:

這幾種選擇是什么意思呢?

Near-End PCS

Near-End PMA

Far-End PMA

Far-End PCS

其實我也沒有必要多廢話,就看數據手冊里面講的很清楚:

UG811有,UG476也有。

所謂的Near-End,以及Far-end代表的就是自己的FPGA的MGT和另外的FPGA的MGT。

而PCS以及PMA是MGT的物理層結構。

在博客:高速串行總線系列(3)GTX/GTH 物理層結構分析

以及UG476中都有講。

我們的TX用戶接口的并行數據是先到PCS之后再到PMA的,而RX的接收到的串行數據先到PMA在到PCS。

中間存在串并轉換,不在細講。

由此可見,要做內部自回環以及外部自回環,都可以通過IBERT來實現。

當然還有一個選擇None,也是外回環。

回環的過程是:

Traffic Generator產生數據通過TX發送出去,之后經過一系列路徑,在由RX接收最終到達Traffic Checker,經過將發送的數據與接收數據對比,可以得到各種報告,包括眼圖等。

補充

要做內回環也好,外回環也好,我們需要選擇是那個通道發送以及那個通道接收,這就需要create link,可以選擇該bank上的任意一個通道發送以及任意一個通道接收。當然還有一個最簡單的辦法,就是刪了所有的link,點擊auto link(類似這樣的),Vivado會自動探測到那一路鏈接有通信。

通常都是X0Y6通道發,X0Y6通道收,類似如此,畢竟成雙成對才是真理。

原文鏈接

https://gitcode.csdn.net/66ca084daa1c2020b359a016.html

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614621 -

串行總線

+關注

關注

1文章

185瀏覽量

31013

原文標題:高速串行總線系列-IBERT 使用介紹

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

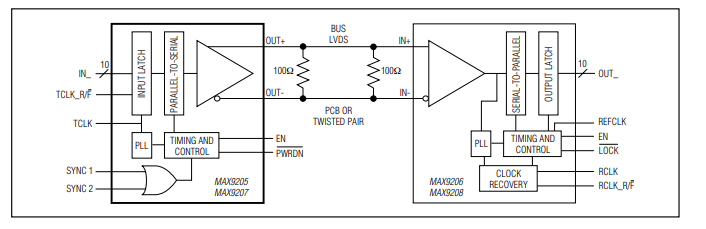

MAX9205/MAX9207 10位、總線LVDS串行器技術手冊

是德S系列示波器如何應對高速串行測試

JDSU Xgig1000 12G SAS/SATA 分析儀應對高速串行總線挑戰的理想平臺

CAN總線通信原理介紹 CAN總線模塊選擇指南

【米爾-Xilinx XC7A100T FPGA開發板試用】+03.SFP光口測試(zmj)

電腦通用串行總線控制器感嘆號怎么辦

電腦通用串行總線控制器怎么接

通用串行總線控制器和通用串行總線設備的區別

USB是通用串行總線

TSB12LV01B IEEE 1394-1995高速串行總線鏈路層控制器數據表

深度解析高速串行信號的誤碼測試|線上講堂

高速串行總線系列-IBERT使用介紹

高速串行總線系列-IBERT使用介紹

評論