當(dāng)前,半導(dǎo)體行業(yè)正在將 3.5D 作為先進(jìn)封裝的下一個(gè)最佳選擇,這是一種混合方法,包括堆疊邏輯芯片并將它們分別粘合到其他組件共享的基板上。

這種封裝模型既滿足了大幅提升性能的需求,又避開(kāi)了異構(gòu)集成中一些最棘手的問(wèn)題。它在數(shù)據(jù)中心內(nèi)已經(jīng)廣泛使用的2.5D和芯片行業(yè)近十年來(lái)一直在努力實(shí)現(xiàn)商業(yè)化的全3D-IC之間建立了一個(gè)中間地帶。

3.5D 架構(gòu)有幾個(gè)主要優(yōu)勢(shì):

它創(chuàng)造了足夠的物理分離來(lái)有效解決散熱和噪音問(wèn)題。

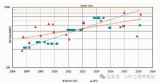

它提供了一種在高速設(shè)計(jì)中添加更多 SRAM 的方法。自 20 世紀(jì) 60 年代中期以來(lái),SRAM 一直是處理器緩存的首選,并且仍然是加快處理速度的必要元素。但 SRAM 不再以與數(shù)字晶體管相同的速率擴(kuò)展,因此它在每個(gè)新節(jié)點(diǎn)上占用更多的空間(以百分比計(jì)算)。而且由于光罩的尺寸是固定的,因此最好的選擇是通過(guò)垂直堆疊芯片來(lái)增加面積。

通過(guò)減小處理元件和內(nèi)存之間的接口,3.5D 方法還可以縮短信號(hào)需要傳輸?shù)木嚯x,并大大提高處理速度,遠(yuǎn)遠(yuǎn)超過(guò)平面實(shí)現(xiàn)。這對(duì)于大型語(yǔ)言模型和 AI/ML 至關(guān)重要,因?yàn)檫@些領(lǐng)域需要快速處理的數(shù)據(jù)量正在激增。

芯片制造商仍然認(rèn)為,完全集成的 3D-IC 是平面 SoC 的最佳替代品,但將所有東西都打包成 3D 配置使得處理物理效應(yīng)變得更加困難。散熱可能是最難解決的問(wèn)題。工作負(fù)載可能會(huì)有很大差異,從而產(chǎn)生動(dòng)態(tài)熱梯度并將熱量困在意想不到的地方,從而縮短芯片的使用壽命和可靠性。除此之外,在每個(gè)新節(jié)點(diǎn)上,電源和基板噪聲都會(huì)變得更加成問(wèn)題,電磁干擾問(wèn)題也是如此。

Ansys產(chǎn)品營(yíng)銷總監(jiān)Marc Swinnen表示:“市場(chǎng)首先采用的是高性能芯片,這些芯片會(huì)產(chǎn)生大量熱量。他們選擇了昂貴的冷卻系統(tǒng),配備了大量風(fēng)扇和散熱器,并且選擇了硅中介層,這可以說(shuō)是連接芯片的最昂貴的技術(shù)之一。但它也能提供最高的性能,并且非常適合散熱,因?yàn)樗c熱膨脹系數(shù)相匹配。散熱是它成功的一大原因。除此之外,你可能想要更大的系統(tǒng),里面有更多東西,而這些東西是無(wú)法放在一塊芯片上的。這只是一個(gè)光罩尺寸的限制。另一個(gè)是異構(gòu)集成,你需要多個(gè)不同的工藝,比如 RF 工藝或 I/O,而這些工藝不必在 5nm 范圍內(nèi)。”

3.5D 封裝還提供了更大的靈活性來(lái)添加額外的處理器內(nèi)核,并且由于可以單獨(dú)制造和測(cè)試已知良好的芯片,因此可以實(shí)現(xiàn)更高的產(chǎn)量,這是Xilinx于 2011 年在 28nm 工藝上率先提出的概念。

3.5D 是所有這些方法的松散融合。它可以包括兩到三個(gè)堆疊在一起的芯片,甚至可以包括水平排列的多個(gè)芯片。

“它的垂直方向受到限制,這不僅僅是因?yàn)樯嵩颍?ASE 集團(tuán)研究員兼高級(jí)技術(shù)顧問(wèn)Bill Chen表示。“這也是出于性能原因。但散熱是限制因素,我們已經(jīng)討論過(guò)許多不同的材料來(lái)幫助解決這個(gè)問(wèn)題——金剛石和石墨烯——但這個(gè)限制仍然存在。”

這就是為什么最有可能的組合(至少在最初階段)是將處理器堆疊在SRAM上,從而簡(jiǎn)化冷卻。不同處理元件的高利用率產(chǎn)生的熱量可以通過(guò)散熱器或液體冷卻去除。而且,使用一個(gè)或多個(gè)變薄的基板,信號(hào)將傳播更短的距離,從而使用更少的功率在處理器和內(nèi)存之間來(lái)回移動(dòng)數(shù)據(jù)。

“最有可能的是,這將是邏輯過(guò)程上的內(nèi)存邏輯,”Arm硅操作工程研究員兼高級(jí)總監(jiān) Javier DeLaCruz 表示。“這些通常都包含在 SoC 中,但其中一部分將是 SRAM,而 SRAM 在節(jié)點(diǎn)之間的擴(kuò)展性不是很好。因此,在內(nèi)存和邏輯過(guò)程中使用邏輯才是真正的制勝解決方案,這是 3D 更好的用例之一,因?yàn)檫@才是真正縮短連接性的原因。處理器通常不會(huì)與另一個(gè)處理器通信。它們通過(guò)內(nèi)存相互通信,因此將內(nèi)存放在不同的樓層,并且它們之間沒(méi)有延遲是非常有吸引力的。”

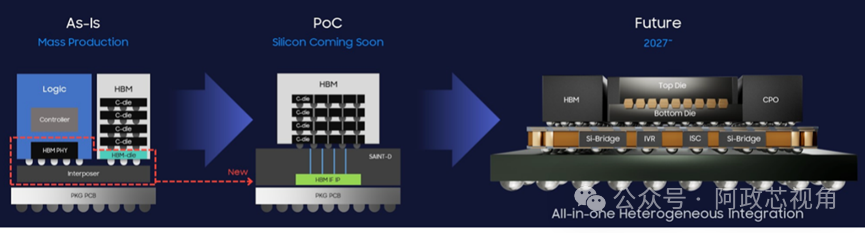

SRAM 不一定必須與處理器的先進(jìn)節(jié)點(diǎn)處于同一節(jié)點(diǎn),這也有助于提高產(chǎn)量和可靠性。在最近的三星代工活動(dòng)中,該公司代工業(yè)務(wù)開(kāi)發(fā)副總裁 Taejoong Song 展示了 3.5D 配置的路線圖,明年將使用 2nm 芯片堆疊在 4nm 芯片上,2027 年將使用 1.4nm 芯片堆疊在 2nm 芯片上。

圖 1:三星的異構(gòu)集成路線圖,顯示堆疊式 DRAM(HBM)、小芯片和共封裝光學(xué)器件。資料來(lái)源:三星代工廠

英特爾代工廠的方法在很多方面都很相似。英特爾高級(jí)副總裁兼代工服務(wù)總經(jīng)理 Kevin O'Buckley 表示:“我們的 3.5D 技術(shù)是在帶有硅橋的基板上實(shí)現(xiàn)的。這不是成本極高、產(chǎn)量低、多掩模版形狀的硅,甚至不是 RDL。我們以更具成本效益的方式使用薄硅片,通過(guò)硅橋?qū)崿F(xiàn)芯片到芯片的連接,甚至是堆疊芯片到芯片的連接。因此,您可以獲得相同的硅密度優(yōu)勢(shì),以及該硅橋的相同 SI(信號(hào)完整性)性能,而無(wú)需在整個(gè)硅橋下方放置巨大的單片中介層,這既成本高昂又限制了容量。它正在發(fā)揮作用。它正在實(shí)驗(yàn)室中運(yùn)行。”

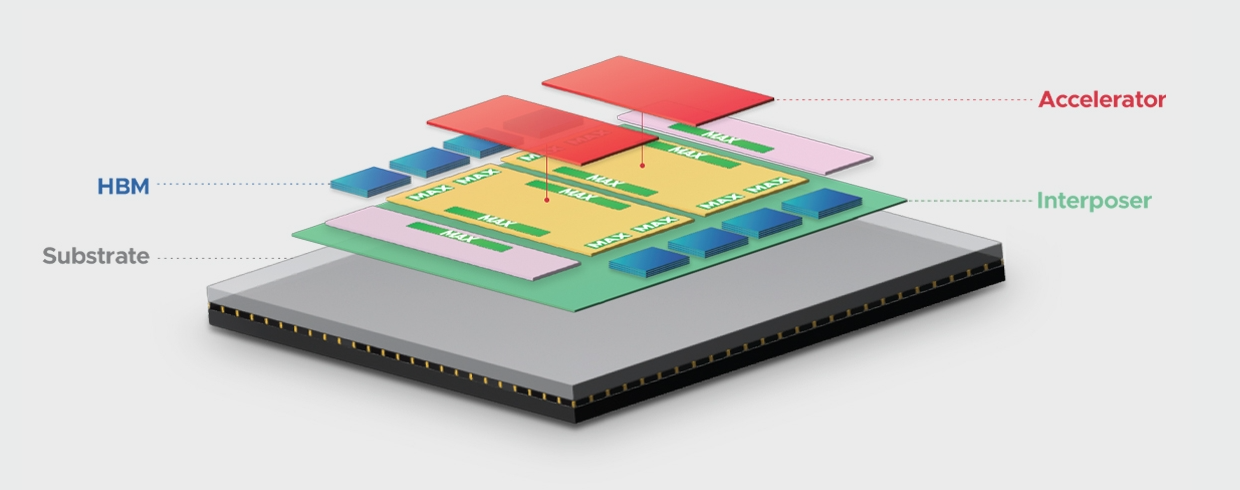

圖 2:英特爾的 3.5D 模型。來(lái)源:英特爾

這里的策略部分是進(jìn)化的——3.5D 至少已經(jīng)進(jìn)行了幾年的研發(fā)——部分是革命性的,因?yàn)闇p薄互連層、找出處理這些更薄互連層的方法以及如何粘合它們?nèi)栽谶M(jìn)行中。可能會(huì)出現(xiàn)翹曲、開(kāi)裂或其他潛在缺陷,并且動(dòng)態(tài)配置數(shù)據(jù)路徑以最大化吞吐量是一項(xiàng)持續(xù)的挑戰(zhàn)。但在兩芯片和三芯片堆棧的熱管理方面已經(jīng)取得了重大進(jìn)展。

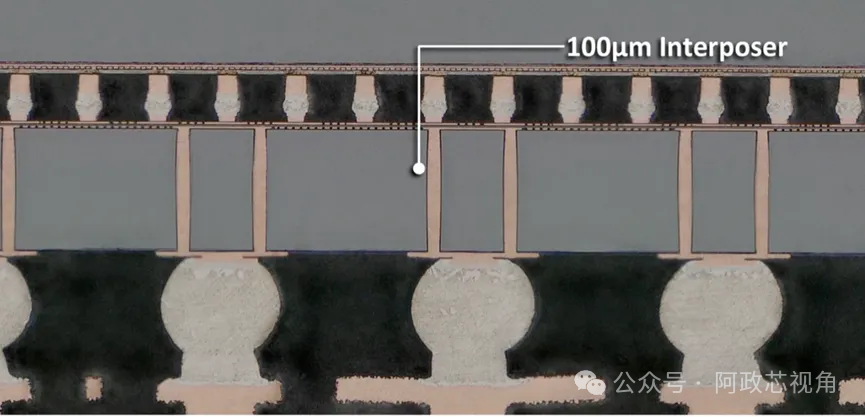

“將會(huì)有多種解決方案,”ASE 公司研發(fā)副總裁 CP Hung 表示。“例如,除了設(shè)備本身和外部散熱器之外,許多人還會(huì)添加浸入式冷卻或局部液體冷卻。因此對(duì)于封裝,您可能還會(huì)看到蒸汽室的實(shí)現(xiàn),這將為設(shè)備本身和外部散熱器之間添加一個(gè)良好的接口。面對(duì)所有這些挑戰(zhàn),我們還需要針對(duì)不同的間距。例如,如今您可以看到批量生產(chǎn)的間距為 45 到 40。這是一種典型的凸塊解決方案。我們預(yù)計(jì)行業(yè)將轉(zhuǎn)向 25 到 20 微米的凸塊間距。然后,為了更進(jìn)一步,我們需要混合鍵合,即小于 10 微米的間距。”

圖 3:當(dāng)今的中介層支持間距為 45m 的 100,000 多個(gè) I/O。來(lái)源:ASE

混合鍵合解決了另一個(gè)棘手的問(wèn)題,即數(shù)千個(gè)微凸塊之間的共面性。“人們開(kāi)始意識(shí)到,我們互連的密度需要一定的平整度,而制造傳統(tǒng)鍵合產(chǎn)品的人很難以合理的產(chǎn)量滿足這一要求,”Promex Industries首席運(yùn)營(yíng)官 David Fromm說(shuō)。“這使得制造它們變得困難,人們的想法是,‘所以也許我們必須做點(diǎn)別的。’你開(kāi)始看到其中的一些。”

-

封裝

+關(guān)注

關(guān)注

128文章

8685瀏覽量

145512 -

邏輯芯片

+關(guān)注

關(guān)注

1文章

158瀏覽量

31354

原文標(biāo)題:3.5D封裝,來(lái)了!(上)

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

3D封裝與系統(tǒng)級(jí)封裝的背景體系解析介紹

3.5D Chiplet技術(shù)典型案例解讀

先進(jìn)封裝技術(shù):3.5D封裝、AMD、AI訓(xùn)練降本

先進(jìn)封裝技術(shù)-19 HBM與3D封裝仿真

TGV玻璃基板主流工藝詳解

3.5D封裝來(lái)了(下)

Cadence如何應(yīng)對(duì)AI芯片設(shè)計(jì)挑戰(zhàn)

博通股價(jià)躍升 或因蘋果與博通合作開(kāi)發(fā)人工智能芯片的利好刺激

一顆芯片面積頂4顆H200,博通推出3.5D XDSiP封裝平臺(tái)

技術(shù)資訊 | 2.5D 與 3D 封裝

新品 | D2PAK和DPAK封裝的TRENCHSTOP?的IGBT7系列

一文理解2.5D和3D封裝技術(shù)

什么是3.5D封裝?它有哪些優(yōu)勢(shì)?

3D封裝熱設(shè)計(jì):挑戰(zhàn)與機(jī)遇并存

3.5D封裝來(lái)了(上)

3.5D封裝來(lái)了(上)

評(píng)論