良好的 EMI 是板級 EMI 設計和芯片 EMI 設計結合的結果。許多工程師對板級 EMI 的降噪接觸較多,也比較了解,而對于芯片設計中的 EMI 優化方法比較陌生。

今天,我們將以一個典型的 Buck 電路為例,首先基于 EMI 模型,分析其噪聲源的頻譜,并以此介紹,在芯片設計中,我們如何有針對性地優化 EMI 噪聲。

01Buck 變換器的傳導 EMI 模型介紹

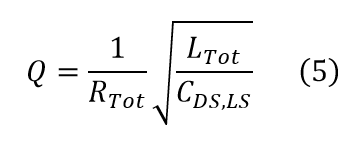

我們知道,電力電子系統中,半導體器件在其開關過程中會產生高 dv/dt 節點與高 di/dt 環路,這些是 EMI 產生的根本原因。

而適合的 EMI 模型可以幫助我們分析噪聲產生的原因。

同時,由于傳播路徑的不同,EMI 可以分為共模和差模噪聲(可詳見:汽車電子非隔離型變換器傳導與輻射EMI的產生,傳播與抑制)。

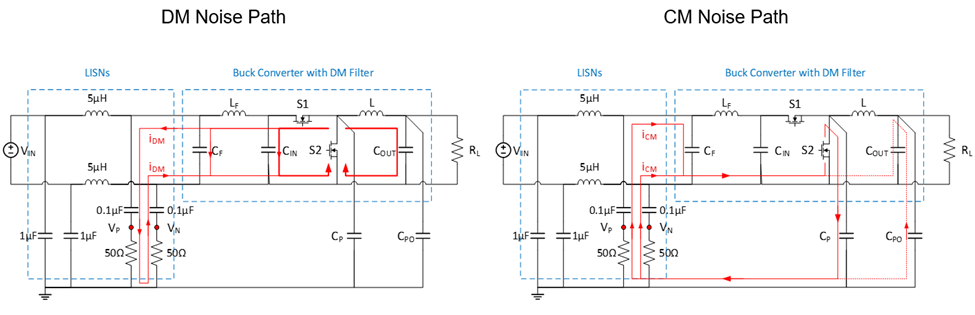

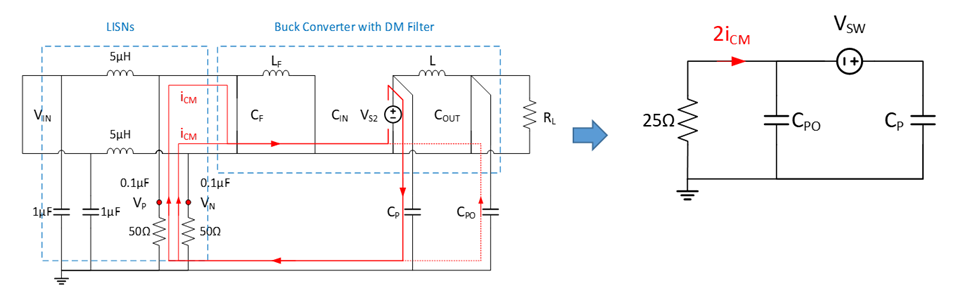

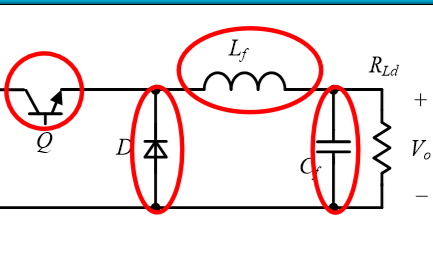

圖 1 中展示了一個典型的 Buck 變換器差模和共模噪聲的傳播路徑。

圖 1 Buck 電路中差模和共模 EMI 的傳播路徑

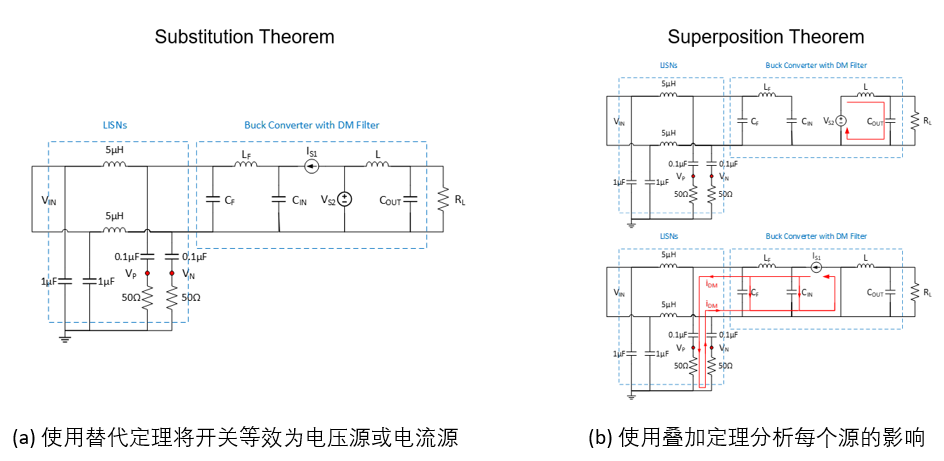

EMI 建模的第一步是把開關用電流源或電壓源進行等效,等效之后,電路各處的電流和電壓依然不變。然后可以使用疊加定理來具體分析每一個源的影響。

以一個 Buck 變換器為例,在圖 2(a) 中,我們將開關用電壓源和電流源進行替代,由于差模電流不留經參考地,因此電路到參考地的寄生參數可以忽略。

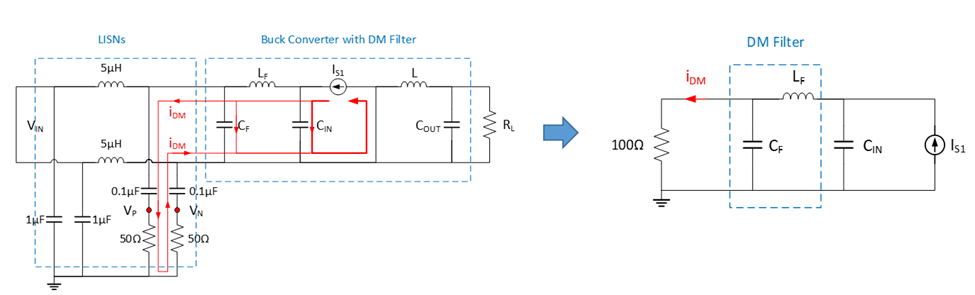

在圖 2(b) 中,我們使用疊加定理對其分別進行分析,需要注意的是,當分析某一個源的影響時,其他的電壓源需做短路處理,而其他的電流源需進行開路處理。由圖 2(b) 可知,實際上差模電流的源可以用 Buck 上管的電流等效,而最終的等效模型可簡化為圖 3 的形式。

圖 2 Buck 差模 EMI 噪聲模型推導

圖 3 Buck 差模 EMI 噪聲模型

由于差模噪聲是由開關電源本身運行狀態決定的,因此,降低差模噪聲的主要方法是設計合理的差模濾波器,而與芯片設計關系不大。本次分享不展開討論。

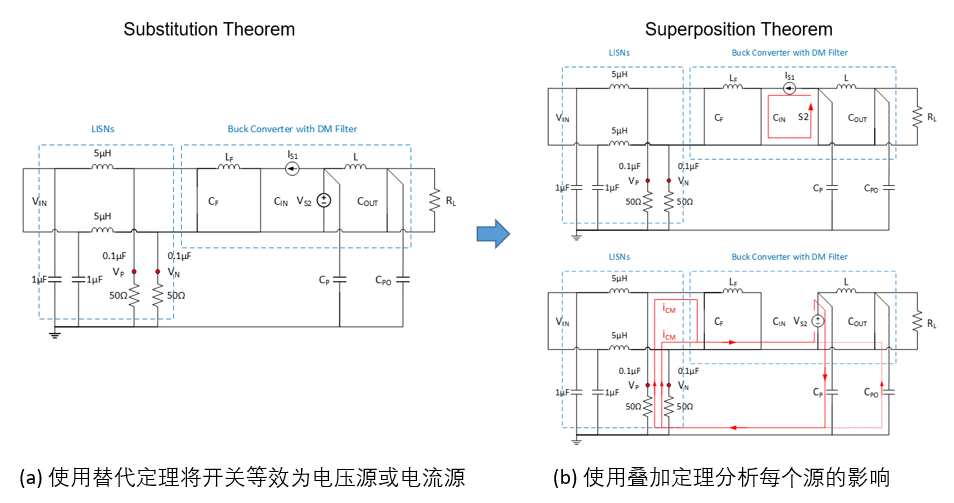

另一方面,對于共模 EMI 噪聲來說,我們可以通過類似的方式進行建模,圖 4 展示了建模的過程。值得一提的是,對于共模噪聲,由于輸入、輸出電容的阻抗通常遠小于電路對地寄生電容的阻抗,因此在建模中,輸入、輸出電容可以作為短路處理。而最終的等效模型可簡化為圖 5 的形式。

圖 4 Buck 共模 EMI 噪聲模型推導

圖 5 Buck 共模 EMI 噪聲模型

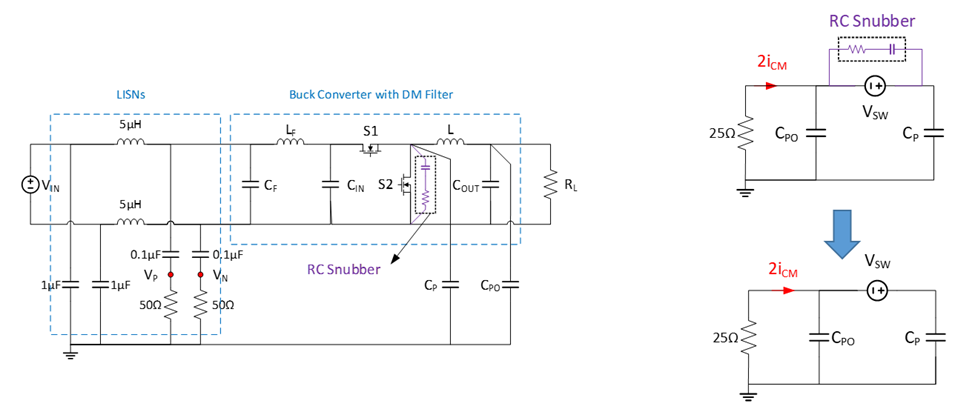

有點工程師朋友可能會有疑惑,這個模型如此簡潔,那么一些其他的電路元件是不是被忽略了呢?(比如圖 6 中所示的 RC Snubber 元件)

但實際上,答案是并不會。

盡管 EMI 模型是相同的,但實際上開關波形會受到外部電路的影響,而這一部分已經被包含在了噪聲源 VSW 中。而在電路分析中,與一個電壓源并聯的器件可以忽略。正因如此,我們可以看到,圖 6 中的 RC Snubber 可以從最終模型中去掉。

圖 6 對于并聯元件的討論

02EMI 共模噪聲源的頻譜分析

根據上一節的內容,我們知道對于 Buck 變換器來說,它的共模 EMI 噪聲源即為開關節點的電壓。

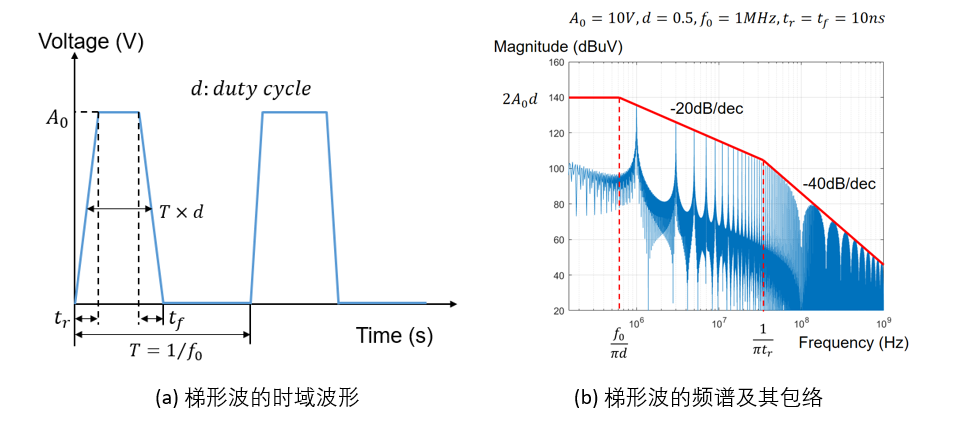

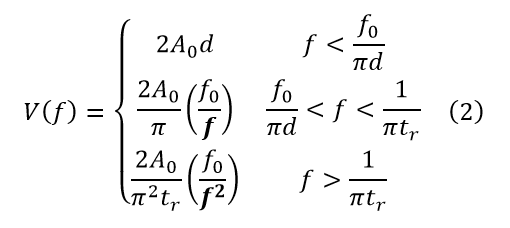

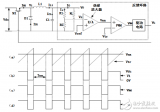

在忽略開關振蕩時,Buck 開關節點電壓波形可以等效為一個梯形波,如圖 7(a) 所示。其中梯形波的幅值 A0 即為 Buck 的輸入電壓,tr 和 tf 對應節點電壓的上升和下降時間,波形的周期 T 為 Buck 的開關頻率 f0 的倒數,d 為 Buck 電路的占空比。

圖 7

如果在頻域上對這個波形進行分析,我們將會得到形如圖 7(b) 中的頻譜,而它的包絡線分為兩段:從 f0 / πd 到 1 / πtr(tr 取上升時間和下降時間中的較小值),頻譜的包絡以每十倍頻率 20dB 下降;而在 1 / πtr 后,頻譜的包絡以每十倍頻率 40dB 下降。

那這個結論是怎么產生的呢?

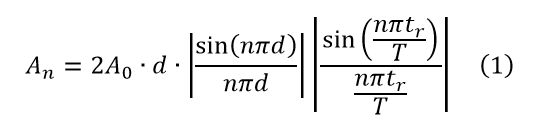

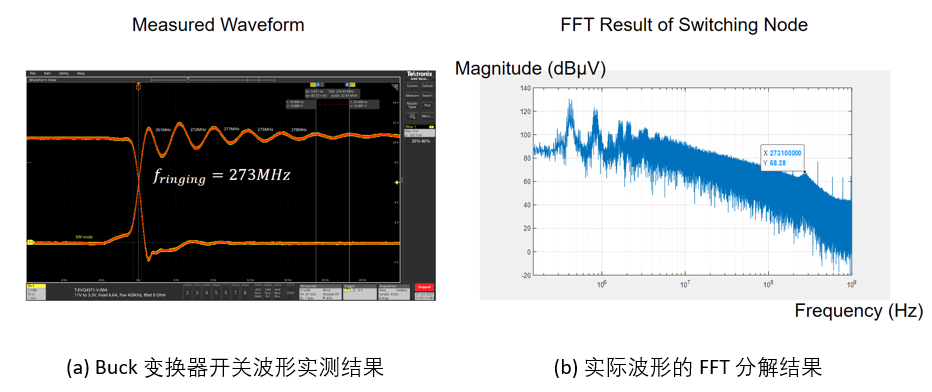

實際上,如果對此梯形波進行傅里葉分解,我們將會得到如下的表達式,其中,An 為其 n 次諧波的幅值。

對 sin(x) / x 這樣的形式,在 x<1 時,sin(x) / x < 1;在 x > 1時,sin(x) / x < 1 / x。

因此我們可以將其簡化為公式(2)中所示的形式,并依此畫出包絡線。

對于 f0 / πd 到 1 / πtr 區間的表達式,函數與頻率成反比;而在 1 / πtr 之后,函數與頻率的平方成反比。因此我們得到了圖 7 中展示的斜率。

從公式(1)中我們還可以得到一些有趣的結論。

如圖 8 (a) 所示,如果 d = 0.5,當 n 為偶數時,An = 0,因此在頻譜上是沒有偶數次諧波分量的。

另外,如圖 8 (b) 所示,當 d 與 0.5 接近的時候,偶次諧波的包絡約等于 2A0 | d - 0.5 |。對于汽車電子來說,12V 轉 5V 是一個很常見的應用,此時的占空比也比較接近 0.5,可以用這個結論幫助進行分析。

圖 8

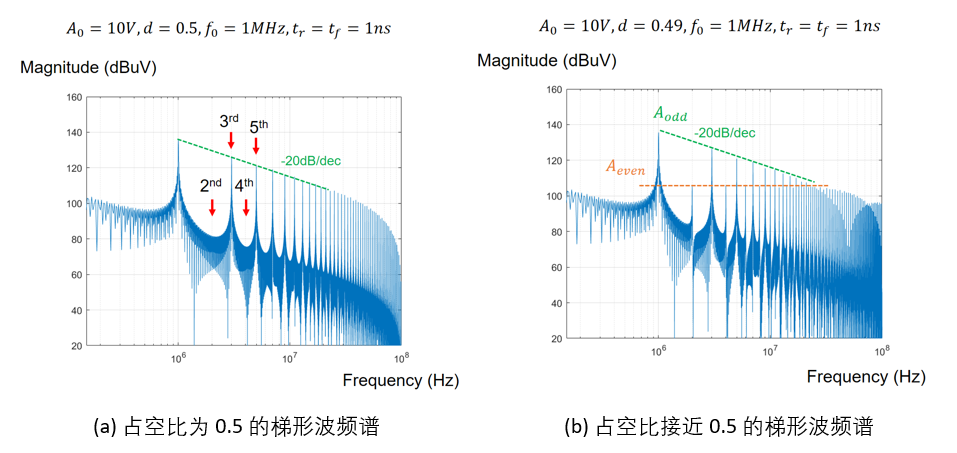

從公式(2)中,我們也可以對開關頻率以及上升下降時間的影響進行量化分析。

在其他條件不變的前提下,如圖 9 (a) 所示,如果開關頻率提高十倍,高頻 EMI 的噪聲源會整體提高 20dB;而如圖 9 (b) 所示,如果開關上升/下降時間變為初始值的十分之一,則高頻 EMI 的噪聲源也會整體提高 20dB。

因此,提高開關頻率雖然有助于減小電感元件,但確實也對 EMI 提出了更高的挑戰。而對于芯片設計來說,MPS 的大部分汽車電子芯片都支持客戶通過模擬或者數字的形式來設置開關頻率,從而幫助客戶通過 EMI 測試。

圖 9

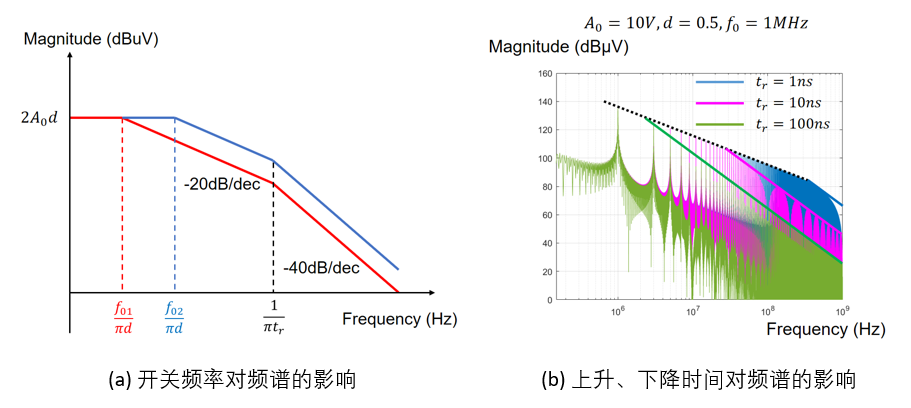

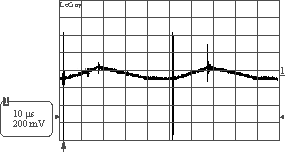

以上分析主要是基于理想開關波形,而實際開關波形(如圖 10(a) 所示)則往往會帶有一些振蕩,而在 EMI 頻譜上,在對應振蕩頻率的位置也會出現一個凸起(如圖 10(b) 所示)。我們將在下一節中分析如何對這個問題進行優化。

圖 10

03IC 設計中優化 EMI 的方法

A對開關波形振蕩的優化

我們知道,在實際電路中,芯片、無源元件,以及 PCB 走線都會帶來一些寄生參數。而在開關過程中,這些寄生參數會造成一些振蕩。

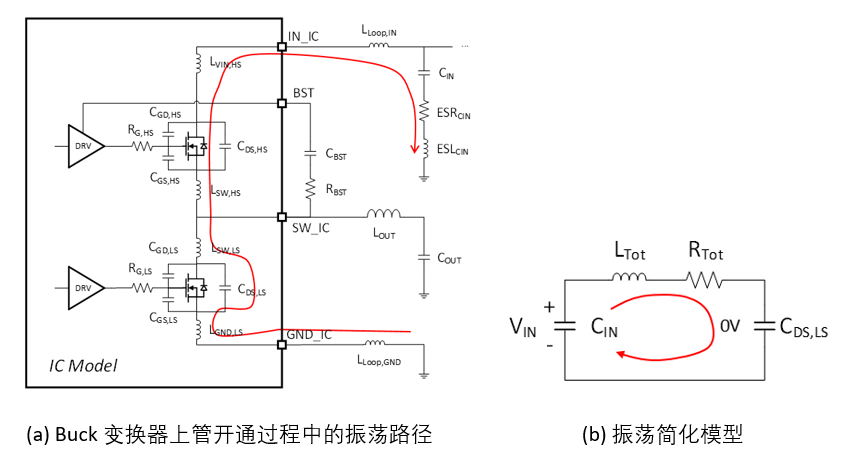

圖 11(a) 中展示了 Buck 變換器上管開通過程中,形成開關節點振蕩的回路,其中 LLoop,IN,LLoop,GND 為 PCB 走線帶來的寄生電感,LVIN,HS,LSW,HS,LSW,LS,LGND,LS 為引腳到芯片內部晶片各節點的引線電感,CDS,CGD,CGS 為 MOS 管的寄生電容。

這個回路其實是距離芯片最近的一顆輸入電容 CIN 與芯片上下管之間形成的回路。在諧振發生時,CIN 上的電壓較穩定,可以近似等效為輸入電壓 VIN。

圖 11

通過進一步簡化,我們可以得到圖 11(b) 中的串聯諧振模型,其中,RFET,HS 為上管在開通過程中的電阻:

值得一提的時,在開通過程中,FET 處于飽和區,隨著 VG-S 的增加,RFET,HS 會逐漸減小,最終達到導通電阻。

對于這個串聯諧振,其品質因數 Q 如公式(5)所示:

我們知道,Q 值越大,振蕩越強烈。因此,為了從源頭上減小這個振蕩,我們需要做的是減小 LTot 的值,或者增大 RTot 和 CDS,LS。

在板級電路的設計上,是有一些方法來做到這點的。比如,通過在下管并聯一個 RC Snubber,可以等效增大電容;或者通過增加 Bootstrap 電阻來減小開通速度,從而等效增大諧振發生時的 RFET,HS 。但這些方法也有一些副作用,如增加了損耗,也增加了電路成本。

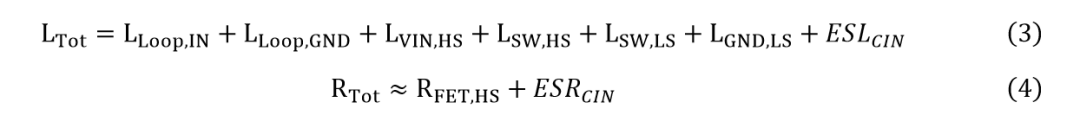

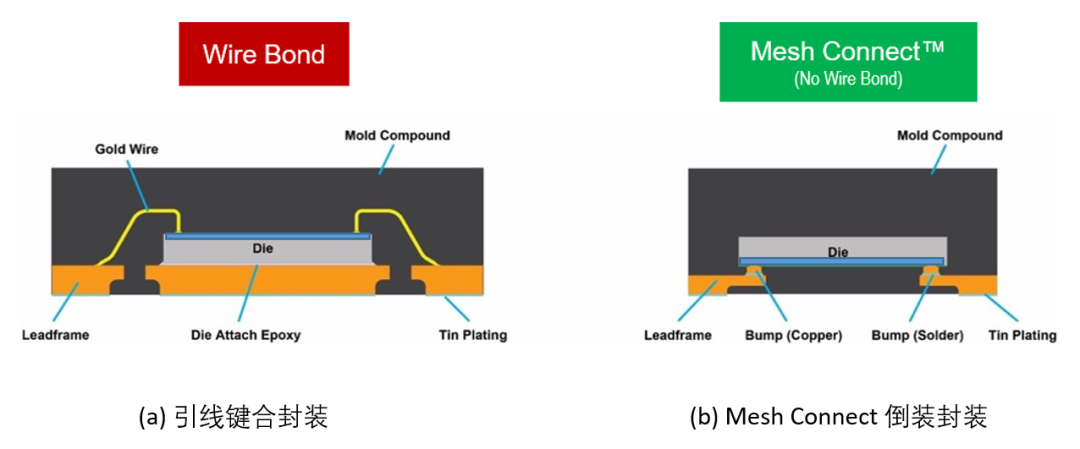

從芯片設計上進行優化的優勢更明顯,副作用更小。從封裝技術上,相比傳統的引線鍵合封裝(如圖 12(a) 所示),MPS 的倒裝封裝技術(如圖 12(b) 所示)大幅減小了封裝帶來的寄生電感,可將 LVIN,HS,LSW,HS,LSW,LS,LGND,LS 等從 nH 級降為 pH 級。

圖 12

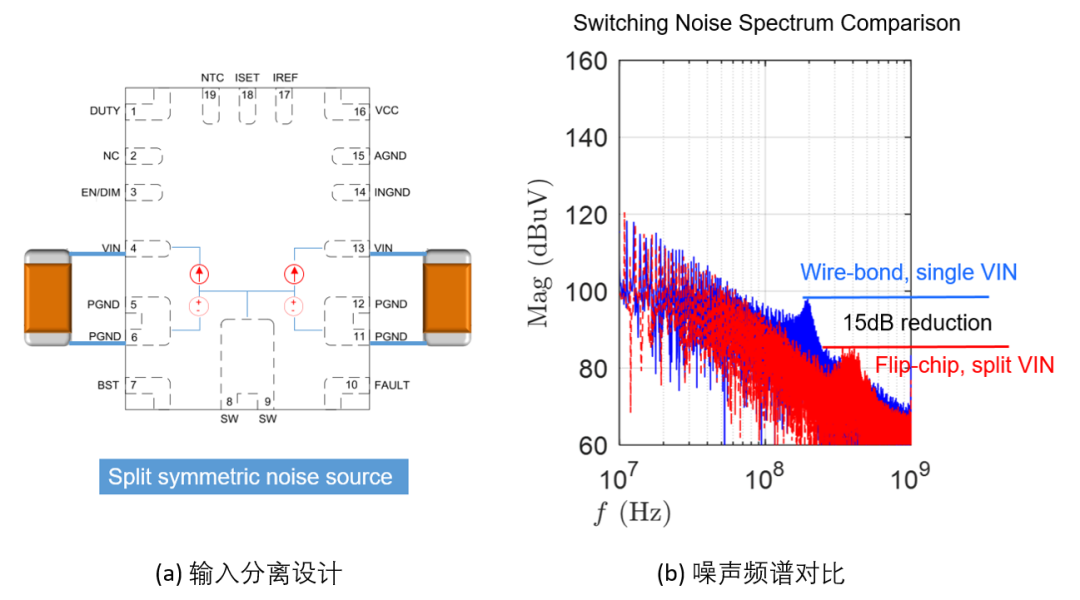

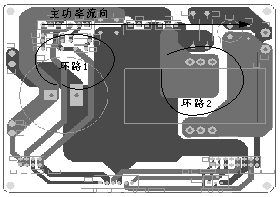

此外,由于振蕩回路是由 VIN 與芯片內部上下管形成,通過將輸入環路分離為對稱的兩部分(如圖 13(a) 所示),MPS 可以進一步降低輸入回路的寄生電感。

圖 13(b) 對比了引線鍵合、單輸入封裝和倒裝封裝、輸入分離設計的兩顆芯片的噪聲源頻譜。從圖中可見,封裝的改進帶來了 15dB 以上的提升。

圖 13

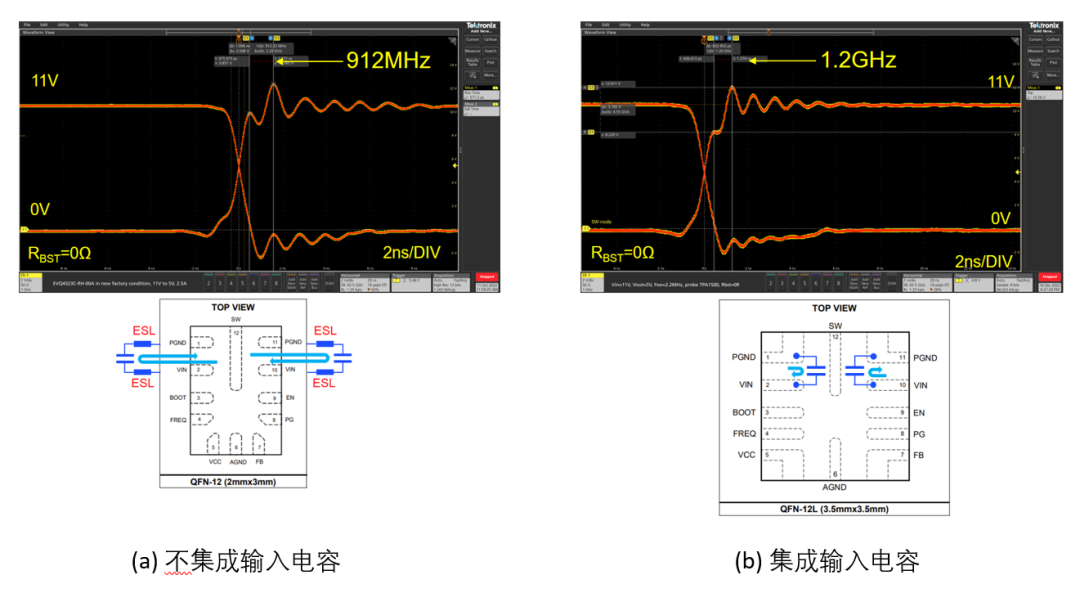

為了進一步減小輸出回路的電感,MPS 還可以進一步將輸入電容也集成在封裝之中。

圖 14 對比了集成輸入電容的開關波形,由于回路電感進一步減小,諧振頻率已經在 1GHz 以上,已經超過了許多 EMI 測試的要求范圍。

圖 14 開關波形與引腳示意圖

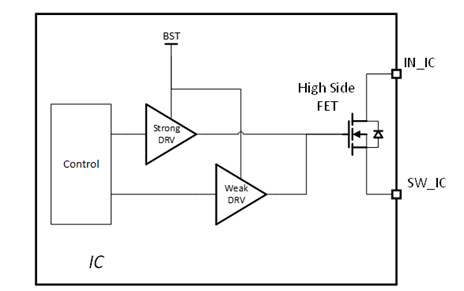

除了封裝技術之外,在電路設計上也可以通過動態調整開關速度,使得諧振發生時,上管處于剛剛導通的狀態,此時,RFET,HS 較大,從而可以有效抑制振蕩強度。這一設計可通過設計多級驅動,并在合適的時間開通不同驅動來實現。

圖 15 為一個兩級驅動的示例。

圖 15 多級驅動(以兩級驅動為例)

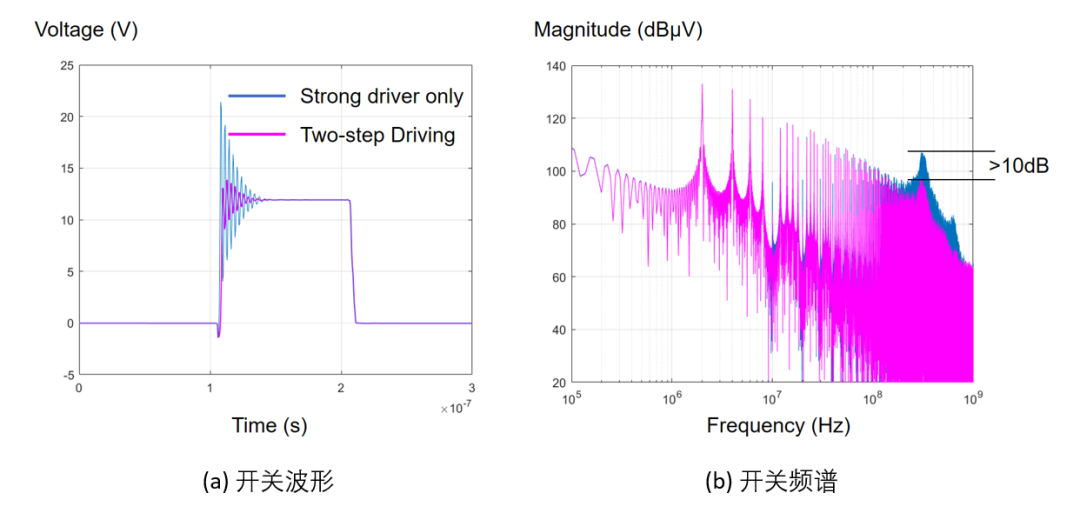

圖 16 比較了傳統的單級驅動方式與兩級驅動的效果。

從圖 16(a) 的時域波形上可以看出,兩級驅動有效地降低了開關時的振蕩,而從圖 16(b) 的頻譜上來,兩級驅動也有非常明顯的效果,將振蕩產生的 EMI 峰值抑制了 10dB 以上。因為這一方法只改變了諧振回路中的電阻,因此諧振頻率不會發生變化。

另外,值得一提的是,由于多級驅動實際上降低了開關速度,它對開關損耗是有一定影響的。但相比于增加 Bootstrap 電阻的方法,由于多級驅動可以動態調節開關速度,在諧振發生后,芯片可以加快管子開通速度,從而使得總開關時間僅有有限的增加,來減少過多的開關損耗。

圖 16 單級驅動與兩級驅動對比

B通過抖頻設計優化 EMI

抖頻技術可以通過將開關能量分散到不同的頻率上,從而有效降低 EMI,這一部分在之前的分享中有詳細介紹(可詳見:選擇合適參數進行抖頻設計),因此在本文中暫略。

總結

在本次的分享中,基于對噪聲源頻譜的分析,我們可以量化各個關鍵參數對于頻譜的影響。另外,我們也介紹了芯片設計中降低 EMI 噪聲的一些方法:

從開關頻率的選擇上,MPS 芯片支持多種開關頻率的選擇,部分芯片也可以開啟抖頻;

從封裝與布線設計上,MPS 的倒裝封裝,對稱輸入設計,集成輸入電容等技術可以有效降低高頻噪聲源;

從驅動方法上,MPS 獨特的多級驅動可以有效減小開關振蕩。

-

emi

+關注

關注

53文章

3726瀏覽量

130419 -

變換器

+關注

關注

17文章

2132瀏覽量

110478 -

噪聲源

+關注

關注

0文章

42瀏覽量

11616 -

共模噪聲

+關注

關注

1文章

57瀏覽量

10993

原文標題:【工程師筆記】EMI 噪聲源的分析與優化方法

文章出處:【微信號:MPS芯源系統,微信公眾號:MPS芯源系統】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

BUCK變換器設計

高頻共模電流、電壓和阻抗的測量 —— 以反激變換器為例

BUCK變換器的DCM模式建模

Buck變換器參數辨識的分析

Buck變換器的EMC分析

Buck 三電平變換器

buck變換器設計_自制buck變換器

buck變換器工作原理_Buck變換器的降壓原理分析

Buck變換器的工作原理與設計的學習課件免費下載

Buck變換器中EMI噪聲源的優化方法

Buck變換器中EMI噪聲源的優化方法

評論