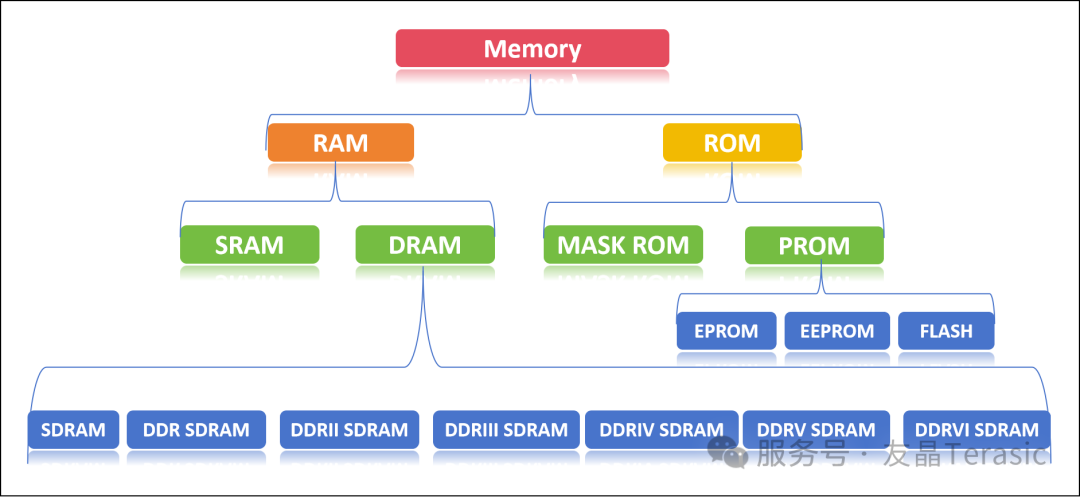

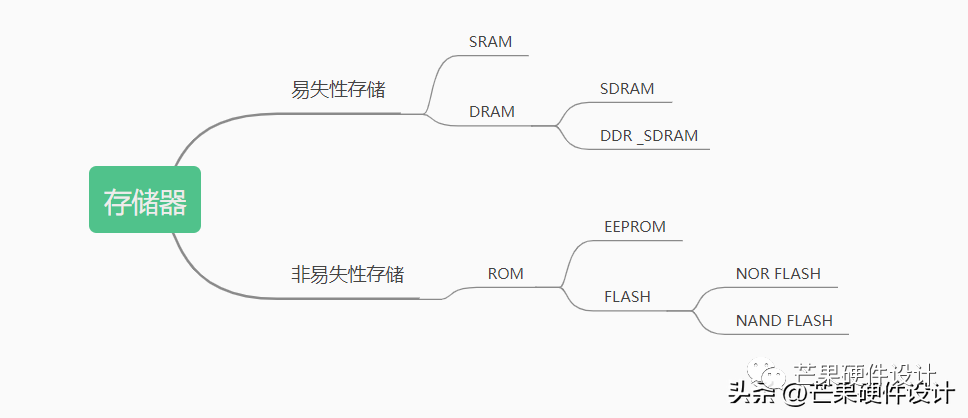

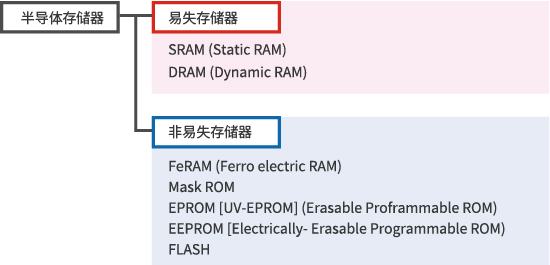

存儲器分類

初學者要了解SDRAM需要先了解存儲器分類。按照存儲器的存儲功能劃分,可將其分為RAM 和 ROM 兩大類。

RAM(Random Access Memory)存儲器又稱隨機存取存儲器,正常工作時存儲的內容可通過指令隨機讀寫訪問,RAM中的數據在掉電時會丟失。

ROM(Read Only Memory)存儲器又稱只讀存儲器,只能由專用的裝置寫入,一旦寫入,不能隨意改寫。正常工作時ROM只能讀出數據。ROM 具有掉電后數據可保持不變的優點。

RAM往下又可細分為SRAM和DRAM。

SRAM

SRAM(Static RAM),全稱為靜態隨機存取存儲器,是一種在系統不斷電的情況下能無限期保持其內容的記憶設備。由于其讀寫速度極快且能耗極低的特點,在對速度和可靠性要求較高的應用場景中,如CPU緩存等,SRAM成為了首選方案。然而,值得注意的是,SRAM每個存儲單元采用了復雜的雙穩態電路設計來保存數據,制作一個bit存儲位通常需要6個MOS管,這直接導致了其集成度低(容量一般只能到幾百到幾兆字節)且制造成本遠高于DRAM。

DRAM

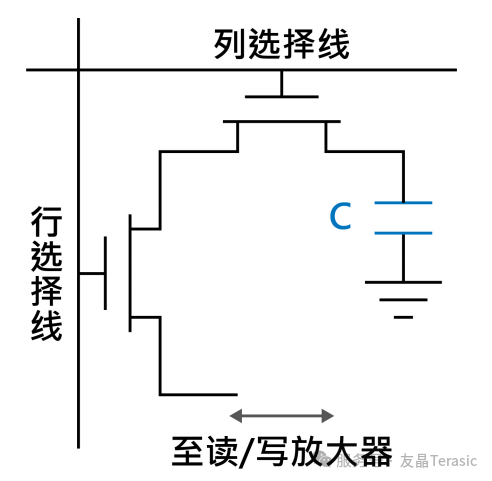

DRAM(Dynamic RAM),動態隨機存取存儲器,與制作一個 bit存儲位通常需要6個MOS管的SRAM相比,保存一位數據簡單到只需一個電容,其中一個存儲器單元的結構如圖所示。當行選擇線與列選擇線動作時,可令 MOSFET 接通,允許電容的電壓被讀取或寫入。

由于電容的電壓會有傳輸時的損失以及保存時的漏電現象,所以除了在讀取與寫入時必須經過放大之外,每保存一位經過一段時間就必須將數據讀出后再寫入一次,這個動作稱為 DRAM 的刷新(Refresh),會降低使用效率。

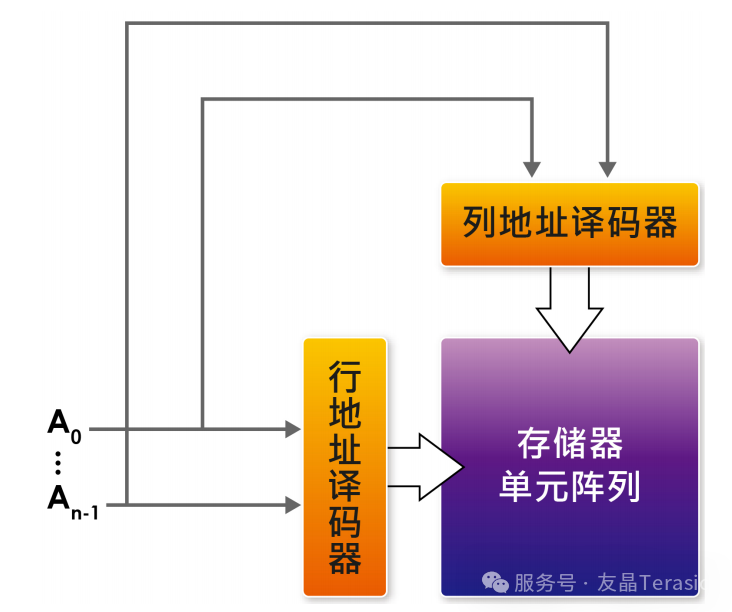

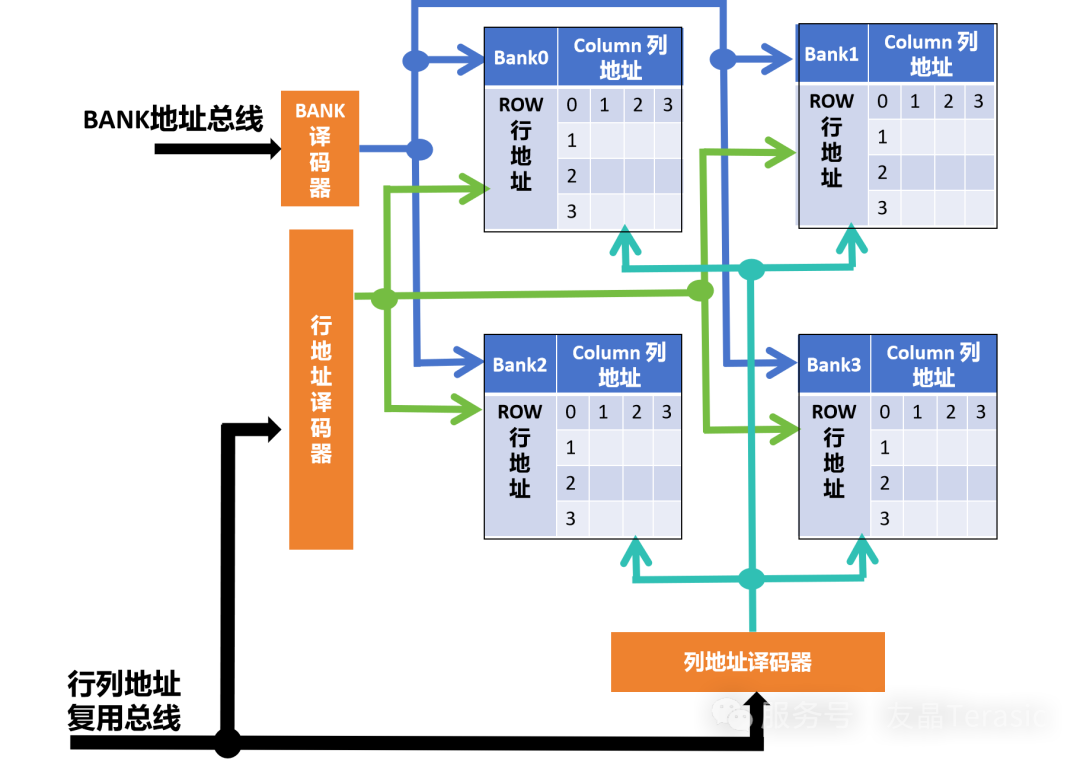

為了降低封裝成本,減少 IC 引腳的數目, DRAM 的地址輸入線是采用多工方式,亦即以同樣的地址線分兩次輸入,先輸入行地址再輸入列地址,如下圖所示。對于 n 條地址線輸入的 DRAM,可以規劃最大譯碼的存儲器單元數目為 22n,因此常見 DRAM 芯片的 容量多以 4 的倍數遞增,如 4M Byte、 16M Byte、 64M Byte、 256M Byte 等等。

SDRAM的誕生

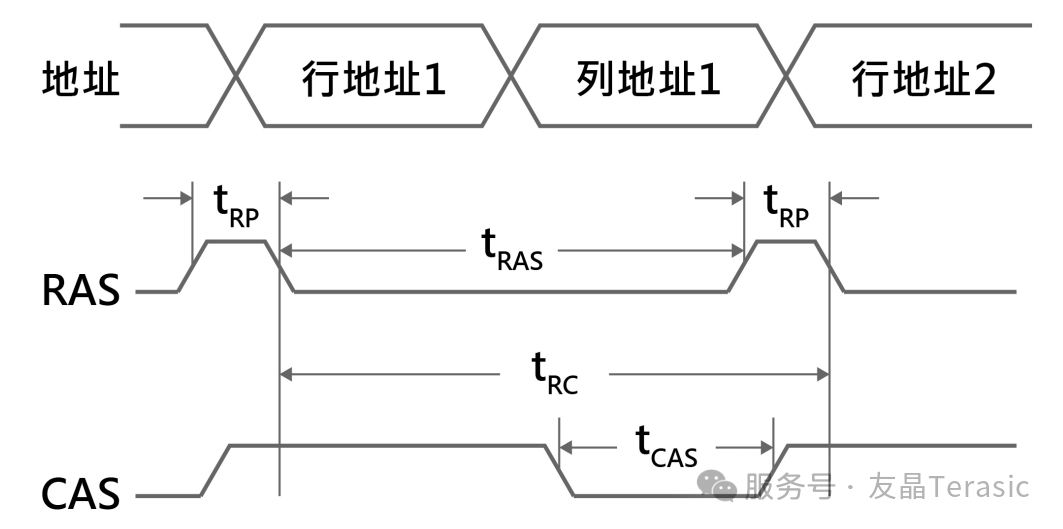

由于 DRAM 是以 MOSFET 為主要器件,電路中的雜散電容(Stray Capacitance)對存取時間的影響很大,每更換一次行地址時,都必須等待一段時間讓控制電路充電,數據的存取才會正確,此充電時間稱為預充電時間(Prechage Time, TRP),如下圖所示。早期 DRAM 的行地址是由 RAS 信號的下降沿來鎖住后送給行地址譯碼器處理,在此 RAS信號至少要維持一段建立行地址時間(tRAS),這段時間內再以 CAS 信號的下降沿來鎖住列地址后送給列地址譯碼器處理,才能譯碼到一個正確的存儲器單元地址,因此一個DRAM 的存取周期(tRC)可用預充電時間加上行地址建立時間來計算:tRC = tRP + tRAS。

這不算短的時間,使得 DRAM 無法成為高速的存取設備,但是低價大容量的特性怎么會讓廠商輕易放棄呢?于是在商業的競爭下,經過階段性的改良,同步動態隨機存儲器(Synchronous Dynamic Random Access Memory,簡稱 SDRAM)誕生。如前面所述, DRAM 在更換行地址時需有預充電時間的天生障礙,限制了分散數據的隨機存取速度,但是對于可預知下一筆數據地址的突發模式(Burst Mode), SDRAM 采用存儲器交錯處理(Memory Interleaving)以及多管線(Multi-Pipeline)的技術,提升分配時間內讀寫的信息量,改善了在突發模式下的存取時間。由于在連續存取的應用中可達到與外部時鐘同步的效率,故被稱為同步動態隨機存儲器。

所謂突發模式是存取存儲器時,分配一次存儲器的地址,即可進行一連串的存或取動作 N 次,不需分配 N 次存儲器的地址,可以省去尋址的時間。至于存儲器交錯處理是將存儲器劃分成多個BANK(通常為 2 個或 4 個BANK),如圖:

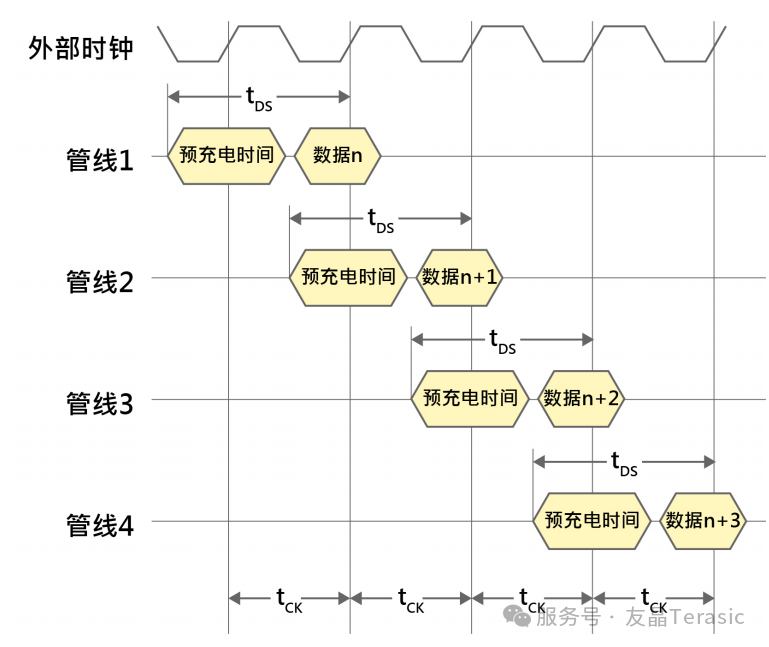

控制端可交錯存取這些BANK的數據,舉例來說,將保存于存儲器的奇數地址和偶數地址分開,當上一個字符被更新時,下一個字符的存取可以不受到影響,減少了等待的時間,讓存儲器的存取更快,雖然不是 2 或 4 倍的速度,但還是快了許多。而多管線是指利用選擇器的原理將存儲器多個區塊的數據輪流傳送至數據端,下圖即說明了一個 SDRAM 的存取時間 (tDS) 大于外部一個時鐘時間 (tCK),但在多管線的架構下,外部仍可同步讀取數據。

存儲器交錯處理與多管線硬件功能的結合,可以有效的忽略等待地址譯碼及預充電的時間。但值得注意的是,SDRAM 可以改善的是數據預選及輸出的方式,并非數據真正的存取時間,所以對于突發模式下的第一筆數據的存取時間仍然無法改善。

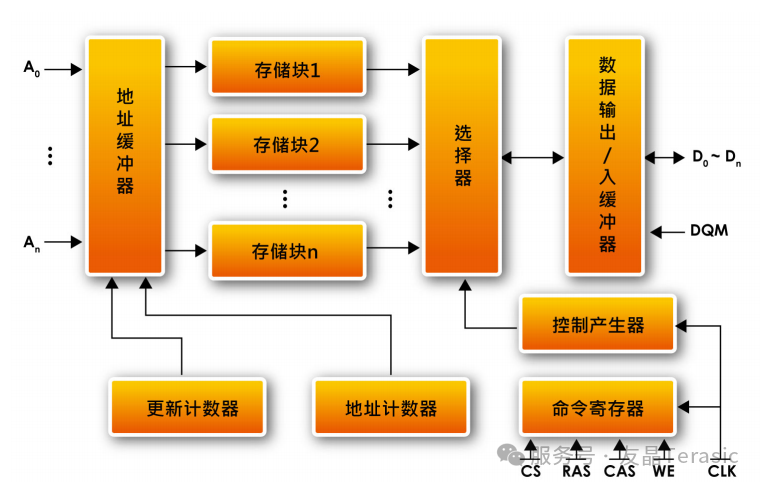

另外,因為 SDRAM 可以選擇操作模式與調整突發存取的長度,與傳統的 DRAM 在使用程序上有所不同,必須先對 SDRAM依序寫入命令才能進行存取,下圖為簡化后SDRAM 的架構圖。另外, SDRAM 的數據寬度均配合 CPU 的發展而生產,故有 8 位、16 位、 32 位、 64 位的產品。

DDR SDRAM

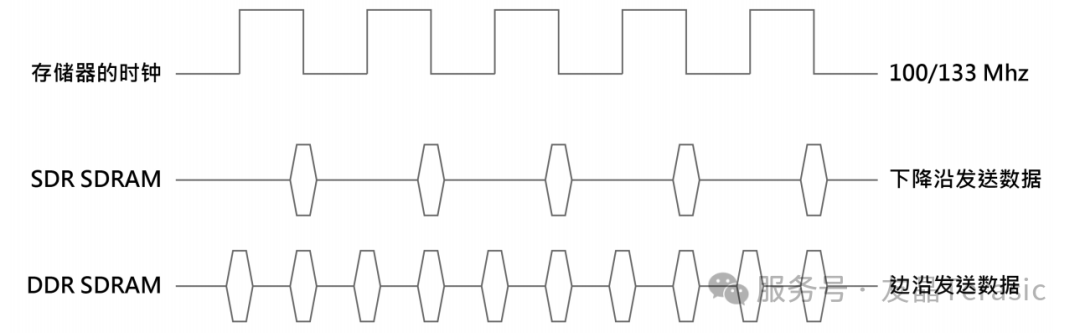

至于 DDR SDRAM ,即雙倍數據率(Double Data Rate) SDRAM 的意思,相較于前面所介紹的 SDRAM 僅在存儲器時鐘下降沿存或取數據,他利用時鐘的上升沿及下降沿都可存或取數據,故數據的傳輸速率為 SDRAM 的兩倍。為了與 DDR SDRAM 區別, SDRAM 又常被稱為 SDR SDRAM。比較下圖中 SDR 與 DDR SDRAM 存取數據時序的差異,可知一個工作于 64 位 /100MHz 時鐘下的 DDR SDRAM,每秒數據的傳輸量為 100M x 64bit x 2 / 8bit =1600MB,而 SDR SDRAM 則僅為其一半 800MB。此外 SDR SDRAM 的電源為 3.3V,而 DDR SDRAM 為 2.5V,DDR 的省電性較占優勢。

DDR SDRAM發展很快,后來出現了DDR2 SDRAM、DDR3 SDRAM,而現在都已經有DDR6 SDRAM了,但它們的控制都基于SDRAM控制原理演變而來。

SDRAM總結

總而言之,SDRAM即同步動態隨機存取存儲器。“同步”是指其時鐘頻率與FPGA系統時鐘頻率相同,并且內部命令的發送與數據的傳輸都以此頻率為基準;“動態”是指存儲陣列需要不斷的刷新來保證所存儲數據不丟失;“隨機”是指數據不是線性依次存儲,而是自由指定地址進行數據的讀寫。

-

DRAM

+關注

關注

40文章

2343瀏覽量

185282 -

SDRAM

+關注

關注

7文章

441瀏覽量

56105 -

存儲器

+關注

關注

38文章

7640瀏覽量

166636 -

MOS管

+關注

關注

109文章

2542瀏覽量

70124

原文標題:02-SDRAM控制器的設計——SDRAM簡介

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

存儲器的分類及其區別

存儲器的分類及其區別

存儲器的分類及其區別

評論