在一個CAN網絡中,如果希望有良好的讀位,那么采樣點的時間位置相對來說是非常重要的。因此,所有的網絡節點都有質量時鐘。然而,石英和諧振器有公差,會隨著溫度和時間漂移。只要變量保持在一個公差范圍內,協議管理器就可以補償錯誤。

CAN協議的建議要求對時鐘頻率最大限度的最大限度地容忍1.58%。

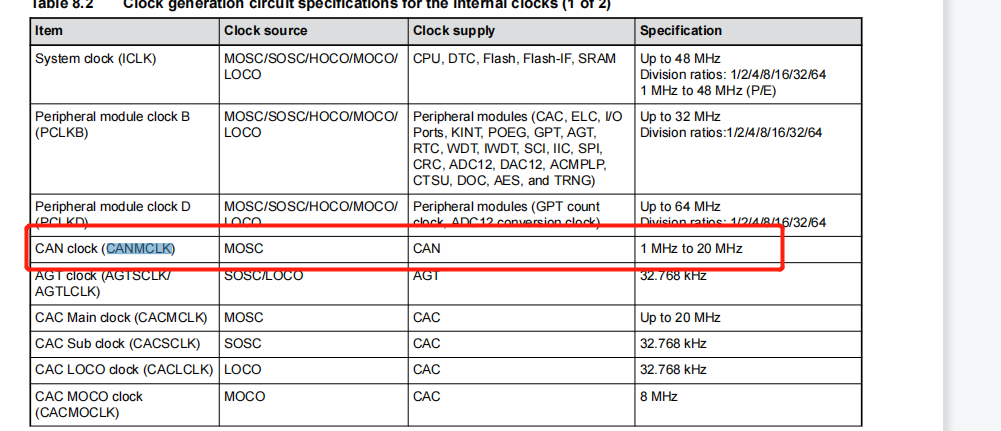

在這種情況下,建議直接使用石英或諧振器的時鐘,而不是由PLL產生的系統時鐘。實際上,PLL(抖動)的頻率變化是無法滿足要求的精度的。

根據μC的類型,它可能會導致改變石英頻率以獲得網絡排放的愿望。讓我們以一個可以使用500 kbit/s波特率的網絡為例,在這種情況下,CAN總線的頻率必須在8MHz上配置。

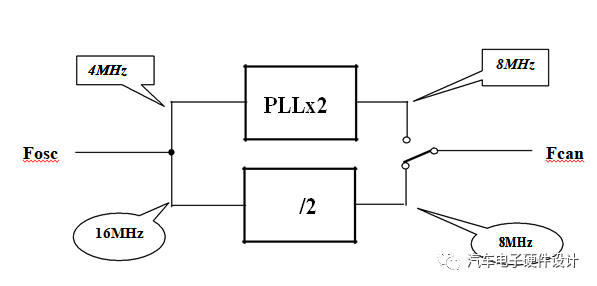

在圖30的結構中,4MHz的quartz足以滿足選擇的PLL(x2)。另一方面,通過避免PLL,16MHz的石英是必要的

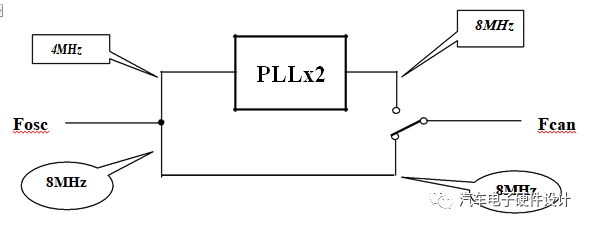

在圖31的結構中,沒有PLL的連接是直接的。在這種情況下,可以保留8MHz的石英。

-

mcu

+關注

關注

146文章

17874瀏覽量

361218 -

CAN

+關注

關注

57文章

2895瀏覽量

466907 -

諧振器

+關注

關注

4文章

1146瀏覽量

66527

原文標題:MCU健壯性設計之CAN時鐘

文章出處:【微信號:QCDZYJ,微信公眾號:汽車電子工程知識體系】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

隔離CAN收發器SiLM5150S產品特性

LabVIEW程序評估_健壯性和簡單性

全新MM32系列的特點

can總線結構和原理

MCU健壯性設計之模擬輸入的特殊特性

MCU健壯性設計之如何配置數字輸入/輸出

如何在IAR Embedded Workbench中填充提高系統的健壯性

CAN與CAN FD的區別是什么?

MCU健壯性設計之CAN時鐘

MCU健壯性設計之CAN時鐘

評論