Tiny_SoC簡介

RISC-V 是一種基于精簡指令集(RISC)原則的開源指令集架構(gòu)(ISA),其開放性和靈活性使其在嵌入式系統(tǒng)和計(jì)算應(yīng)用中得到了廣泛應(yīng)用。在 FPGA 上實(shí)現(xiàn) RISC-V 處理器,可以充分利用 FPGA 的可編程性和高性能特點(diǎn),構(gòu)建定制化的微處理器設(shè)計(jì)。

智多晶Tiny_SoC是基于RISCV-I指令集設(shè)計(jì)的一款輕量化軟核,集處理器核心、豐富外設(shè)與智能中斷管理于一體,為開發(fā)者提供“開箱即用”的輕量化設(shè)計(jì)體驗(yàn)!

Tiny_SoC特點(diǎn)

搭載32位RISC-V處理器(RV32-I指令集),5級流水線設(shè)計(jì),主頻高達(dá)120MHz,性能達(dá)0.5DMIPS/MHz,集成JTAG調(diào)試接口(兼容OpenOCD)。

(*注:根據(jù)使用資源占用情況,最高主頻會(huì)有所變化)

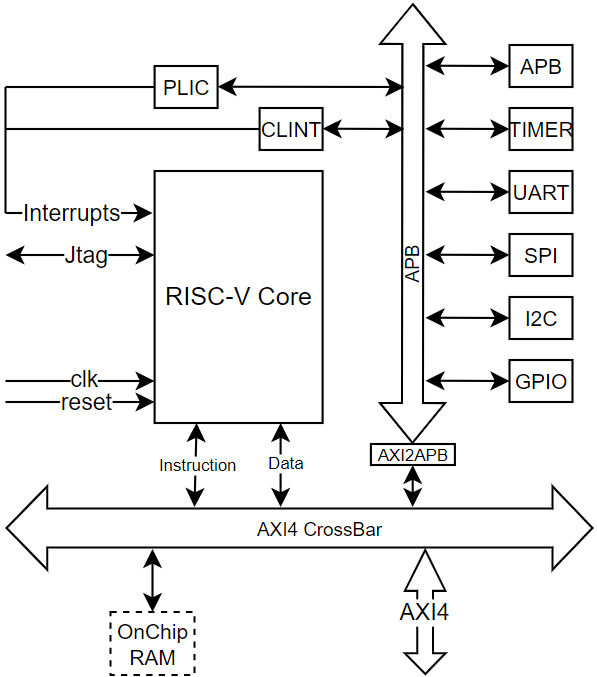

圖 1Tiny_SoC系統(tǒng)框圖

資源占用低至1.2K LUTs(默認(rèn)配置),支持UART、SPI、I2C、GPIO、定時(shí)器等常用外設(shè),輕松適配從智能傳感器到復(fù)雜控制器的多樣化場景。

同時(shí)提供3路AXI接口+5路APB接口,支持自定義外設(shè)擴(kuò)展,滿足個(gè)性化開發(fā)需求。

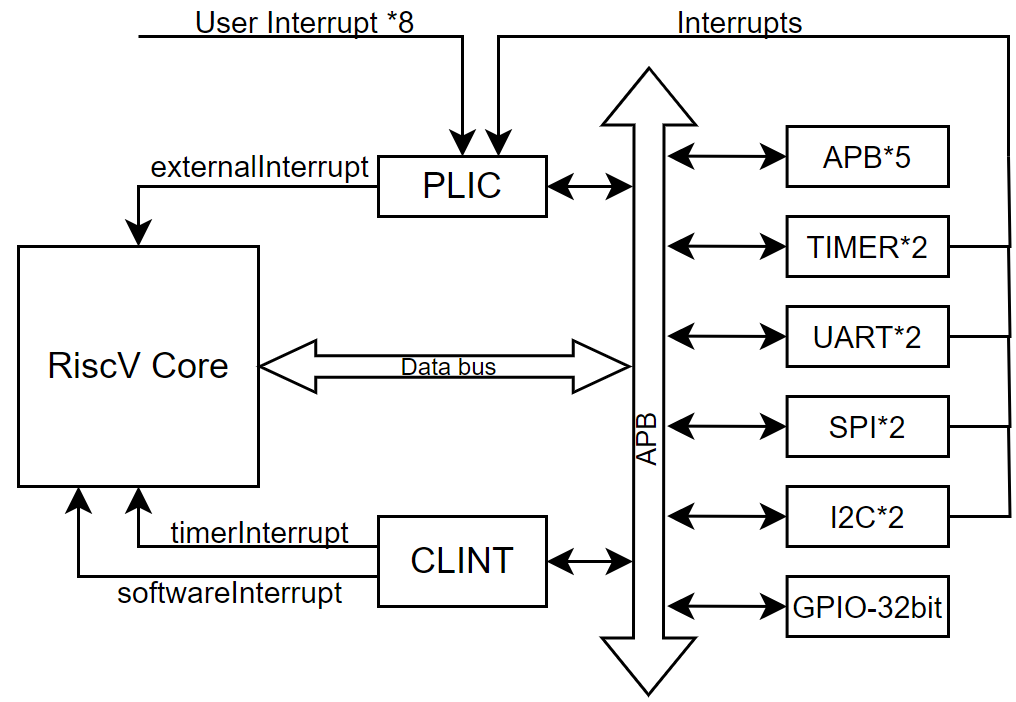

圖 2中斷管理圖

Tiny_SoC使用

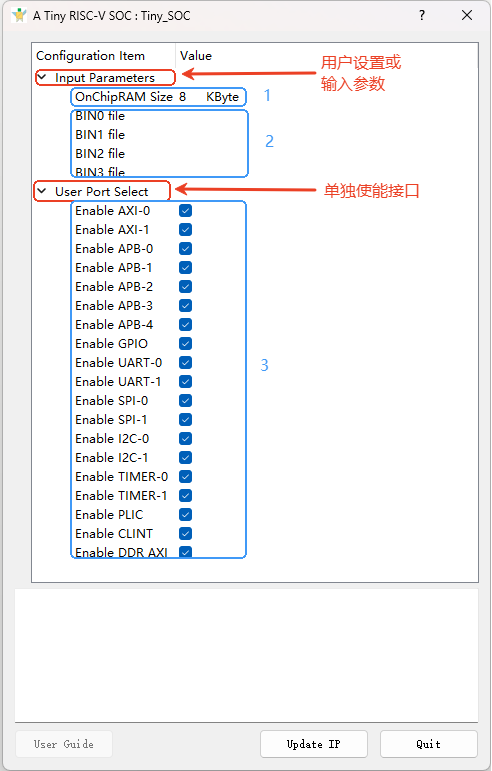

Tiny_SoC有極簡的使用界面,根據(jù)不同功能分為Input Parameters與User Port Select兩大類。

通過IP界面動(dòng)態(tài)選擇外設(shè)模塊(UART/SPI/I2C等),設(shè)置片上RAM大小(4KB~512KB),導(dǎo)入預(yù)編譯程序文件(BIN格式),5分鐘完成核心配置。

圖 3IP界面配置

典型應(yīng)用場景

工業(yè)控制:多中斷響應(yīng)+高精度定時(shí)器,實(shí)現(xiàn)實(shí)時(shí)電機(jī)控制與傳感器數(shù)據(jù)處理。

工業(yè)相機(jī):高速接口+軟核控制器,實(shí)現(xiàn)高速數(shù)據(jù)處理與傳感器狀態(tài)監(jiān)控。

原型驗(yàn)證:靈活配置外設(shè)與接口,實(shí)現(xiàn)快速搭建RISC-V開發(fā)驗(yàn)證平臺。

獲取技術(shù)文檔與demo

技術(shù)文檔獲取:Tiny_SoC已發(fā)布,用戶可以在HQFPGA IP Manage中打開Tiny_SoC界面查看用戶指南,或訪問智多晶官網(wǎng)下載Tiny_SoC用戶指南。

設(shè)計(jì)參考案例獲取:請聯(lián)系FAE獲取參考設(shè)計(jì)案例,或在公眾號中與我們聯(lián)系。

-

處理器

+關(guān)注

關(guān)注

68文章

19833瀏覽量

233951 -

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615456 -

嵌入式

+關(guān)注

關(guān)注

5144文章

19575瀏覽量

315813 -

接口

+關(guān)注

關(guān)注

33文章

8968瀏覽量

153367 -

RISC-V

+關(guān)注

關(guān)注

46文章

2513瀏覽量

48413

原文標(biāo)題:智多晶Tiny_SoC | 輕量化RISC-V處理器核,開啟嵌入式開發(fā)新紀(jì)元

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

CAN協(xié)議特點(diǎn)簡介

SOC芯片供電系統(tǒng)簡介

TencentOS tiny的相關(guān)資料推薦

tencentos-tiny概述

中興微電子所SOC教程

Tiny Switch特性及其應(yīng)用

Windows CE簡介、特點(diǎn)及應(yīng)用

太陽能電池板單晶好還是多晶好,都有什么特點(diǎn)_太陽能板單晶和多晶區(qū)別在哪里

如何使用Zynq SoC硬件加速實(shí)現(xiàn)改進(jìn)TINY YOLO實(shí)時(shí)車輛檢測的算法

STM32開發(fā),體驗(yàn)騰訊RTOS-tencentos-tiny

多晶粒SoC成趨勢,UCIe標(biāo)準(zhǔn)助其一臂之力

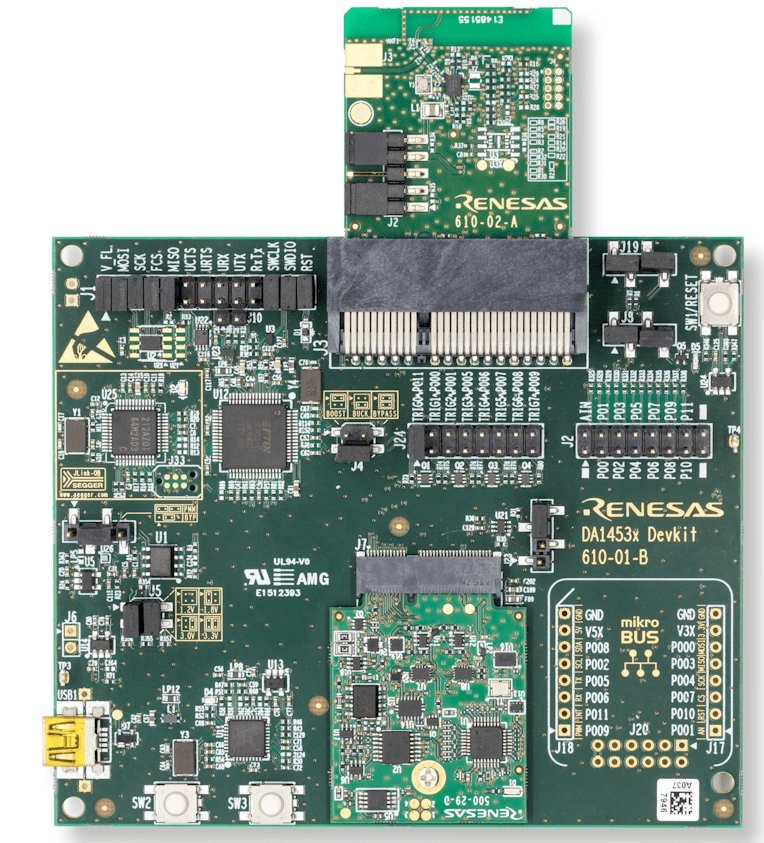

DA14535 SmartBond TINY? SoC開發(fā)套件數(shù)據(jù)手冊

智多晶Tiny_SoC簡介和特點(diǎn)

智多晶Tiny_SoC簡介和特點(diǎn)

評論